# Programmable Logic Design – I

#### Introduction

In labs 11 and 12 you built simple logic circuits on breadboards using TTL logic circuits on 7400 series chips. This process is simple and easy for small circuits. With increasing complexity of the logic circuitry the possibility of wiring errors grows and it becomes increasingly difficult to debug the circuit. Another problem is the difficulty in finding all the needed logic circuitry on available chips. To address these problems the electronics industry has developed the concepts of Programmable Logic Devices (PLD's) or Field Programmable Gate Arrays (FPGA's). The basic idea behind these devices is the notion that logic circuitry of arbitrary complexity can be constructed from simple gates connected with appropriate links and the technical advance that has made this possible is the development of large gate arrays with computer programmable links. The design process then consists of specifying the logic design by means of a logic design language such as VHDL or by entering it on a schematic layout. A computer program then turns this design into a series of instructions that are downloaded into the chip to establish the desired logic circuitry. Facilities are provided to specify the pin out of the logic, to control placement of logic circuits on the chip and to impose timing constraints.

## **Design Tools**

For our designs we will be using the Xilinx Corporation (www.xilinx.com) ISE Foundation 9.2i. We will start by entering our design in the form of a circuit schematic but, in later stages of the labs we will use a high level language, VHDL, to benefit from its power and flexibility. In our designs we will sample only a few of the features and capabilities of this software package which is widely used in the electronics industry today.

#### Hardware

We will download our designs into a Digilab D2XL board connected to a Digilab Digital I/O board (DI01) shown in Figure 1 below. The FPGA chip on the D2XL board is a member of the Spartan II family, the XC2S30, with package type tq144, embodying 972 logic cells with a total of 30,000 gates. While this size of device was state-of-the-art a few years ago, rapid advances in technology have pushed the largest device sizes to many millions of gates.

The D2XL board's I/O resources are limited to a single pushbutton and one LED for use with a test program to verify proper operation. A large variety of I/O devices, however, are available on the DI01 board attached to theD2XL by means of two 40 pin connectors. Our two experiments will exploit the features of the D2XL/DI01 combination to design a number of circuits that will demonstrate the usefulness of this procedure.

## **Getting Started**

### **Hooking up the Hardware**

The circuitry is extremely delicate and can easily be destroyed if handled improperly. Static electricity which is easily generated is particularly dangerous and care must be taken to wear a grounded wrist strap when handling the circuitry. Your instructor will show you how to use it properly. Your two boards should be connected to one another, with power cord installed and a programming cable from the parallel port of the PC to the JTAG connector of the D2XL attached. Ask your instructor for help if this is not the case.

Figure 1: The D2XL and DI01 boards with programming cable attached.

#### **Testing the D2XL board**

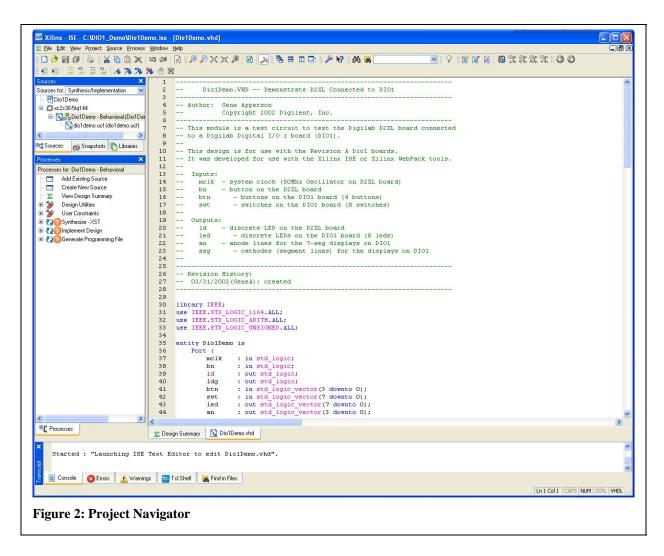

You should have a Xilinx ISE 9.2i icon on your screen. Double click on it to open the program. As a first program to download we want to use "Di01Demo" (C:/Digilent/Di01Demo.ise) to test the integrity of the D2XL board and the attached Digital I/O 1 board. If another project comes up, close it from the "File" menu and use "Open Project"

from the same menu to open "Di01Demo". If you are successful you should get a screen display like Figure 2.

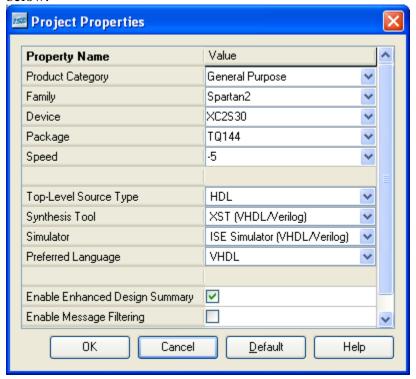

You need to double-click on the 3<sup>rd</sup> line in the top left window to get the display in the top right window. These four windows represent the design environment for the project with "Sources" in the top left window, the "Processes" for a given Source below it, the contents of selected files in the right hand window and text files below. On top of the "Sources" window is a tab to select the type of sources to be displayed. In this instance the sources are those associated with "Synthesis/Implementation" but we will also be interested with sources for "Behavioral Simulation". Before proceeding we need to check that we have selected the proper chip and simulation software. If you right-click the

xc2s30-tq144 icon and select "Properties" you should pop a window such as shown below:

**Figure 3: Project Properties**

Check that the Device and Package types are correctly selected and under "Simulator" choose "ISE Simulator (VHDL/Verilog)" and "VHDL" for Preferred Language. When you have satisfied yourself, close the window.

Extensive help files are available online and at this time it would be a good idea to go to the "Help" window, select "Help Topics, FPGA Design, FPGA Design Flows" and read the chapter "FPGA Design Flow Overview".

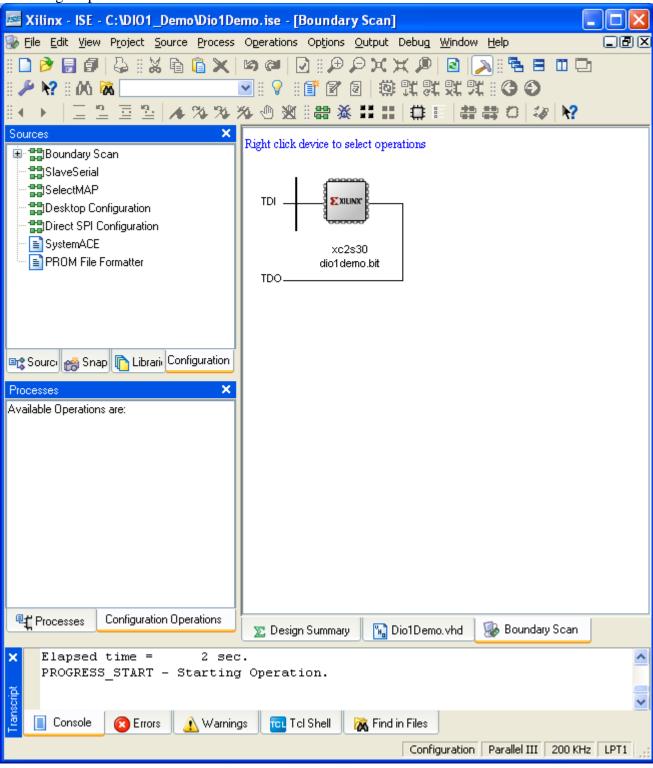

To test our board we are going to select the "Synthesis/Implementation" sources, select "Di01Demo-Behavioral" and in the "Processes" window expand the "Generate Programming File" and then double-click on "Configure Device (iMPACT). Doing this puts the program through all of the necessary steps to generate the file for downloading to the FPGA and to initiate the downloading process. When asked, choose the Configure devices using Boundary Scan bullet and select "Automatically connect a cable and identify a Boundary Scan chain". You will be asked to assign a new configuration file, choose "dio1demo.bit". This will happen, of course, only if there are no errors in any of the intervening steps. If all goes well you should wind up with a page such as Figure 4. Click on the boundary scan tab at the bottom of the window. Following instructions, right-click on the device and select "Program". This will bring up the programming window where you simply click "Ok". If there are no problems success will be signaled by a "Program Succeeded" announcement. At this time the 7-segment display should be cycling through the numbers 0 to 9, the slide switches should control their corresponding LED's and depressing the push buttons should interrupt the display on the 7-segment chip opposite the button. Also, the push button on the D2XL card, when depressed,

should light up the LED "LD1".

Figure 4: Programming page

If this is so, then the D2XL board and the DI/O1 board are in proper working order and we can go on to our first project.

## Important Xilinx design notes:

- 1. Create your own directory right off of the root directory c:\. All of your work must be saved in this directory or in its subdirectories.

- 2. Your directory and subdirectories <u>CANNOT</u> contain any spaces.

- 3. <u>DO NOT</u> name any of your projects or design elements any reserved logical names such as, AND, OR, COUNTER, BUS, etc ...

- 4. If you ignore any of these three notes, your project will not work. You will have to start the project over from the beginning. Depending on the project this could cost you a considerable amount of time. In addition, if one of your projects fails for one of these three reasons points will be deducted from your lab score.

- 5. If implementing your design to your D2XL and D101 boars does not work, try restarting the board by disconnecting it from the power supply.

### Design Project I

For our first project we will use "Schematic Entry" to design a circuit with a single AND gate. We will use "ISE Simulator" to test its proper operation, attach push buttons to the two inputs and an LED to the output, download it into the FPGA and test its operation.

## Schematic Entry

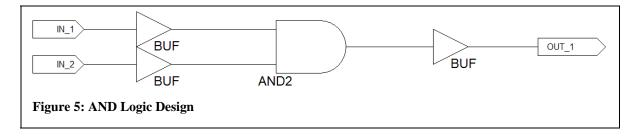

Go to the "Help" window, select "Help Topics" and then read the chapter FPGA Design/Design Entry/Schematics. Close the current project and do not save the configuration file. Select "File" "New Project" to get to the Project Wizard. Choose a Project Name, Project Location on "C" disk and Schematic for Top-Level Source Type. Check that the appropriate hardware is selected and that "ISE Simulator" is chosen. Do not create a new source nor add an old one at this time but continue until the process finishes displays the Design Environment again. Select "Synthesis/Implementation" tab; click on your device name and in the "Processes" window "Create New Source". From the choices given select "Schematic" and give it a name of your choosing When the Wizard finishes, a schematic entry window is created. Click on the "Symbols" tab, choose "Logic" from the categories in the sources window. (If your sources window is too small and you cannot get the symbols or categories scroll bars to work, increase the length of the sources window.) Select "and2" under symbols and place it in the schematic entry window. You may wish to magnify the drawing for better viewing. Next add input and output buffers to the two inputs and one output using the "buf" symbol. You will need the wiring tool to make the connections. Each input needs an input marker and the output needs an output marker which can be generated by clicking on the I/O Marker icon. Edit the default names to change them to IN\_1, IN\_2 and OUT\_1 respectively. Save your design and go to "Tools" "Check Schematic" to verify your design. If there are no errors you can go on to the next step. Your design should look like Figure 5.

### **Modeling the Design**

Figure 6: Timing choices for ISE simulator

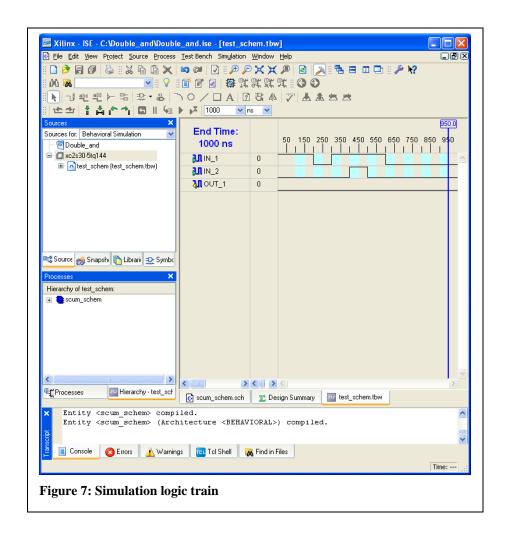

We must now model the design to see that it satisfies our design goals. Select the "Behavioral Simulation" tab for "Sources", click on the .sch file and in "Processes" create "New Source", "Test-bench Waveform" and give it some appropriate name. In the "Timing Window" of Figure 6 select "Combinatorial" for the clocks and leave everything else as it is. The next window, shown in Figure 7, gives you the opportunity of setting a train of input pulses to test your logic design. Note that the two inputs should be chosen

to represent all possibilities for the circuit. Save your file and go back to the Sources window with the "Behavioral Simulation" tab depressed.

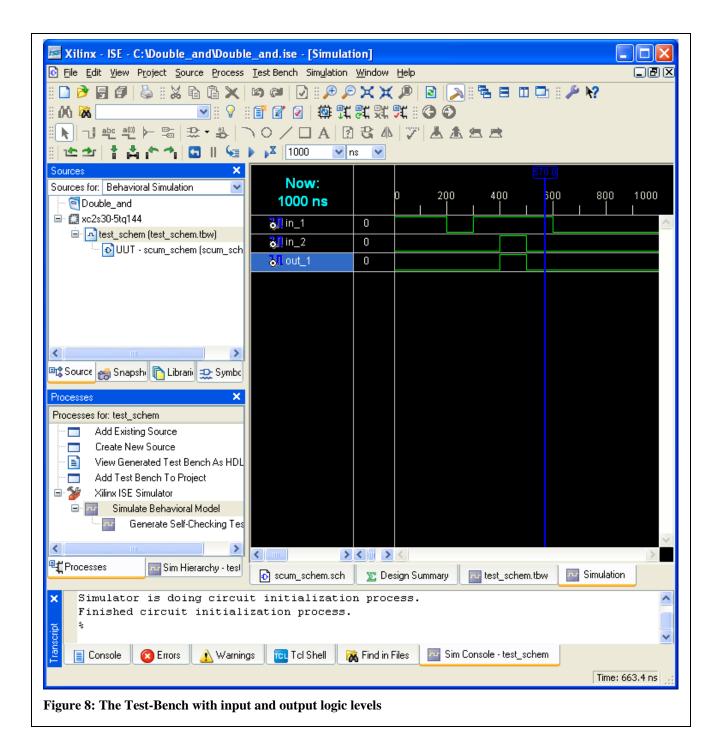

Under processes select "Xilinx ISESimulator", double click on "Simulate Behavioral Model" and you should be rewarded with Figure 8. Check it over to assure yourself that the simulation represents what you expect from your circuit.

# **Assigning Pins**

Next we must assign pins to our device. Checking the DI01 Manual we note on p.2 that the eight LED drive signals are active high. Thus we will attach the output of our AND to the drive signal of LED 1. On p. 4 we note that activating a pushbutton connects its output to Vdd or logic high. Thus we will want to tie our inputs to the outputs of pushbuttons 1 and 2. Next we check the DI01/D2XL pin correspondence chart and note that LD1 is connected to FPGA pin 93 and that BTN1 and BTN2 are connected to pins

84 and 85. Select the .sch file in the "Sources" window with tab set to "Synthesis/Implementation" and double click on "Assign Package Pins" in the "Processes" window under "User Constraints". Answer "Yes" that you do want to create an .ucf file. In the .ucf file enter p84, p85 and p93 in the "Loc" column for I/O components "In\_1", "In\_2" and "Out\_1" respectively and then save the file choosing "Synplify Verilog Default: []" as the bus delimiter.

#### Implementing the Design

Select the .sch file in the "Sources" window and double click "Configure Device [iMPACT]" to generate the appropriate files and download them to the FPGA. Follow the same steps you did in the initial tests of the boards. Ignore any warnings about clocks. You should once again see "Programming Succeeded" as the indication that no errors were found in your design and that the download was successfully accomplished.

#### Testing the Design

Manually verify that BTN1 and BTN2 are inputs to an AND circuit whose result is displayed in LD1.

### Design Project II

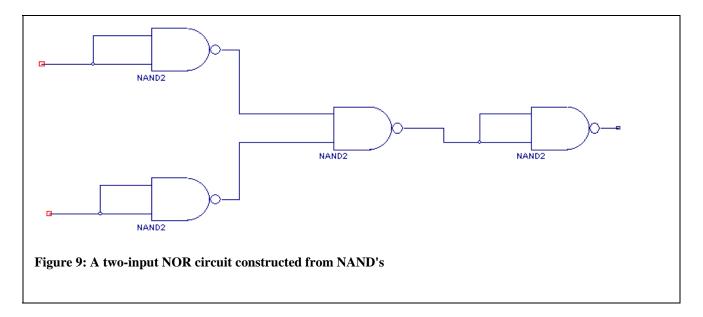

Following the procedure above implement, simulate, download and test the circuit

in Figure 9 which creates a NOR gate from 4 NAND's. Finish the circuit by adding input and output (I/O) buffers and giving appropriate labels to the I/O lines. You can once again use BTN1 and BTN2 for inputs and LD1 for the output. Verify that the truth table for a two-input NOR gate is satisfied.

## Design Project III

One of the huge advantages of this form of design is that macros of arbitrary complexity can be constructed, stored and reused in future designs. Our collection of

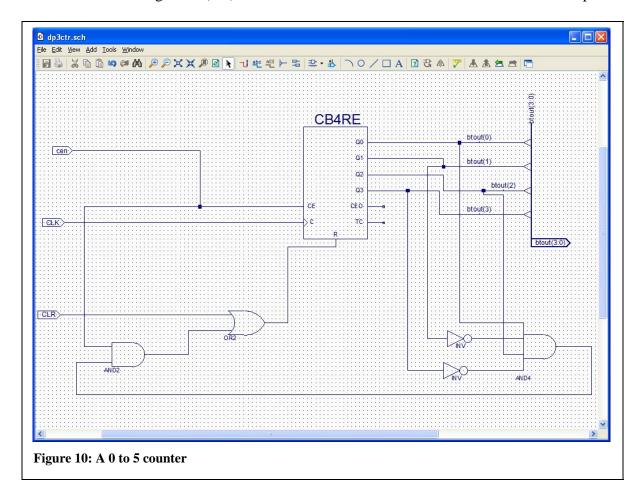

symbols contains many such macros. For our next design we will use one of them, CB4RE, a 4 Bit Cascadable Binary Counter with Clock Enable and Synchronous Clear, to construct a counter that will count from 0 to 5, reset and continue. We will then save it as a new macro to be used in our next experiment. The design in Figure 10 is an implementation of such a counter.

Write down a truth table for this counter using values for the clock (clk), counter enable (cen), clear (clr) and sufficient number of clock cycles to show the full, repetitive operation of the counter. What is meant by "synchronous clear"? You may wish to consult the "Symbol Info" tab for the CB4RE counter.

A new wrinkle in this design is the presence of a bus which is a collection of individual signals. It is automatically created when a wire, drawn with the wiring tool, is labeled as a vector e.g. btout(3:0). Individual elements of the bus are selected via bus taps

with their names specified by using the netname tool. In our case these names are btout(0) to btout(3). Create the schematic entry in Figure 10; check for errors and save the file. The device that we wish to build will have 3 inputs, ce for Clock Enable, clr for Clear and clk for Clock. Outputs will consist of a bus 4 bits wide, btout(3:0). Start a new project with schematic entry at the highest level. Enter your design in the usual fashion naming the inputs ce, clk and clr. To generate a bus for output draw a line using the wiring tool and give it a name btout(3:0). The program will change the line into a thicker,

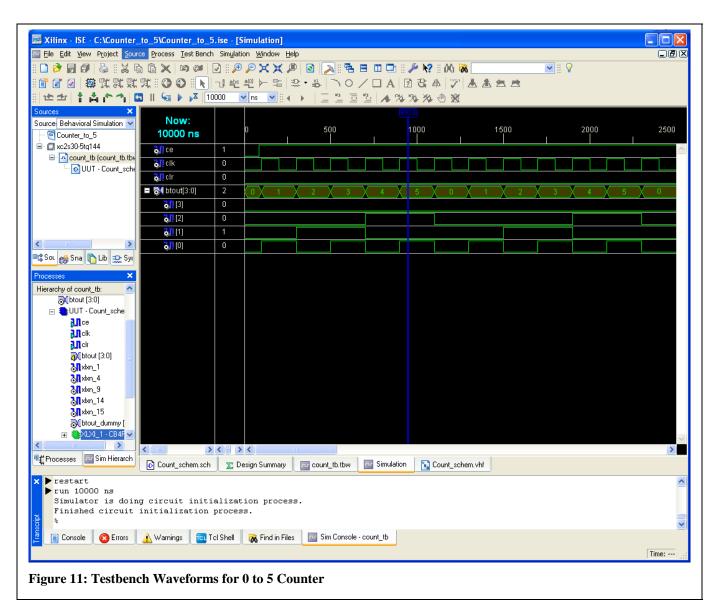

bus, line in correspondence with the name. Attach the bus taps as indicated and name them btout(0) to btout(3) using the "add net name" tool. Be sure to save the design and check for errors. If none are found go back to "Project" and create a new source of type "Testbench Waveform" using a single clock. Provide changes in the logic states of "ce" and "clr" to fully test your design. Save this file and go to "Simulate Behavioral Model". Verify that your logic is working properly by examining the outputs on the "Wave" plot below (Figure 11). Note that the "btout" bus is given numerically after each clock transition and can be expanded to look at the individual bit states as well. Does the output agree with your Truth Table?

Next select your .sch file in "Sources" and double click "Create Schematic Symbol" in "Processes". In your schematic entry page verify that the new symbol is available for use.

### Design Project IV

Today's lab is the introductory part of a two lab series that will result in the construction of a counter to count from 0 to 60 with the counts displayed on our 7-segment displays. If you have arrived this far with time remaining you may wish to continue with next week's lab and construct the 0 to 60 counter that is at the heart of our stopwatch design.