#### **Preliminary**

## InterBOARD<sup>™</sup> 75 Gbps SNAP 12 Parallel Fiber Optic Transmitter and Receiver Board Edge Modules

### SN-T12-C01001 SNAP 12 Transmitter SN-R12-C01001 SNAP 12 Receiver

Ideal for Board Edge Mounting

#### **Product Summary:**

The SNAP12 Transmitter and Receiver modules enable high performance multi-channel optical links designed for very short reach (VSR) high-speed data communication and computing applications where bandwidth bottlenecks are incumbent. In terms of Gbps, they offer the lowest cost solution and the highest packaging density. Consisting of 12 independent optical channels, each capable of transmitting 6.25 Gbps up to 300m on 50 micron multimode optical fiber, these modules have an aggregate link bandwidth in excess of 75 Gbps and operate at a wavelength of 850nm. They are optimized for applications which require line rates of 5.0 or 6.25 Gbps.

The Transmitter and Receiver modules have been designed to meet the harshest external operating conditions including temperature, humidity and EMI interference using Reflex Photonics next generation,  $LightABLE^{TM}$  packaging technology. This unique technology also is expected to enable the modules to meet the most stringent Telcordia and Mil standard specifications. The modules offer very high functionality and feature integration, accessible via a two-wire serial interface.

#### **Key Benefits:**

- SNAP 12 "Snap On" Pluggable for direct field replacements

- Highest package density per Gbps

- · Lowest profile form factor

- Low power consumption

- Easy system design

- Extended high reliability via advanced LightABLE™ technology

#### **Specifications and Features Highlights:**

- 12 independent parallel optical channels

- Channel Data rate of up to 6.25 Gbps

- Aggregate Data rate in excess of 75 Gbps (over 12 channels) per module

- 850-nm VCSEL/PD array technology

- CML/LVDS/PECL compatible electrical I/O

- Individually addressable channels

- Individual channel fault monitoring

- 62.5µm and 50µm multimode fiber supported

- Single 3.3V power supply

- Drop in compatible with SNAP 12 MSA via MEG-Array® connector

- Protocol Agnostic

#### **Applications:**

- Very high speed datacom and telecom VSR links:

- Board to board interconnect

- Rack to rack interconnect

- System to system interconnect

- Server farms and mass storage interconnects

- 12 channels of high speed serial data streams:

- Infiniband™ 12x

- SONET/SDH (OC-16 and OC-48)

- Multi-Lane PCI Express

- Gigabit Ethernet

- RXAUI 6.25 Gbps

- Fibre Channel (1/2/4 Gbps)

- OIF-VSR5-01 (Very Short Reach OC-768)

- Massively parallel/super computing systems

#### 1. Transmitter and Receiver Overview

Reflex Photonics transmitter and receiver modules offer twelve asynchronous channels operating at up to 6.25-Gbps per channel. These modules are designed for very short reach application (1m to 300m) with support for both 62.5/125 micron and 50/125 micron multimode fiber.

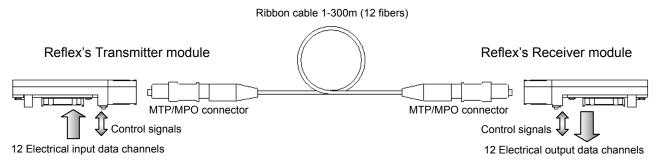

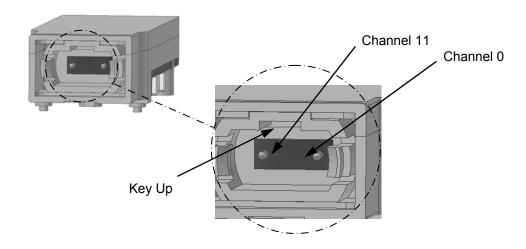

As shown in Figure 1, a complete 12 channel parallel point-to-point optical link consists of a transmitter module, a 12-fiber optical ribbon cable, and a receiver module. The transmitter module consists of an array of 12 VCSELs (Vertical Cavity Surface Emitting Lasers) and associated circuitry, which converts 12 parallel electrical data inputs to 12 parallel optical data output signals. Conversely, the receiver module inputs 12 parallel optical signals and converts them into 12 parallel electrical signals through an array of 12 PIN photodiodes and associated circuitry.

Figure 1. Complete point-to-point 12 channel parallel optical link.

The optical fiber ribbon cable has an MPO/MTP<sup>TM</sup> connector at each end, which plugs into the Transmitter and Receiver module receptacle. The orientation of the ribbon cable is "keyed" and guide pins are present inside the module receptacle to ensure proper alignment. The cable usually has 180 degree twist (key up to key down) to ensure proper channel to channel alignment. Electrical connection is achieved though a vertically pluggable 10X10 Meg-Array® connector.

Figure 2 illustrates a typical board edge implementation of a Transmitter and Receiver pair. The modules operate from a single +3.3V power supply and LVCMOS/LVTTL global control signals such as fault/signal detection, reset, enable and disable are available with the modules. A 2-wire serial interface is available to send and receive more complex control signals and to obtain digital diagnostic information. Individual channels can be addressed and unused channels can be shutdown for maximum design flexibility.

Each parallel module is supplied with a receptacle process plug for the protection of the optics and a process plug for the pin protection of the electrical 10 X 10 Meg-Array® BGA connector. The transmitter module is Class 1 eye safe by design. Please refer to the regulatory compliance section for further details.

These modules are channel compliant with the IEEE 802.3z 1000Base-SX standard for Gigabit Ethernet. Therefore, they can be used in conjunction with an optical fiber fan-out to connect to single channel transceivers such as 850nm small form factor modules.

Figure 2. Board-edge application example.

#### 2. Absolute Maximum Ratings

Absolute maximum ratings indicate values beyond which damage may occur.

Table 1. Absolute maximum ratings for Transmitter and Receiver

| Parameter                    | Symbol             | Min. | Max.    | Unit | Remarks |

|------------------------------|--------------------|------|---------|------|---------|

| Storage Temperature          | T <sub>ST</sub>    | -25  | 100     | °C   |         |

| Operating Case Temperature   | Tc                 | 0    | 90      | °C   | 1.      |

| Supply Voltage               | Vcc                | -0.5 | 4       | V    |         |

| Differential Input Voltage   | V <sub>ID</sub>    |      | 2       | V    | 2.      |

| Peak Input Voltage           | $V_{PEAK}$         | -0.5 | Vcc+0.5 | V    |         |

| Output Short Circuit Current | I <sub>SHORT</sub> | -30  | 30      | mA   |         |

| ESD Resistance               | $V_{ESD}$          |      | +/- 1   | kV   |         |

| Relative Humidity            | RH                 | 5    | 95      | %    |         |

<sup>1.</sup> Case temperature is measured at the case on opposite side on the electrical connector.

#### 3. Recommended Operating Conditions

Recommended operating conditions indicate values at which performance and reliability is intended. Device functionality is not implied beyond the recommended operating conditions.

Table 2. Recommended operating conditions for Transmitter and Receiver

| Parameter                                  | Symbol           | Min.     | Max. | Unit       | Remarks |

|--------------------------------------------|------------------|----------|------|------------|---------|

| Supply Voltage                             | Vcc              | 3.1      | 3.5  | V          |         |

| Operating Case Temperature                 | Tc               | 0        | 75   | °C         | 1.      |

| Signaling Rate per Channel for Transmitter | $F_{TX}$         | 0        | 6.25 | Gbps       |         |

| Signaling Rate per Channel for Receiver    | $F_{RX}$         | 0.000175 | 6.25 | Gbps       |         |

| Differential Input Voltage Swing           | $\Delta V_{p-p}$ | 175      | 1200 | mV         |         |

| Power Supply Noise                         | $V_N$            |          | 200  | $mV_{p-p}$ |         |

1. Case temperature is measured on the case on opposite side on the electrical connector.

<sup>2.</sup> Maximum voltage that can be applied across the differential data inputs without damaging the device.

#### 4. Transmitter Specifications

#### 4.1 Transmitter Functional Description

The transmitter module converts parallel electrical input signals via a laser driver and a Vertical Cavity Surface Emitting Laser (VCSEL) array into parallel optical output signals. The transmitter module accepts electrical input signals which are voltage compatible with both Low Voltage Positive Emitter Coupled Logic (LVPECL) and Current Mode Logic (CML) levels. All input data signals are differential and are internally terminated. The transmitter supports a data rate up to 6.25 Gbps for each channel. With a DC coupled configuration the transmitter module's minimum data rate is DC otherwise bound by the selection of the AC coupling capacitors.

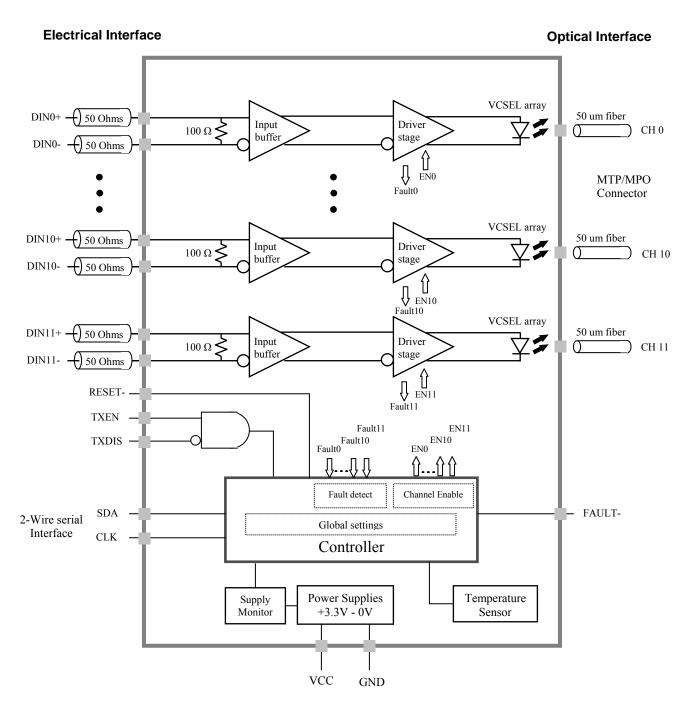

Figure 3, presents a detailed functional block diagram of the transmitter module with corresponding external connection pins. Inside the transmitter module, a control block provides, through individual channel settings, proper laser drive parameter, such as modulation and biasing and ensures proper operation of the device.

A single power supply, Vcc, is required to power up the module. The module offers 4 global control signals, TXEN (Transmitter Enable), TXDIS (Transmitter Disable), RESET- and FAULT-. A two-wire serial interface is also available to communicate with the controller through two control pins: CLK (Clock) and SDA (Serial Data). All control signals are LVCMOS (Low Voltage Complementary Metal Oxide Semiconductor) compatible.

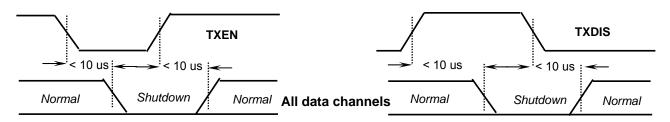

TXEN and TXDIS are complementary signals used to shutdown and enable the transmitter. For the transmitter optical output to be operational TXEN must be held to a logical High and TXDIS must be held at a logical Low. If either is not properly set, the transmitter optical outputs will be disabled. TXDIS is internally pulled and may be left unconnected; however TXEN must be connected and properly set for the transmitter to be functional.

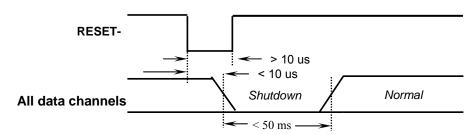

A logical Low at the FAULT- pin indicates a problem with transmitter. A fault condition may arise from two reasons; either a VCSEL is operating improperly or the circuitry senses a short/open condition. When a fault is detected at a VCSEL the faulty channel is automatically powered down and the FAULT- signal will remain active (Low) until the RESET- switch is toggled. A logic Low level at RESET- also switches all laser outputs to an off state. During power-up RESET- can be used as a power-on reset switch, which disables drive and control circuitry until the power supply has reached a 3.135 V level.

#### 4.2 Transmitter functional block diagram

Figure 3. Reflex transmitter functional block diagram.

#### 4.3 Transmitter Pin Description and Assignment

Table 3, Transmitter Pin Description

| ,          |             |        |                                                                                                                                       |

|------------|-------------|--------|---------------------------------------------------------------------------------------------------------------------------------------|

| Symbol     | Туре        | I/O    | Description                                                                                                                           |

| DIN+[0:11] | CML/LVPECL  | Input  | Input Non-Inverting Data, internal differential termination at 100 Ohms                                                               |

| DIN-[0:11] | CML/ LVPECL | Input  | Input Inverting Data, internal differential termination at 100 Ohms                                                                   |

| VCC        | Supply      | Input  | +3.3 V Transmitter Voltage Supply                                                                                                     |

| GND        | Supply      | Input  | Transmitter Ground, connected to signal ground plane                                                                                  |

| FAULT-     | CMOS        | Output | Transmitter Fault indicator, Logic Low indicates fault                                                                                |

| TXEN       | CMOS        | Input  | Transmitter enable, internal pull-up, High: normal operation, Low: transmitter disable                                                |

| TXDIS      | CMOS        | Input  | Transmitter disable, internal pull-down, Low: normal operation, High: transmitter disable                                             |

| RESET-     | CMOS        | Input  | Transmitter reset, internal pull-up, Logic Low: reset transmitter, Logical High: normal operations. Also used to clear FAULT- signal. |

| SDA        | CMOS        | In/Out | Serial data Input and Output for 2-wire interface                                                                                     |

| CLK        | CMOS        | Input  | Clock for 2-wire interface                                                                                                            |

| DNC        |             |        | Do Not Connect                                                                                                                        |

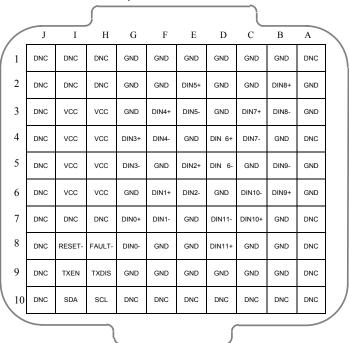

#### Towards optical MTP/MPO connector

Figure 4, Transmitter pin assignment - top view of printed circuit board layout (customer side) for  $10X10~\text{Meg-Array}^{\circledR}$  connector.

#### 4.4. Transmitter Characteristics

Table 4, Transmitter Optical Specifications (Room T = 25°C, VCC = 3.3V +/- 5%)

| Parameter                                      | Symbol           | Min. | Тур. | Max. | Unit  | Remarks       |

|------------------------------------------------|------------------|------|------|------|-------|---------------|

| Optical Rise/Fall Time                         | $T_R/T_F$        |      | 40   | 80   | ps    | 1.            |

| Average Optical Power (per channel)            | P <sub>OUT</sub> | -8   | -2.5 | -2   | dBm   | 2. 3.         |

| Average Optical Power (per channel) – Disabled | P <sub>OFF</sub> |      |      | -30  | dBm   |               |

| Launched Power (per channel)                   | PL               | -9   | -3   | -2.2 | dBm   | 4.            |

| Extinction Ratio                               | ER               | 6    | 7    |      | dB    | 5.            |

| Center Wavelength                              | $\lambda_{C}$    | 840  | 850  | 860  | nm    |               |

| RMS Spectral Width                             | λ                |      | 0.5  |      | nm    |               |

| Deterministic Jitter                           | DJ               |      |      | TBD  | ps    | K28.5 Pattern |

| Total Jitter                                   | TJ               |      |      | TBD  | ps    |               |

| Relative Intensity Noise                       | RIN              |      |      | -120 | dB/Hz |               |

- Measured at 20% to 80% levels using 550 Mb/s clock signal.

- 2.

- Measured at the output of the modules optical interface.

If using DC coupling, data must remain DC balanced otherwise rated optical power may be exceeded. 3.

- Optical power measured at the output of 1m 50/125 um breakout cable.

- Measured 550 Mb/s with a  $2^7 1$  encoded pattern.

Table 5, Transmitter Electrical Specifications (Room T = 25°C, VCC =3.3V +/- 5%)

| Parameter                    | Symbol           | Min. | Тур. | Max. | Unit      | Remarks |

|------------------------------|------------------|------|------|------|-----------|---------|

| Power Dissipation            | P <sub>DIS</sub> |      | 1.0  | 1.3  | W         |         |

| Supply Current               | I <sub>CC</sub>  |      | 310  | 395  | mA        |         |

| Differential Input Impedance | $Z_{\text{IN}}$  |      | 100  | 110  | Ω         | 1.      |

| Differential Input Voltage   | $V_D$            | 0.2  |      | 2    | $V_{p-p}$ |         |

| Inter-Channel Skew           | $T_{SK}$         |      |      | 150  | ps        | 2.      |

| Control I/O Voltage, High    | $V_{IH}$         | 1.1  |      | VCC  | V         |         |

| Control I/O Voltage, Low     | $V_{IL}$         | 0    |      | 0.7  | V         |         |

| FAULT- Assert time           |                  |      |      | 100  | us        | 3.      |

| RESET- Duration              |                  | 10   |      |      | us        | 3.      |

| RESET De-assert time         |                  |      |      | 100  | ms        | 3.      |

| TXEN Assert time             |                  |      |      | 1    | ms        | 3.      |

| TXDIS Assert time            |                  |      |      | 1    | ms        | 3.      |

| Power on time                |                  |      |      | 100  | ms        | 3.      |

Differential input impedance measure between DIN- and DIN+.

Defined as the difference in times of flight between the "slowest" channel (i.e. the channel having the longest effective time of flight), and the "fastest" 2. channel (i.e., the channel having the shortest time of flight). See figures 5,6,7 and 8 for timing diagrams.

# 4.5 Timing Diagrams VCC All data channels Shutdown Normal

Figure 5, Typical transmitter power-up sequence.

Figure 6, TXEN and TXDIS timing diagram.

Figure 7, RESET Timing diagram.

Figure 8, Reset timing diagram. The transmitter is reset to clear a fault. If the fault persists the FAULT- signal will remain active. Note that the RESET- signal must be held low for a minimum of 10 us.

#### 5. Receiver Specifications

#### 5.1 Receiver Functional Description

The receiver module converts parallel optical input signals via a receiver and a photodetector array into parallel electrical output signals. The receiver module outputs electrical signals, which are voltage compatible with Current Mode Logic (CML) levels. All output data signals are differential and support a data rate up to 6.25 Gbps for each channel.

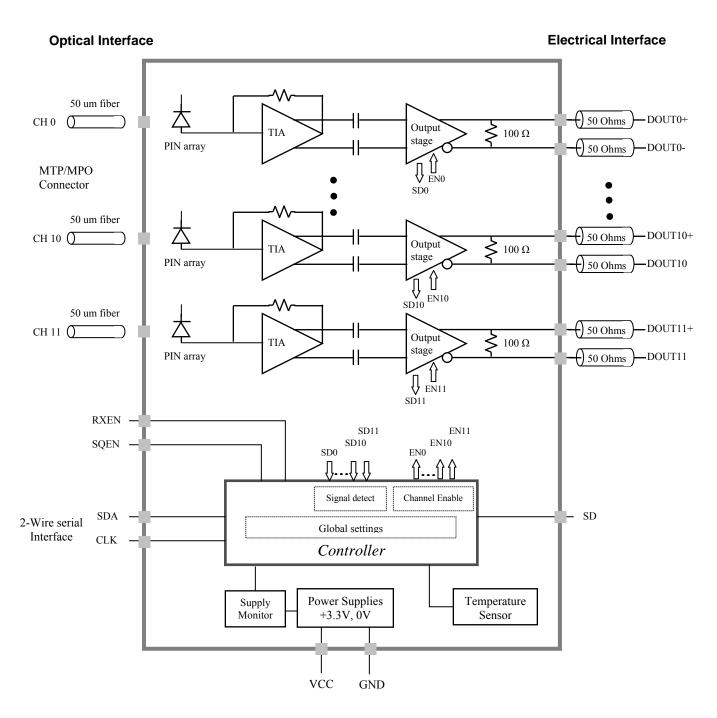

Figure 9, presents a detailed functional block diagram of the receiver module with corresponding external connection pins. Inside the receiver module, a control block ensures proper operation of the device and provides individual channel settings and monitoring.

A single power supply, VCC, is required to power up the module. The module offers 3 global control signals, RXEN (Receiver Enable), SQEN (Squelch Enable) and SD (Signal Detect). A two-wire serial interface is also available to communicate with the controller through two control pins: CLK (Clock) and SDA (Serial Data). All control signals are LVCMOS compatible.

RXEN is used to enable the receiver. RXEN is internally pulled-up and may be left unconnected in order for the receiver to be operational. RXEN must be set to a logical Low for the electrical outputs to be shutdown. SD is used to indicate the presence of sufficient optical power on all the channels. A Low output on SD indicates a loss of signal i.e. the presence of at least one data channel without sufficient optical power. SQEN is used to drive electrical data output to a logic zero on any channel that has a loss of signal; this feature is disabled when SQEN is set to Low.

#### 5.2 Detailed Receiver Block Diagram

Figure 9, Receiver block diagram.

#### 5.3 Pin Description and Assignment for Receiver

Table 6, Receiver pin description

| ,           |        |        |                                                                                                            |

|-------------|--------|--------|------------------------------------------------------------------------------------------------------------|

| Symbol      | Туре   | I/O    | Description                                                                                                |

| DOUT+[0:11] | CML    | Output | Non-Inverting Data output, internal differential termination at 100 Ohms                                   |

| DOUT-[0:11] | CML    | Output | Inverting Data output, internal differential termination at 100 Ohms                                       |

| vcc         | Supply | Input  | +3.3 V Voltage supply for receiver                                                                         |

| GND         | Supply | Input  | Receiver Ground, connect to signal ground plane                                                            |

| VPP         | Supply | Input  | Not internally connected (Power supply pin for MSA CML DC-coupling)                                        |

| RXEN        | CMOS   | Input  | Receiver output enable, internal pull-up, High: normal operation, Low: receiver disable                    |

| ENSD        | CMOS   | Input  | Enable signal detect, internal pull-up, High: normal operation, Low: signal detect output(s) forced active |

| SD          | CMOS   | Output | Global signal detect; High: normal operation; Low: inadequate power on at least one channel                |

| SQEN        | CMOS   | Input  | Squelch enable; asserted High                                                                              |

| SDA         | CMOS   | In/Out | Serial data input/output for 2-wire interface                                                              |

| CLK         | CMOS   | Input  | Clock for 2-wire interface                                                                                 |

| DNC         |        |        | Do not connect                                                                                             |

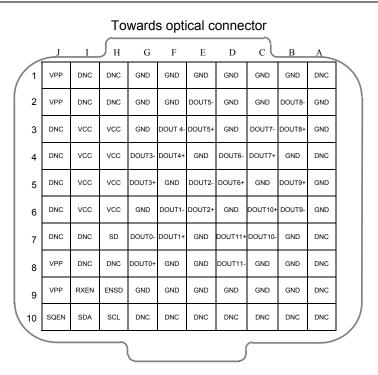

Figure 10, Receiver pin assignment - top view of printed circuit board layout (customer side) for  $10X10~\text{Meg-Array}^{\circledR}$  connector.

#### 5.4 Receiver Characteristics

Table 7, Receiver Optical Specifications (Room T = 25°C, VCC =3.3V +/- 5%)

| Parameter                               | Symbol               | Min. | Тур. | Max. | Unit | Remarks |

|-----------------------------------------|----------------------|------|------|------|------|---------|

| Optical Power Sensitivity (per channel) | P <sub>IN MIN</sub>  |      | -17  |      | dBm  | 1.      |

| Optical Power Saturation (per channel)  | P <sub>IN MAX</sub>  |      |      | -1.5 | dBm  |         |

| Stressed Receiver Sensitivity           | Ps                   |      |      |      | dBm  |         |

| Center Wavelength                       | $\lambda_{\text{C}}$ | 830  |      | 860  | nm   |         |

| Optical Return Loss                     | $R_L$                | 12   |      |      | dB   |         |

| Signal Detect Assert                    | T <sub>SDA</sub>     |      | 120  |      | us   |         |

| Signal Detect De-Assert                 | T <sub>SDD</sub>     |      | 150  |      | us   |         |

Defined as the average optical power necessary to produce a BER of 10<sup>-12</sup> at the center of the baud interval using a 6.25 Gbps PRBS of length 2<sup>23-1</sup> or equivalent. Input power is provided as an ideal source and all receiver channels are not under test are operating and receiving an optical signals.

Table 8, Receiver Electrical Specifications (Room T = 25°C, VCC =3.3V +/- 5%)

| Parameter                        | Symbol          | Min. | Тур. | Max. | Unit       | Remarks |

|----------------------------------|-----------------|------|------|------|------------|---------|

| Power Dissipation                | P <sub>D</sub>  |      | 1.65 | 1.9  | W          |         |

| Supply Current                   | Is              |      | 500  | 580  | mA         |         |

| Low frequency cut-off            |                 | 150  |      |      | Mb/s       |         |

| Electrical Rise / Fall Time      | $T_R/T_F$       |      | 60   |      | ps         | 1.      |

| Differential Output Impedance    | $Z_{\text{IN}}$ |      | 100  |      | Ω          |         |

| Differential Output Swing        | $V_D$           | 500  | 650  | 675  | $mV_{p-p}$ |         |

| Inter-Channel Skew               | $T_{SK}$        |      |      | 150  | ps         | 2.      |

| Data Output Deterministic Jitter | DJ              |      |      | TBD  | ps         |         |

| Data Output Total Jitter         |                 |      |      | TBD  | ps         |         |

| Control Input Voltage, High      | $V_{IH}$        | 1.1  |      | VCC  | V          |         |

| Control Input Voltage, Low       | $V_{IL}$        | 0    |      | 0.7  | V          |         |

<sup>1.</sup> Measured at 20% to 80% levels using 550 Mb/s clock signal.

<sup>2.</sup> Defined as the difference in times of flight between the "slowest" channel (i.e. the channel having the longest effective time of flight), and the "fastest" channel (i.e., the channel having the shortest time of flight).

#### 6. Mechanical and Layout Considerations

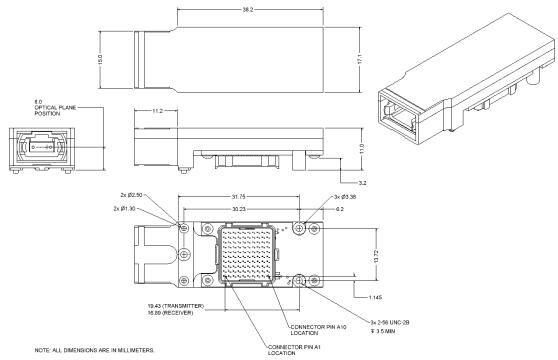

Figure 11a, Transmitter and Receiver mechanical outline, no heatsink

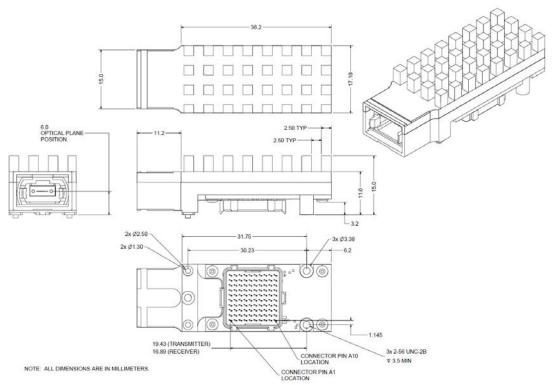

Figure 11b, Transmitter and Receiver mechanical outline, with heatsink

Figure 12, Transmitter and Receiver fiber channel assignment.

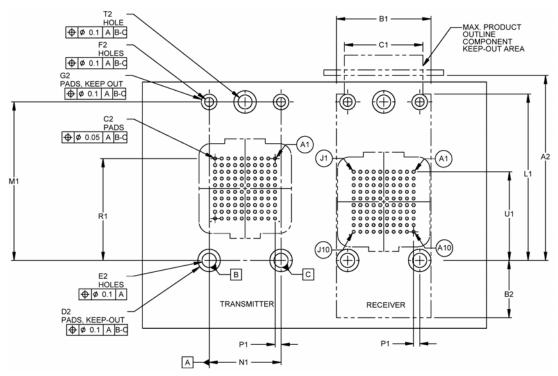

A typical host board mechanical layout for attaching the pluggable parallel optical transmitter and receiver modules is shown in Figure 13. The host electrical connector must be a 100-position FCI Meg Array<sup>®</sup> plug (FCI PN: 84512-101) or equivalent.

Host enclosures that use pluggable parallel optical modules should provide appropriate clearances between modules to allow insertion and extraction of the optical connector without the use of special tools. A recommended minimum center to center separation distance between modules is 18.42mm. Table 9 summarizes critical dimensions.

Figure 13, Host board mechanical layout.

For more information on this or other products:

Contact sales at (650) 967- 4416, or by email at <a href="mailto:sales@reflexphotonics.com">sales@reflexphotonics.com</a>

Page 14 July 2009 Doc # SN-970-020-00 Rev 2.0

| Key | Value (mm) | Tolerance (mm) | Comments                                                     |

|-----|------------|----------------|--------------------------------------------------------------|

| A2  | 35.31      | ±0.75          | Distance from rear post to inside surface of bezel           |

| B2  | 10.92      | MAX            | Distance from rear post to rear of module keep-out area      |

| C2  | Ø0.58      | ±0.05          | Diameter of pad in BGA pattern                               |

| D2  | Ø4.30      | MIN            | Diameter of keep-out pad for rear post                       |

| E2  | Ø2.69      | ±0.12          | Diameter of hole for mounting screws: two rear and one front |

| F2  | Ø1.70      | ±0.12          | Diameter of hole for front post                              |

| G2  | Ø3.00      | ±MIN           | Diameter of keep-out pad for front post                      |

#### 7. Compliance

Table 10, Regulatory Compliance Table

| Feature                                                     | Test Method                              | Comments                                                                                                                              |

|-------------------------------------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Laser Eye Safety                                            | IEC 60825-1 Amendment 2<br>CFR21 1040.10 | TUV Certificate number: N/A                                                                                                           |

| Electrostatic Discharge (ESD) to Case                       | IEC 61000-4-2                            |                                                                                                                                       |

| Electrostatic Discharge<br>(ESD) to Electrical<br>Connector | MIL-STD 883C; Method 2015.               | Class 42 ky)                                                                                                                          |

| Electromagnetic Interference (EMI)                          |                                          |                                                                                                                                       |

| Radiated Immunity                                           | IEC 6100-4-3 (TBD)                       | Field strength of 10V/m swept from 80 MHz to 1 GHz. No variation of Transmitter or Receiver performance detectable over those limits. |

| Component Recognition                                       | UL 1950<br>CSA C22.2 #950                | UL Certificate number: N/A<br>CSA Certificate number: N/A                                                                             |

DO NOT VIEW RADIATION DIRECTLY WITH OPTICAL INSTRUMENTS - CLASS 1M LASER PRODUCT

#### 8. Link distances and supported fiber types

Reflex Photonics Transmitter and Receiver modules support different link lengths depending on the fiber type used. The following table illustrates shows typical links distances with common multimode fiber types.

Table 11, Informative Link Reach

| Fiber Type and             | Max. Reach Distance |

|----------------------------|---------------------|

| Modal Bandwidth            | 6.25 Gbps           |

| 62.5/125 MMF<br>200 MHz·km | 35 m                |

| 50/125 MMF<br>500 MHz·km   | 100 m               |

| 50/125 MMF<br>2000 MHz·km  | 190 m               |

#### 9. Brief Application Information

#### 9.1 Handling and Cleaning

The MTP/MPO optical connector plug should be kept on during module manipulation to prevent physical damage or particle deposition on the end face. In case of contamination, clean the end face with linear motions using either a Kimwipe or a Q-Tip damped in 91% isopropyl alcohol. Forced nitrogen or clean dry air can also be used to remove particles or to remove lint residue after cleaning.

Always handle modules with care. To prevent damage to the electrical connector, only remove the plug before insertion. As shown in figure 14, align both connectors by using the receptacle keys. Push down on the rear of the module and then move forward to the front of the module. Like mating, the connector pair can be unmated by pulling them straight apart. However, it requires less effort to un-mate if the force is originated from one of the slot/key ends of the assembly. Mating or un-mating of the connector by rolling in a direction perpendicular to alignment slot/keys may cause damage to the terminal contacts and is must be avoided.

Figure 14, mating and un-mating procedure.

#### 9.2 ESD Discharge

The Transmitter and Receiver modules are shipped in Electrostatic Discharge ESD protective packaging, once removed normal handling precautions to prevent ESD are advised. They include grounding wrist straps, work benches and floor mats.

#### 9.3 Electrical Signals

Reflex Photonics Transmitter and Receiver use a differential CML circuit interface for their input or output stages which may require the user to properly design its interface. CML is a high-speed point-to-point interface and typically does not require any external termination resistors as it is provided internally by both the driver and the receiver devices. This greatly simplifies the system interconnect and stub lengths are minimized, thus signal quality is optimized. CML supports data rates above 10 Gbps depending upon the process for the drivers and receiver integrated circuit (IC).

CML maybe DC coupled or AC coupled if encoding is used. CML uses a passive pull up to the supply rail, which is typically 50 Ohms. Due to the fact that one side is pulled to the rail, both the driver and receiver should be powered from the same supply potential for DC coupled applications. This is one reason that AC coupling is popular with CML interfaces. It provides common-mode tolerance, fault protection and also supply independency. CML tends to be vendor specific, so a careful review of datasheets is recommended to determine inter-operation especially in DC coupled applications.

Printed circuit board transmission traces to and from the modules should be designed to have a differential impedance of 100 ohms. In order to preserve good signal quality, traces built on FR-4 printed circuit board material should be kept below 10 inches in length.

#### 9.4 Power Supply and Grounding

Power supply filtering is highly recommended for both the transmitter and receiver. A filtering network should be placed on the host printed circuit board as close a possible to the transmitter and receiver electrical connector for enhanced performance. It is recommended to put the filtering network on the opposite side of the PCB directly under the modules.

The case or chassis of the modules is isolated from the signal ground. It is recommended to tie the module case ground through the three mounting screws.

#### 9.5 Eye safety

The transmitter is a class 1M Laser Product per IEC/EN 60835-1 and should not be viewed directly with an optical instrument. Tampering or operating the product in a manner inconsistent with intended usage may result in hazardous radiation exposure.

#### 9.6 Evaluation Kit:

Transmitter and Receiver evaluation boards designed for high-speed testing are available. Each board is fitted with a 10x10 BGA electrical Meg-Array<sup>®</sup> connector socket where the module can be plugged. 24 SMA connectors provide the connections for the 12 differential electrical signals, which can be AC or DC coupled. The modules require a single 3.3V power supply.

The evaluation kit comes with a user manual to facilitate the evaluation process. In house application and design engineers are available to assist product evaluations and to support integration.

Page 17

#### 10. Ordering information

| Part Number            | Description                                                                                                                                                                                                              |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SN-T12-C01001-000-0-01 | 12 X 6.25 Gb/s 850 nm InterBoard™ SNAP 12 Transmitter Module for Board Edge Mounting Applications; The Transmitter module meets IEC 60825-1 Class 1M laser eye safety specifications. No heatsink.                       |

| SN-R12-C01001-000-0-01 | 12 X 6.25 Gb/s 850 nm InterBoard™ SNAP 12 Receiver Module for Board Edge Mounting Applications. No heatsink.                                                                                                             |

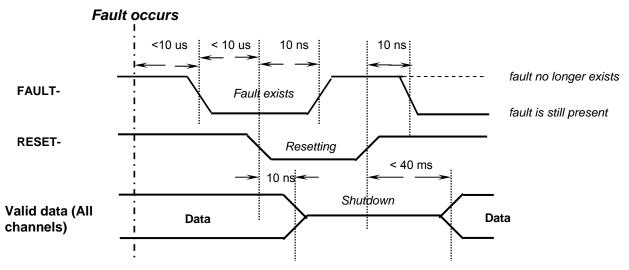

| SN-T12-C01001-000-0-02 | 12 X 6.25 Gb/s 850 nm InterBoard™ SNAP 12 Transmitter Module for Board Edge Mounting Applications; The Transmitter module meets IEC 60825-1 Class 1M laser eye safety specifications. With heatsink shown in Figure 11b. |

| SN-R12-C01001-000-0-02 | 12 X 6.25 Gb/s 850 nm InterBoard™ SNAP 12 Receiver Module for Board Edge Mounting Applications. With heatsink shown in Figure 11b.                                                                                       |

| SN-K12-X01001          | 12 channel InterBoard™ SNAP 12 Transmitter/Receiver<br>Evaluation Kit- includes Evaluation Board and User Guide.                                                                                                         |

Reflex Photonics Inc. 550 Sherbrooke West, Suite 680, West Tower Montreal, Quebec, Canada, H3A-1B9

#### © Copyright 2009, Reflex Photonics Inc.

This document including pictures and drawings contains information about a new product during its early phase of development. The information contained herein is given to describe certain components and shall not be considered as a guarantee of characteristics. Reflex Photonics reserves the right to change the design or specifications of the product at any time without notice. The material is provided as is and without any warranties, including but not limited to warranties of non-infringement, description and fitness for a particular purpose.

#### www.reflexphotonics.com