# CMX Status, installation and integration plans

Chip Brock, Dan Edmunds, Philippe Laurens, Savanna Shaw @MSU Yuri Ermoline, Duc Bao Ta @MSU/CERN Wojciech Fedorko @UBC Pawel Plucinski @Stockholm University

L1 Calo General meeting 20 Feb 2014

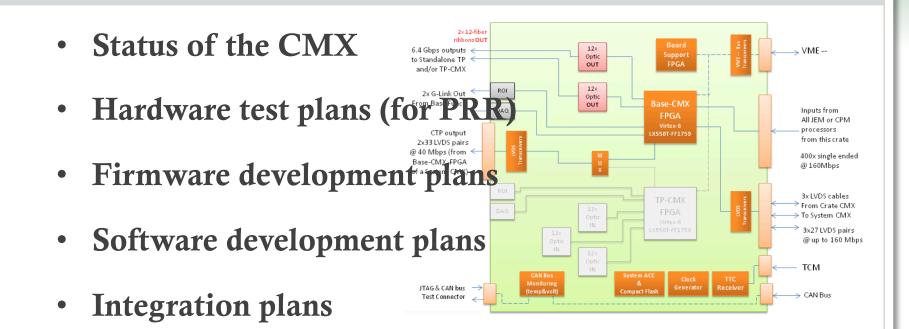

### Overview

## Status of CMX

- Arrival of three prototype CMX

- One empty board

- One only with board support FPGA

- Two will be fully loaded

- First tests performed, today achieve pattern capture on CMX from JEM

### Status of CMX

$\overline{\mathbf{M}}$

#### • Test plans for successful PRR

- Initial bare tests @ MSU, then with MSU test rig and JEM

- System tests @ CERN test rig, system test in one crate in USA15

- Concentrate on basic interface tests, esp. backplane transmission

- Initial board checkout@ MSU (Dan, Philippe)

- Board inspection and final assembly and installation of components

- Board support FPGA configuration via JTAG and VME IO

Today

- Base and top FPGA configuration via JTAG/CF

- Interface tests to using the MSU test rig (Dan, Philippe, Wojciech, Pawel)

- Establish the system clocking for Base and Topo FPGAs

- Backplane connectivity and timing measurement

- Test data interfaces standalone in loopback

- Embed Chipscope cores for control and monitoring to minimizing SW support

- Possibly use updated CMX software and CMX timing software already in interface tests

2 weeks @ MSU, continue @ MSU&CERN for ~4 weeks

- Backplane data transmission tests in Lab 104 (Wojciech, Pawel, Duc, Savanna, Yuri)

- Preparation for USA15 tests

- Operation parameters for 160 Mbps backplane input from single JEM using timing procedure/software

- Long term data stability test with stress data patterns in test crate

- System tests with full crate and two CMX prototypes in USA15 (Wojciech, Pawel, Duc, Savanna, Yuri)

- Test of full high-speed backplane performance with full crate of at least JEMs for long periods of time

- Looking into having JEM energy sum as well for electrical tests

- Redo data integrity test as in CERN test rig

- Power and power quality tests

- L1calo standalone partition for one (JEM) crate would be sufficient, no CTP needed, no other detector systems needed

### **Continued interface testing in Lab 104**

- CPM testing

- In contact with Jurai about CPM firmware and software

- Would need same/similar capability as the JEM

# Installation of CMX production cards for M-runs as soon as...

- PRR successful

- Production of CMX card completed

- Tests of production CMX cards @MSU finished

- Development of firmware along with the hardware tests (Wojciech, Pawel)

- Prototype firmware for initial test

- Focus on jet firmware first, re-use building blocks for other parts of the firmware

- Development of Board Support FPGA (Yuri)

- Control of the AVAGO TXRXs

- LVDS buffer control

- TTC control

#### • JET System

- ROI, DAQ readout

- LVDS IO module adaptation Spy memory integration

- RT path thresholding

- FW integration and verification with simulation software and comparing to software model on test vectors

- Jet Crate:

#### in sync with simulation development

- Adaptation of thresholding logic from system

- FW integration and verification

- Following the Jet System/Jet Crate firmware

- Sum ET Crate/System, CPM

- Decoder, Encoder, Sum logic

- FW integration and verification

- in sync with simulation development

- Development along with hardware tests and firmware development (Duc, Savanna)

- Prototype software in hardware tests, especially timing software

- Simulation needs to be completed for firmware verification

- Basic structure available via copy of CMM simulation

- Creation of test vectors, but no sensible patterns defined, yet

- Online software development, finished tasks

- Various data formats implemented

- Thresholding of jets implemented

- JEM System and crate merger updated/implemented

- Online software development, on-going

- CMX timing procedure and software

- Documentation in development

- Abstract version of procedure in code

- Implementation of interfaces to actual CMX registers

- Update of other CMM parts in the software

- CMX test vector generation

- CMX to Topo development

- CMX stand-alone test environment

# Integration plans

- Hardware level integration (data sending receiving)

- During hardware tests initial integration with

- JEM (single), CPM (single), ROD (DAQ/ROIB)

- Integration at later stage

- Complete integration with above

- Crate-System CTP (CMX as sink) LVDS

- Topo (CMX as sink)

#### • Online software development and system integration

- DB interface available

- Software interfaces to other simulations via agreed data formats and data ports

- JEM, CP, TOPO, CTP, ROS

## Summary

#### • Hardware tests

- Initial hardware tests @ MSU have started

- Interface tests @ MSU will start soon

- Backplane transmission tests and system tests planned @ CERN in Lab 104 and USA15

#### • Development of firmware and software

- Prototype firmware and software used for first tests

- Continued firmware and software development

- Firmware verification needs completed simulation software

#### • Integration plans

- Hardware/firmware integration will start in hardware test

- Software integration hopefully easier via agreed-on data formats

#### • Test plans for successful PRR

- Initial bare tests @ MSU, then with MSU test rig and JEM

- System tests @ CERN test rig, system test in one crate in USA15

- Concentrate on basic interface tests, esp. backplane transmission

- Initial board checkout@ MSU (Dan, Philippe)

- Board inspection and final assembly and installation of components

- Grounding and power verification

- Clock testing and characterization

- Board support FPGA configuration via JTAG and VME IO

Today

• Base and top FPGA configuration via JTAG/CF

- Interface tests to using the MSU test rig (Dan, Philippe, Wojciech, Pawel)

- Establish the system clocking for Base and Topo FPGAs

- Backplane connectivity and timing measurement

- Test data interfaces standalone in loopback

- Low speed serial TX connectivity test

- High speed serial Base RX/ Topo TX connectivity

- LVDS RTM (crate to system) communication at 80 Mbps

- LVDS front panel (CTP) communication at 40 Mbps

- BASE to TOPO GPIO link

- Operation parameters for 160 Mbps backplane input from single JEM using timing procedure/software

- Development of stress test data patterns

- Embed Chipscope cores for control and monitoring to minimizing SW support

- Possibly use updated CMX software and CMX timing software already in interface tests

2 weeks @ MSU, continue @ MSU&CERN for ~4 weeks

- Backplane data transmission tests in Lab 104 (Wojciech, Pawel, Duc, Savanna, Yuri)

- Preparation for USA15 tests

- Operation parameters for 160 Mbps backplane input from single JEM using timing procedure/software

- Long term data stability test with stress data patterns in test crate

- Further data interface tests on-going @ MSU

- Further tests in Lab 104, but not needed before USA15 full crate test

- DCS tests

- Continuing data interface test, possibly with other hardware components (e.g. CPMs)

- System tests with full crate and two CMX prototypes in USA15 (Wojciech, Pawel, Duc, Savanna, Yuri)

- Test of full high-speed backplane performance with full crate of at least JEMs for long periods of time

- Expertise and support on JEM at hand

- Looking into having JEM energy sum as well for electrical tests

- Redo data integrity test as in CERN test rig

- Power and power quality tests

# System tests with full crate and two CMX prototypes in USA15, cont.

- Re-use prototype FWs used in previous tests

- L1calo standalone partition for one (JEM) crate would be sufficient, no CTP needed, no other detector systems needed

- Operations experts would be needed to facilitate partition building and running tests concurrently with other sub-systems

- Would want to have separate partition for CMX test from partition for other L1Calo test or ATLAS subsystems

### **Continued interface testing in Lab 104**

- CPM testing

- In contact with Yurai about CPM firmware and software

- Would need same/similar capability as the JEM

# Installation of CMX production cards for M-runs as soon as...

- PRR successful

- Production of CMX card completed

- Tests of production CMX cards @MSU finished

- Development of firmware along with the hardware tests (Wojciech, Pawel)

- Prototype firmware for initial test

- Focus on jet firmware first, re-use building blocks for other parts of the firmware

- Development of Board Support FPGA (Yuri)

- Control of the AVAGO TXRXs

- LVDS buffer control

- TTC control

### • JET System

- ROI, DAQ readout

- LVDS output module adaptation (CP, CRATE->SYSTEM) (80 Mbps), LVDS input module adaptation (CRATE->SYSTEM) (80 Mbps)

- Spy memory integration

- RT path thresholding

- FW integration

#### Jet System FW verification

- 'FPGA' level TB developed

- generation of stimulus file based on

- physics simulation

- case-based

- Verification with simulation software and comparing to software model on pre-loaded data

- Jet Crate:

- adaptation of thresholding logic from system

- FW integration and verification *m* in sync with simulation development

*in sync with simulation development*

- Following the Jet System/Jet Crate firmware

- Sum ET Crate/System, CPM

- Decoder

- Encoder

- Sum logic

- FW integration

- Verification

in sync with simulation development

- Development along with hardware tests and firmware development (Duc, Savanna)

- Prototype software in hardware tests, especially timing software

- Simulation needs to be completed for firmware verification

- Online software development

- Services = register map update along the development of firmware

- On-going effort

- Copy of CMM simulation

- Basic structure available

- Reading test vectors

- Creation of test vectors, but no sensible patterns defined, yet

- Online software development, finished tasks

- Data formats implemented

- JEM (jet and energy sum), CP -> CMX

- crate CMX -> system CMX created

- CMX -> ROS, CTP

- Thresholding of jets implemented

- JEM System and crate merger implemented

- Online software development, on-going

- CMX timing procedure and software

- Procedure agreed on, documentation in development

- Abstract version of procedure in code

- Implementation of interfaces to actual CMX registers

- Merge code to read/write timing test patterns

- Integration into TDAQ system

in sync with hardware tests

- Online software development, on-going

- Update of CMM parts in the software

- JET Daq merger

- Energy sum merger, similar to CMM

- Eg merger, similar to CMM

- CMX test vector generation .

- CMX to Topo development

in sync with firmware verification

CMX stand-alone test environment

# Integration plans

- Hardware level integration (data sending receiving)

- During hardware tests initial integration with

- JEM (single), CPM (single), ROD (DAQ/ROIB)

- Integration at later stage

- Complete integration with above

- Crate-System CTP (CMX as sink) LVDS

- Topo (CMX as sink)

#### • Online software development and system integration

- DB interface available

- Software interfaces to other simulations via agreed data formats and data ports

- JEM, CP, TOPO, CTP, ROS

## Summary

#### • Hardware tests

- Initial hardware tests @ MSU have started

- Interface tests @ MSU will start soon

- Backplane transmission tests and system tests planned @ CERN in Lab 104 and USA 15

#### • Development of firmware and software

- Prototype firmware and software used for first tests

- Continued firmware and software development

- Firmware verification needs completed simulation software

#### • Integration plans

- Hardware/firmware integration will start in hardware test

- Software integration hopefully easier via agreed-on data formats