1

# AN INTELLIGENT HOT-SWAP CONTROLLER FOR ATCA FRU

A Lattice Semiconductor White Paper April 2005

> Lattice Semiconductor 5555 Northeast Moore Ct. Hillsboro, Oregon 97124 USA Telephone: (503) 268-8000 www.latticesemi.com

An Intelligent Hot-Swap Controller for ATCA FRU A Lattice Semiconductor White Paper

# What is AdvancedTCA?

Advanced Telecommunications Computing Architecture, or AdvancedTCA, is a new series of industry standard specifications for a variety of equipment including carrier grade communications equipment, high performance blade servers and high-speed routers. This standard is driven by hundreds of companies under the PCI Industrial Computers Manufacturing Group (PICMG), and incorporates the latest trends in high speed interconnect technologies, next generation processors, improved reliability, manageability and serviceability, resulting in a new blade (board) and chassis (shelf) form factor optimized for communications. Each circuit board in an ATCA shelf is called a Field Replaceable Unit (FRU).

The primary impetus to develop the ATCA standard is to reduce the system's cost and its time to market. Designers can leverage this standard for developing systems by simply focusing on developing their application specific hardware. This is because the ATCA standard, with its high performance backplane, high power distribution capability, increased reliability and cooling meets the requirements of systems across a wide range of applications. This results in driving down the cost and increasing the availability of the ATCA base shelf manufactured by a number of vendors.

## Implementation

The power distribution section of the ATCA standard is based on the use of intelligence in power supply management. The Intelligent Platform Management Controller (IPMC) provides the intelligence to control the power on the card. There are three control elements in a power supply management circuit of an ATCA card. They are:

- 1. Hot-Swap controller

- 2. IPM Controller

- 3. Secondary Power Manager

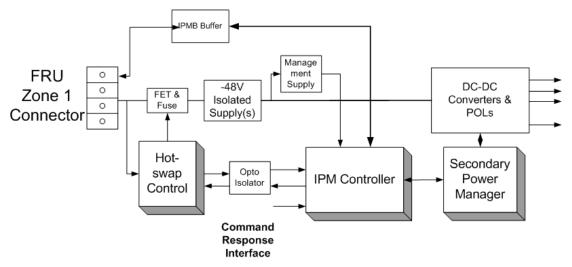

Figure 1 shows a typical power supply arrangement in an ATCA circuit board.

Figure 1 - Typical FRU power supply management block diagram

The main power supply for the FRU is derived from a dual -48V power bus (zone 1 connector). The purpose of the Hot-Swap controller is to limit the inrush current when the FRU is plugged into the live backplane.

An isolated power supply on the circuit board generates +12V (Intermediate Power Supply Bus) from the –48V power source. The Intermediate Power Supply Bus powers a number of non-isolated DC-DC converters required to power on-board devices. Designs often use a separate power management supply to power IPMC and secondary power manger ICs.

After power-on, the IPMC communicates with the shelf manager through the IPMB (Intelligent Platform Management Bus) and provides the circuit board details. The shelf manager then issues a command to the IPMC to power the FRU. The IPMC signals the secondary power manager to turn all the local circuit board power supplies on to power the ICs.

The Secondary Power Manager (SPM) turns the power supplies on by following the sequencing and tracking requirements of the devices used on the FRU. Once all the supplies are turned on and have reached their operating voltage, the SPM generates the appropriate logic signals (e.g., PowerGood, ResetCPU, etc) and the FRU is said to be in normal operation mode. Once the normal operation of the card begins, SPM begins to monitor all the power supply voltages on the circuit board and any power supply failure is flagged to the IPMC for appropriate action. If the power supply fault is severe, the IPMC could also signal the secondary power manager to shut the power supply off to all the devices on the circuit board.

The intelligence of the IPMC serves two main purposes: Provide a wellcontrolled power on process in an FRU, and also prevent fault propagation into the system. While the IPMC is able to control the power supply of the FRU on the secondary side, the hot-swap circuitry is traditionally autonomous. The IPMC gets no indication of any fault on the primary side, such as input voltage (-48V) low/ high, excess current or faulty fuses. The hot-swap controller decides the course of action for a given power supply condition and, if needed, turns the power supply off. This reduces the time available for the board to perform safe shut down.

Consider this: If the hot-swap controller on the -48V side provides the status in real time, it increases the time available for the IPMC to perform an appropriate shut-down process to communicate with the shelf manager to flag the operator to check for the fuse on that circuit board, etc., thereby improving the manageability, and serviceability of the system and resulting in a more reliable system.

This article examines a traditional, full-featured hot-swap controller circuit, and then suggests an intelligent hot-swap circuit that not only provides early warning to IPMC but also accepts commands from the IPMC for a controlled shutdown on the –48V side of the power supply.

## Traditional Hot-Swap Solution

The functions of a traditional full-featured hot-swap circuit in an FRU include:

## Inrush Current Limit

When an FRU is plugged into a live chassis backplane, the on board discharged bulk power supply capacitors draw large amounts of current from the power supply. This sudden surge in current often causes the backplane power supply An Intelligent Hot-Swap Controller for ATCA FRU A Lattice Semiconductor White Paper voltage to dip momentarily, interrupting the operation of the circuit boards already in the chassis. The primary function of a hot-swap controller is to limit this initial current in-rush. Traditionally, hot-swap controllers have used N-channel pass FET devices in conjunction with current sense resistors to limit the current inrush. Additionally, this controlled the turn-on delay of the FET devices, extending the power supply connector's electrical life.

#### Detection of -48V Over Voltage & Under Voltage Limits

ATCA explicitly describes the circuit behavior over voltage and under voltage as well as transient conditions. Designers usually resort to bulk capacitors and timing circuits in order to meet these specifications under transient conditions, since the ICs shut down the power supplies during over and under voltage conditions. Hot-Swap controllers just cut off the power supply to the secondary side of the circuit when the primary side power supply develops a fault. Because there is no communication between the primary and the secondary side of the power supply, power management circuitry on the secondary side has a limited time to respond to the power disconnection.

#### **Detection of Over Current**

Over current detection is achieved simply by monitoring the voltage across a series pass resistor in the power supply circuit, and, in the case of a fault, the power supply is cut off by turning the FET off. There is no warning generated to the secondary side.

## Improving Board Reliability

As discussed, traditional hot-swap solutions are autonomous and do not communicate with the main board power supply controller. However, the following features, if included, provide more control over supplying power to the board and also increase the time available for responding to various types of faults. This reduces fault propagation and also prevents a forced FRU shut down due to double faults (as in the case of two fuse "blow-out fault").

#### Fuse Detection

ATCA specifies that a fuse be placed on both the -48V and the return limbs of the power supply, resulting in the use of four fuses. Sometimes when the card is plugged into the backplane, a fuse might open. This is because the board is designed to operate without interruption, even If one of the fuses is open. It is difficult to detect a fuse failure and the operator will only detect one when both fuses are open, at which time it could be too late to maintain the quality of service. If there is a mechanism in place to detect when one fuse fails, the operator could be instructed to perform maintenance before the circuit board completely fails.

## Flagging UV & OV Conditions to the On-board IPMC

Under voltage indication can be used to provide an early warning to the CPU on the FRU board. This increases the time available for the CPU to safely perform the shutdown operation, including shutting down the secondary power supply following the rules of power supply sequencing.

A catastrophic over voltage condition can be used to shut the series pass FET off, protecting the -48V isolated power supply brick and also providing a warning to the IPMC for safe shut down procedure.

## Flagging Over Current warning to the IPMC

Power supply current can be monitored to generate over current warning to the IPMC. The IPMC can then use this signal to isolate the fault (e.g., a partially faulty AMC) that is causing this over current condition, or to inform the shelf manager to increase the airflow, etc.

If the current reaches catastrophic fault level, the series pass FET can be turned off to protect the circuit board from overheating.

## Ability to Isolate the Card Under the IPMC Command

Series FETs offer a second level control for powering off a circuit board under on-board power supply fault conditions. The IPMC can also use this mechanism to completely isolate the card from the backplane and prepare for card extraction. In the case of ATCA boards with multiple -48V isolated power supplies, IPMC could turn on the second isolated power supply brick by another series FET to meet the increased power requirement.

#### **IPMC Controlled Retry Power Cycling**

Retry power cycling is a process by which the hot-swap controller turns the series FET off, waits for the primary side to power off completely, waits for perhaps1 second and turns it back on. This may be required for simulating the card extraction and re-insertion, or required by the diagnostic system to classify a fault on the board between temporary and permanent, or required to implement a total carrier board reconfiguration after replacing a faulty AMC, etc. In all these cases, the power retry can replace mechanical operation, resulting in increased connector life.

## Intelligent Hot-Swap Controller Circuit

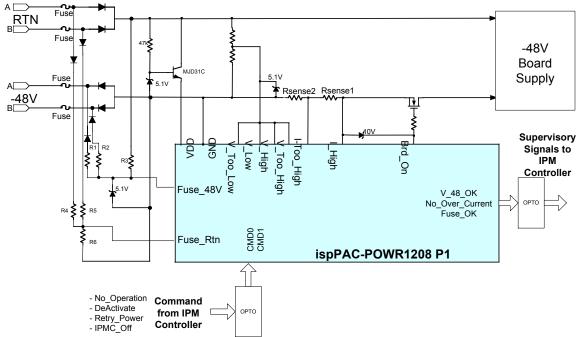

Figure 2 - Intelligent Hot-Swap Circuit Using a Programmable Power Manager

#### **Circuit Description**

Figure 2 shows an intelligent ATCA compliant hot-swap circuit based on a programmable power manager – in this case the ispPAC-POWR1208P1 (Power1208P1). This is a "canned" ATCA hot-swap power control solution. Starting from the left of the Power1208P1, 2 sets of the resistor divider circuits are used to monitor all four fuses (pins: Fuse\_48V, Fuse\_Rtn). The next portion of the circuit on the top left side of the device (VDD & GND) is the power supply to the device, which is regulated by a zener diode. Continuing on the top of the device, the next section monitors -48V for four different analog inputs with individual thresholds (V\_Too\_Low, V\_Low, V\_High, V\_Too\_High). Usually, the V\_Low and V\_High thresholds are used for generating supervisory signals to the IPMC. The V\_Too\_high & V\_Too\_Low thresholds are used for disconnecting the series FET.

The inputs I-Too\_High & I\_High monitor for current on the circuit board. The I\_high current threshold is used to send an over current signal to the IPMC. The I\_Too\_High Threshold turns off of Series FET, protecting the circuit board. The Brd\_On signal controls the series FET enable circuit. This programmable output pin is used as a switch and also provides the soft start mechanism to limit current inrush. The outputs on the right side of the chip (V\_48\_OK, No\_Over\_Current, Fuse\_OK) are the supervisory signals to warn the IPMC of the status of the power supply. The supervisory signals are routed through opto-couplers to meet the isolation requirements between the IPMC on the secondary side and the hot-swap circuit on the primary side. The commands from the IPMC are received by the Power Manager IC, as shown at the bottom of the circuit (CMD0, CMD1), through an opto-coupler.

#### Power Supply Voltage Monitoring

This section monitors the -48V power supply for over Voltage, catastrophic over voltage, under voltage & very low voltage. Four analog monitoring inputs (V\_Too\_Low, V\_Low, V\_High, V\_Too\_High) of the Programmable Power manager device are set at different thresholds to monitor each of these

conditions. When the power supply voltage is said to be in the normal operating range (More than V\_Low threshold and Less than V\_High threshold) this is indicated by an active V\_48\_OK supervisory signal. When the power supply voltage is less than V\_Too\_Low Threshold, the Series FET is turned off after a 10 ms timeout and, if the voltage is greater than V\_Too\_High threshold, the Series FET is turned off immediately.

#### Fuse Detection Circuit

The fuse detection circuit consists of resistors R1, R2 and R3, sensing the fuses on the RTN terminals and R4, R5 and R6, sensing voltage on the -48V terminal. If either fuse fails on the RTN terminal, the voltage on at the Fuse\_Rtn pin drops below its threshold, resulting in the change of logic output indicating the fuse failure on either limb. Similarly, the Fuse\_48V threshold detects the fuse open condition on the -48V limbs. The Fuse\_OK signal is deactivated when any fuse opens.

## **Over Current Protection**

Over Current protection is achieved by monitoring voltage drop across two resistors (Rsense1 and Rsense 2) in series by separate analog monitoring inputs I\_High and I\_Too\_High. When the current is within the normal operating limit (less than the I\_High threshold) the "No\_Over\_Current" signal will be active and when the current exceeds "I\_Too\_High" threshold, the series transistor is turned off, protecting the circuit.

## Inrush Current Limiting & Series FET control

The Brd\_On is a programmable high voltage analog output signal of the Power Manager device. This output can be programmed to control the FET turn-on ramp rate. There are 32 different ramp rates settings available on this programmable output pin.

The Series FET device is also used for turning the power supply off for the entire circuit board. These are the conditions that result in the Series FET being tuned off for protection:

- 1. -48V is either Too High or Too Low for more than 10 ms

- 2. Current is Too High

- 3. IPMC sends a "Deactivate" command

4. IPMC sends "Retry\_Power" Command (Series FET will be turned off until the secondary side is completely off and an additional 1 second and turned back on)

#### **IPMC Command & Supervisory Signal Interface**

There are 3 supervisory signals generated by the Power1208P1:

1. -48V OK - indicates that the -48V source is within the operating limits

2. No\_Over\_Current - indicates that the power supply current is healthy and is within limits

3. Fuse\_OK - indicates that all four fuses are intact.

There are two command bits generated by the IPMC controller – CMD0, CMD1

00 - All Power Supplies are OK and the Power1208P1 need not take any action

01 - Deactivate Circuit board - Turn the series FET OFF

10 - Retry power supply – Turn the series FET OFF, wait for all the board supplies to turn off and wait one more second and turn the FET back on.

11 - IPMC is off – Indicates that all the power supplies on the secondary side are off.

# Software Code for the Power1208P1

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |                      |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | - D × |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PAC-Designer - [Hotswap Controller,PAC: Sequence Controller]                     |                      |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| Eile Edit View Tools Options Window Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | jile <u>E</u> dit <u>V</u> jew Iools <u>O</u> ptions <u>Wi</u> ndow <u>H</u> elp |                      |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| D 📽 🖫 🞒   ⊕ ⊕ ⊕   ]), 2, 3, 4,   \ +   🐲                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |                      |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |                      |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |                      |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |                      |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |                      |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| Step Sequencer Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |                      | Inte                                                               | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| Step 0 Wait for NOT V_Low AND NOT V_High   Step 1 Brid (On = 1, V, 4K) (SK = 1, 6, 0, 0, ver, Current = 1, 5   Step 2 Wait for NOT CMD0 AND NOT CMD1   Step 3 Wait for NOT CMD0 AND NOT CMD1   Step 4 IF CMD0 AND NOT CMD1 Then Gato 6 Else Gato 5   Step 5 IF CMD0 AND NOT CMD1 Then Gato 6 Else Gato 6   Step 5 IF CMD0 AND CMD1 Then Gato 8 Else Gato 6   Step 6 Ed (On = 0, 5   Step 7 Hit   Step 8 Ed (On = 0, 5   Step 9 Wait for S24.3ms using timer 1   Step 10 Wait for S24.3ms using timer 1   Step 11 NOP   Step 12 Wait for S24.3ms using timer 1   Step 13 Go to step 0   Step 14 Hait (end-of-program) |                                                                                  |                      | ио<br>учез<br>учез<br>учез<br>учез<br>учез<br>учез<br>учез<br>учез | Wait for +49V to stabilize<br>Tum Sereise FTC on, Activate 48V OK & No Over Current Flags<br>Wait for IDMO: to signal Normal Operation<br>No Action IT FMOC has no command and no over voltage or current condition<br>Check for Paetry Power Command<br>Severe Fault condition or DEactivate Command - Turn off Power<br>Responding to Power recycle command<br>Wait for IDMO: to indicate no power<br>Wait for IDMO: to indicate no power<br>Wait for IDMO: to indicate no power<br>Wait for IDMO: to indicate no power |       |

| Exception ID Boolean Expression                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Outputs                                                                          | Exception Handler    | Com                                                                | ment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| E0 If NOT Fuse_48V OR NOT Fuse_Rtn<br>E1 If I_High<br>E2 If NOT V_Low OR V_High<br><end-of-exception-table></end-of-exception-table>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Vegeds   Fuse_OK = 0,   No_Over_Current = 0,   V_48_OK = 0,                      | not used<br>not used | Fuse<br>No_C                                                       | Jeann<br>Vier Cument Rag is set when the Cument exceeds limit<br>OK Rag is cleared when the output voltage exceeds either thresolids                                                                                                                                                                                                                                                                                                                                                                                      |       |

| l<br>Ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |                      |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10    |

Figure 3: Hot-Swap algorithm source code

Figure 3 shows the algorithm implemented using the LogiBuilder utility built into the PAC-Designer software tool. The Power1208P1 begins executing from step 0 as soon as the power supply (in this case the -48V at the backplane) to the device is turned on.

This design is compiled by the software and a JEDEC file is generated that can be downloaded into the chip. This software source is available from the author upon request at <a href="mailto:shyam.chandra@latticsemi.com">shyam.chandra@latticsemi.com</a>. The PAC-Designer software can be downloaded from the Lattice website (<a href="http://www.latticesemi.com/">http://www.latticesemi.com/</a>).

# Conclusion

## Intelligence Improves Board Reliability

The early warning mechanism built into the hot-swap circuitry increases the time available for fault handling on the secondary side, resulting in increased functional board reliability. By incorporating the command control ability into the hot-swap circuit, the IPMC will be able to contain the problem to the circuit board with ample time to react. This increases the reliability of the circuit board even further. The ispPAC-POWR1208P1 device provides unprecedented convenience to designers of ATCA Hot-Swap circuits.

#### Software Based Design Results in Flexibility

Not all circuit board requirements are identical. Because the command and supervisory warning algorithm of the Hot-Swap controller is implemented completely in software, it is very easy to modify the algorithm. For example, to alter the voltage thresholds monitored, one simply reprograms the V\_Low and V\_High thresholds. If additional monitoring signals are required, just redefine the output signal equations in software.

#### Additional Functionality That Can be Programmed

Addition of intelligence to the Hot-Swap circuitry makes additional features available that were not possible even with sophisticated, full-featured traditional Hot-Swap devices.

For example, it is possible to add a -48V isolated supply (say, to power the AMCs of the circuit board) with its own series pass FET, along with another command signal from the IPMC, to control this new power supply. Thus, the additional –48V Supply can be switched on in response to power consumption increase grant from ATCA shelf manager.

It is also possible to sense each fuse separately and generate a Fuse\_OK signal for the A and B limbs separately. This enables the system to detect other types of faults. If the A side is online and the fuse in series with the A-limb of the power supply is faulty, then the fault becomes more serious and might require immediate attention, as opposed to an open fuse on the B-limb when the A side is on-line).

###