## **TPS40400**

SLUS930B-APRIL 2011-REVISED OCTOBER 2011

# 3.0-V TO 20-V PMBus SYNCHRONOUS BUCK CONTROLLER

Check for Samples: TPS40400

# **FEATURES**

- Input Operating Voltage Range: 3 V to 20 V

- PMBus Enabled Analog Controller

- Reference 600 mV ± 1%

- Remote Voltage Sense Amplifier

- Internal 6-V Regulator and 6-V Gate Drive

- Programmable Overcurrent Protection

- Inductor Resistance or Series Resistance Used for Current Sensing

- Programmable Switching Frequency: 200 kHz to 2 MHz

- Powergood Indicator

- Thermal Shutdown

- Programmable Soft-Start

- Internal Bootstrap Diode

- Pre-bias Output Safe

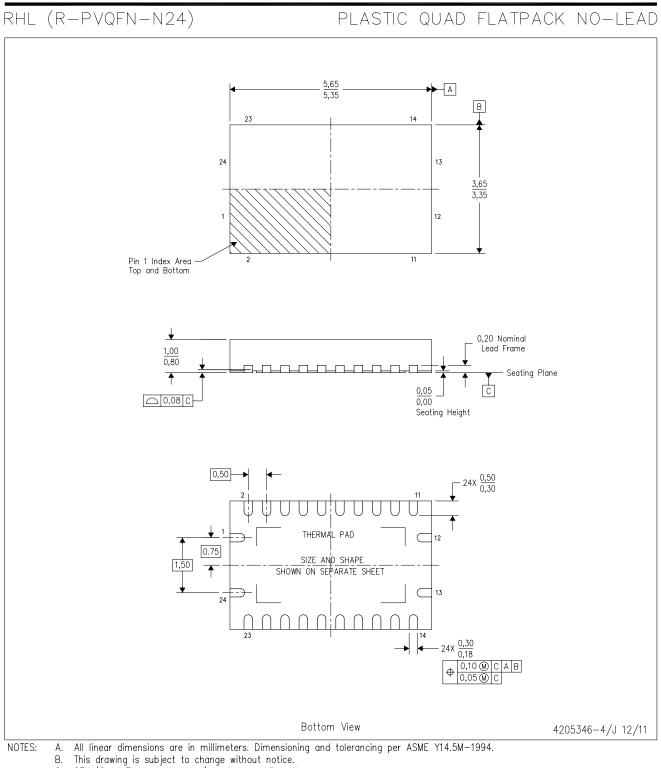

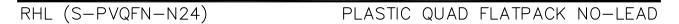

- 24-Pin QFN Package

# APPLICATIONS

- Smart Power Systems

- Power Supply Modules

- Communications Equipment

- Computing Equipment

## DESCRIPTION

The TPS40400 cost-optimized is flexible а synchronous buck controller that operates from a nominal 3 V to 20 V supply. This controller is an analog PWM controller that allows programming and monitoring via the PMBus interface. Flexible features found on this device include programmable soft-start circuit time. programmable short limit and programmable undervoltage lockout (UVLO).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. SwitcherPro is a trademark of Texas Instruments. SLUS930B-APRIL 2011-REVISED OCTOBER 2011

# **DESCRIPTION (CONTINUED)**

An adaptive anti-cross conduction scheme is used to prevent shoot through current in the power FETs. Gate drive voltage is 6 V to better enhance the power FETs for reduced losses. Short circuit detection is done by sensing the voltage drop across the inductor or across a resistor placed in series with the inductor. A PMBus programmable threshold is compared to this voltage and is used to detect overcurrent. When the overcurrent threshold is reached, a pulse by pulse current limit scheme is used to limit current to acceptable levels. If the overcurrent condition persists for more than 7 clock cycles of the converter, a fault condition is declared and the converter shuts down and goes into either a hiccup restart mode or latches off. The behavior is selectable though the PMBus interface. Other PMBus interface features include programmable operating frequency, soft-start time, overvoltage and undervoltage thresholds and the response to those events, output voltage change including margining as well as status monitoring.

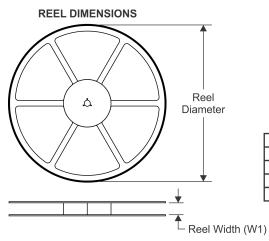

## **ORDERING INFORMATION**<sup>(1)(2)</sup>

| PACKAGE            | PINS | TAPE AND REEL QTY. | ORDERABLE NUMBER |

|--------------------|------|--------------------|------------------|

| Plantia OEN (DUIL) | 04   | 250                | TPS40400RHLT     |

| Plastic QFN (RHL)  | 24   | 3000               | TPS40400RHLR     |

(1) For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

(2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

## **ABSOLUTE MAXIMUM RATINGS**

|                                                     |                                                         | VALUE | VALUE |      |

|-----------------------------------------------------|---------------------------------------------------------|-------|-------|------|

|                                                     |                                                         | MIN   | MAX   | UNIT |

|                                                     | VDD                                                     | -0.3  | 22    |      |

|                                                     | SW                                                      | -5    | 27    |      |

|                                                     | BOOT                                                    | -0.3  | 30    |      |

| Innut voltogo rongo                                 | BOOT-SW, HDRV-SW (Differential from BOOT or HDRV to SW) | -0.3  | 7     | V    |

| Input voltage range                                 | VSNS+, TRACK, SYNC, FB                                  | -0.3  | 7     | V    |

|                                                     | DATA, CLK, CNTL                                         | -0.3  | 3.6   |      |

|                                                     | ISNS+, ISNS-                                            | -0.3  | 15    |      |

|                                                     | VSNS-                                                   | -0.3  | 0.3   |      |

|                                                     | HDRV                                                    | -0.3  | 30    |      |

|                                                     | BP3                                                     | -0.3  | 3.8   | V    |

| Output voltage range                                | BP6, COMP, PGOOD, DIFFO, LDRV                           | -0.3  | 7     | V    |

|                                                     | SMBALRT, ADDR0                                          | -0.3  | 3.6   |      |

| T <sub>J</sub> Operating junction temperature range |                                                         | -40   | 150   | °C   |

| T <sub>STG</sub> Storage tempera                    | -55                                                     | 150   | °C    |      |

## PACKAGE DISSIPATION RATINGS<sup>(1)</sup>

| PACKAGE                     | THERMAL IMPEDANCE<br>JUNCTION-TO-AMBIENT<br>(°C/W) | AIRFLOW            | T <sub>A</sub> = 25°C<br>POWER RATING<br>(W) | T <sub>A</sub> = 85°C<br>POWER RATING<br>(W) |

|-----------------------------|----------------------------------------------------|--------------------|----------------------------------------------|----------------------------------------------|

|                             | 31.1                                               | Natural Convection | 3.21                                         | 1.29                                         |

| 24-Pin Plastic<br>QFN (RHL) | 25.2                                               | 200 LFM            | 3.96                                         | 1.58                                         |

|                             | 23                                                 | 400 LFM            | 4.36                                         | 1.74                                         |

(1) Ratings based on JEDEC High Thermal Conductivity (High K) Board. For more information on the test method, see TI Technical Brief SZZA017.

## **RECOMMENDED OPERATING CONDITIONS**

|     |                                | MIN | TYP MAX | UNIT |

|-----|--------------------------------|-----|---------|------|

| VDD | Input operating voltage        | 3.0 | 20      | V    |

| TJ  | Operating junction temperature | -40 | 125     | °C   |

2 Submit Documentation Feedback

Copyright © 2011, Texas Instruments Incorporated

SLUS930B - APRIL 2011 - REVISED OCTOBER 2011

# **ELECTROSTATIC DISCHARGE PROTECTION**

|                            | MIN | TYP  | MAX | UNIT |  |

|----------------------------|-----|------|-----|------|--|

| Human Body Model (HBM)     |     | 2500 |     | V    |  |

| Charged Device Model (CDM) |     | 1500 |     | V    |  |

# **ELECTRICAL CHARACTERISTICS**

|                       | PARAMETER                                                         | TEST CONDITIONS                                                                                                   | MIN                   | TYP                   | MAX                   | UNIT |

|-----------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|------|

| INPUT SUP             | PLY                                                               |                                                                                                                   |                       |                       |                       |      |

| V <sub>VDD</sub>      | Input voltage range                                               |                                                                                                                   | 3                     |                       | 20                    | V    |

| VDD                   | Input operating current                                           | Switching, no driver load                                                                                         |                       | 6                     | 15                    | mA   |

|                       | REFERENCE                                                         |                                                                                                                   |                       |                       |                       |      |

| V <sub>FB</sub>       | Feedback pin voltage default settings                             | -40°C ≤ T <sub>J</sub> ≤ 125°C                                                                                    | 594                   | 600                   | 606                   | mV   |

| V <sub>FB(max)</sub>  | Feedback pin voltage maximum adjustment                           |                                                                                                                   |                       | 750                   |                       | mV   |

| V <sub>FB(min)</sub>  | Feedback pin voltage minimum adjustment                           |                                                                                                                   |                       | 450                   |                       | mV   |

| V <sub>FB(inc)</sub>  | Feedback pin voltage adjustment resolution                        |                                                                                                                   |                       | 2.34                  |                       | mV   |

| V <sub>FB(NL)</sub>   | Maximum nonlinearity error over adjustment range                  |                                                                                                                   |                       |                       | 10                    | mV   |

| BP6 REGUL             | ATOR                                                              |                                                                                                                   |                       |                       |                       |      |

| V <sub>BP6</sub>      | 6-V regulator output voltage                                      |                                                                                                                   | 6.2                   | 6.5                   | 6.8                   | V    |

| V <sub>DO6</sub>      | Regulator dropout voltage, (V <sub>VDD</sub> – V <sub>BP6</sub> ) | V <sub>VDD</sub> = 6 V, I <sub>BP6</sub> = 50 mA                                                                  |                       |                       | 300                   | mV   |

| I <sub>BP6</sub>      | Regulator current limit                                           |                                                                                                                   | 100                   |                       |                       | mA   |

| BP3 REGUL             | ATOR                                                              |                                                                                                                   |                       |                       |                       |      |

| V <sub>BP3</sub>      | 3.3-V regulator output voltage                                    |                                                                                                                   | 3.1                   | 3.3                   | 3.5                   | V    |

| V <sub>DO3</sub>      | Regulator dropout voltage, (V <sub>VDD</sub> – V <sub>BP3</sub> ) | $V_{VDD} = 3V$ , $I_{BP3} = 5$ mA                                                                                 |                       | 100                   | 200                   | mV   |

| OSCILLATO             | )R                                                                |                                                                                                                   |                       |                       |                       |      |

| f <sub>SW</sub>       | Switching frequency                                               | Factory default setting                                                                                           | 480                   | 600                   | 720                   |      |

|                       | Nominal frequency range                                           |                                                                                                                   | 200                   |                       | 2000                  | kHz  |

|                       | Accuracy                                                          | $3 \text{ V} \leq \text{V}_{\text{VDD}} \leq 20 \text{ V}, 200 \text{ kHz} \leq f_{\text{SW}} \leq 2 \text{ MHz}$ | -20%                  |                       | 20%                   |      |

| V <sub>IH</sub>       | SYNC high-level input voltage                                     |                                                                                                                   | 2.0                   |                       |                       |      |

| V <sub>IL</sub>       | SYNC low-level input voltage                                      |                                                                                                                   |                       |                       | 0.4                   | V    |

|                       |                                                                   | V <sub>SYNC</sub> = 6 V                                                                                           |                       |                       | 100                   |      |

| ISYNC                 | SYNC pin leakage current                                          | V <sub>SYNC</sub> = 0 V                                                                                           |                       |                       | 100                   | nA   |

| t <sub>SRISE</sub>    | Maximum SYNC rise time <sup>(1)</sup>                             |                                                                                                                   | 100                   |                       |                       | ns   |

| t <sub>SYNC</sub>     | Minimum SYNC pulse width                                          |                                                                                                                   | 100                   |                       |                       | ns   |

|                       |                                                                   | FREQUENCY_SWITCH = 200 kHz                                                                                        | V <sub>VDD</sub> /6.6 | V <sub>VDD</sub> /6.5 | V <sub>VDD</sub> /6.3 | V    |

| V <sub>RMP</sub>      | Ramp amplitude <sup>(1)</sup>                                     | FREQUENCY_SWITCH = 600 kHz                                                                                        | V <sub>VDD</sub> /7.0 | V <sub>VDD</sub> /6.8 | V <sub>VDD</sub> /6.6 |      |

|                       |                                                                   | FREQUENCY_SWITCH = 2000 kHz                                                                                       | V <sub>VDD</sub> /10  | V <sub>VDD</sub> /9.6 | V <sub>VDD</sub> /9.2 |      |

| V <sub>VLY</sub>      | Valley voltage <sup>(1)</sup>                                     |                                                                                                                   |                       | 0.9                   |                       |      |

| SYNC                  | SYNC range % of nominal oscillator frequency                      | 200 kHz ≤ f <sub>SW</sub> ≤ 2 MHz                                                                                 | 85%                   |                       | 150%                  |      |

| PULSE WID             | TH MODULATOR (PWM)                                                | •                                                                                                                 |                       |                       |                       |      |

| D <sub>MAX</sub>      |                                                                   | FREQUENCY_SWITCH = 600 kHz                                                                                        | 90%                   |                       |                       |      |

|                       | Maximum duty cycle <sup>(1)</sup> (2)                             | FREQUENCY_SWITCH = 1.2 MHz                                                                                        | 85%                   |                       |                       |      |

|                       |                                                                   | FREQUENCY_SWITCH = 2 MHz                                                                                          | 75%                   |                       |                       |      |

| t <sub>OFF(min)</sub> | Minimum OFF time                                                  |                                                                                                                   |                       | 170                   | 225                   | ns   |

| t <sub>ON(min)</sub>  | Minimum controllable pulse <sup>(1)</sup>                         | T <sub>J</sub> = 25°C, f <sub>SW</sub> = 600 kHz                                                                  |                       |                       | 75                    | ns   |

Ensured by design. Not production tested.

Operation at 3 V reduces maximum duty cycle by approximately 5%.

SLUS930B - APRIL 2011-REVISED OCTOBER 2011

www.ti.com

ISTRUMENTS

EXAS

# **ELECTRICAL CHARACTERISTICS (continued)**

|                          | PARAMETER                                                          | TEST CONDITIONS                                                                                                                                                                               | MIN  | TYP                 | MAX | UNIT   |

|--------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|-----|--------|

| SOFT-STAR                | т                                                                  |                                                                                                                                                                                               |      |                     |     |        |

|                          | Soft-start time (3)                                                | Factory default setting                                                                                                                                                                       | 2.7  | 3.1                 | 3.5 | ms     |

| t <sub>SS</sub>          | Accuracy                                                           | 600 µs ≤ t <sub>SS</sub> ≤ 9 ms                                                                                                                                                               | -15% |                     | 15% |        |

| ERROR AM                 | PLIFIER                                                            |                                                                                                                                                                                               |      |                     |     |        |

| GBWP                     | Gain bandwidth product <sup>(4)</sup>                              |                                                                                                                                                                                               | 15   | 20                  |     | MHz    |

| A <sub>OL</sub>          | DC gain <sup>(4)</sup>                                             |                                                                                                                                                                                               | 60   |                     |     | dB     |

| I <sub>IBFB</sub>        | Input bias current: FB (out of pin)                                |                                                                                                                                                                                               | 0    |                     | 100 | nA     |

| I <sub>IBT</sub>         | Input bias current: TRACK (out of pin)                             |                                                                                                                                                                                               | 0    |                     | 250 | nA     |

| I <sub>EAOP</sub>        | Output source current                                              | $V_{FB} = 0 V, V_{COMP} \ge 2 V$                                                                                                                                                              | 1    |                     |     | 0      |

| I <sub>EAOM</sub>        | Output sink current                                                | $V_{FB} = 2 \text{ V},  V_{COMP} \leq 0.3 \text{ V}$                                                                                                                                          | 1    |                     |     | mA     |

| V <sub>COMPH</sub>       | Error amplifier high output voltage                                | V <sub>FB</sub> = 0 V                                                                                                                                                                         | 3.8  |                     |     | V      |

| V <sub>COMPL</sub>       | Error amplifier low output voltage                                 | V <sub>FB</sub> = 2 V                                                                                                                                                                         |      |                     | 50  | mV     |

| V <sub>TRACK(ofst)</sub> | TRACK pin offset voltage                                           |                                                                                                                                                                                               | -5   |                     | +5  | mV     |

| CURRENT S                | ENSE AMPLIFIER                                                     | -1                                                                                                                                                                                            |      |                     |     |        |

| I <sub>ISNS+</sub>       | ISNS+ bias current                                                 |                                                                                                                                                                                               |      |                     | 200 | nA     |

| I <sub>ISNS-</sub>       | ISNS- bias current                                                 |                                                                                                                                                                                               |      |                     | 100 | μA     |

| VICM                     | Input common mode range                                            |                                                                                                                                                                                               | 0.45 |                     | 15  | V      |

| AO <sub>CM</sub>         | Common mode gain                                                   |                                                                                                                                                                                               |      |                     | -80 | dB     |

| V <sub>LIN</sub>         | Input linear range, VISNS+ - VISNS- <sup>(5)</sup>                 |                                                                                                                                                                                               | -45  |                     | 110 | mV     |

| CURRENT L                | IMIT PROTECTION                                                    |                                                                                                                                                                                               |      |                     |     |        |

| t <sub>OFF</sub>         | Off time between restart attempts                                  |                                                                                                                                                                                               |      | 6 × t <sub>SS</sub> |     | ms     |

|                          | $V_{CS+} - V_{CS-}$ voltage that trips OC fault function           | Factory default settings <sup>(5)</sup> , T <sub>J</sub> = 25°C                                                                                                                               | 27   | 30                  | 33  | mV     |

|                          |                                                                    | $\begin{array}{l} 3 \hspace{0.1cm} V \leq V_{VDD} \leq 20 \hspace{0.1cm} V, \\ 30 \hspace{0.1cm} mV \leq V_{ILIMTH} \leq 110 \hspace{0.1cm} mV, \hspace{0.1cm} T_J = 25^{\circ}C \end{array}$ | -10% |                     | 10% |        |

| V <sub>ILIMTH</sub>      | Threshold accuracy                                                 | $\begin{array}{l} 3V \leq V_{VDD} \leq 20 \ V, \ V_{ILIMTH} \leq 30 \ mV, \\ T_J = 25^{\circ}C \end{array}$                                                                                   | -3   |                     | 3   | mV     |

|                          | Comparator offset                                                  | $V_{ILIMTH} = 30 \text{ mV}, T_J = 25^{\circ}\text{C}$                                                                                                                                        | -3   |                     | 3   | mV     |

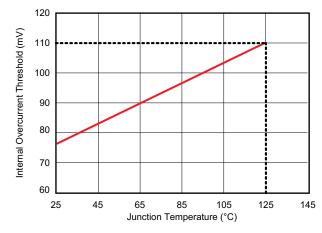

|                          | Temperature coefficient <sup>(4)</sup>                             |                                                                                                                                                                                               |      | 4000                |     | ppm/°0 |

| t <sub>DLYOC</sub>       | Overcurrent delay                                                  | 3-mV overdrive, $T_J = 25^{\circ}C$                                                                                                                                                           |      | 155                 |     | ns     |

|                          | $V_{\text{CS+}} - V_{\text{CS-}}$ voltage that sets warning status | Factory default settings, $T_J = 25^{\circ}C$                                                                                                                                                 | 12   | 15                  | 18  | mV     |

| V <sub>ILIMW</sub>       |                                                                    | $\begin{array}{l} 3 \hspace{0.1cm} V \leq V_{VDD} \leq 20V, \\ 1.9 \hspace{0.1cm} mV \leq V_{ILIMTH} \leq 120 \hspace{0.1cm} mV, \hspace{0.1cm} T_J = 25^{\circ}C \end{array}$                | -10% |                     | 10% |        |

|                          | Threshold accuracy                                                 | $\begin{array}{l} 3V \leq V_{VDD} \leq 20 \ V, \ V_{ILIMTH} < 30 \ mV, \\ T_J = 25^{\circ}C \end{array}$                                                                                      | -3   |                     | 3   | mV     |

|                          | Comparator offset                                                  | $V_{ILIMTH} = 20 \text{ mV},  \text{T}_{J} = 25^{\circ}\text{C}$                                                                                                                              | -3   |                     | 3   | mV     |

|                          | Temperature coefficient <sup>(4)</sup>                             |                                                                                                                                                                                               |      | 4000                |     | ppm/°C |

| t <sub>DLYOCW</sub>      | Overcurrent warning delay <sup>(4)</sup>                           | 3-mV overdrive                                                                                                                                                                                |      | 250                 |     | ns     |

See applications section for more information regarding soft-start time setting. (3)

(4) (5) Ensured by design. Not production tested.

The entire current ripple waveform must reside inside the linear range for current reading results to be accurate. DC current level must be zero or greater for accurate results. Current sense does not support applications that sink current. Transient voltages (such as ripple) are permitted to go below 0 V, but must be within the specified linear range.

**TPS40400** SLUS930B - APRIL 2011 - REVISED OCTOBER 2011

www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

#### Unless otherwise stated, these specifications apply for –40°C ≤ T<sub>J</sub> ≤ 125°C, V<sub>DD</sub>= 12 Vdc, FREQUENCY\_SWITCH = 600 kHz

|                        | PARAMETER                                     | TEST CONDITIONS                                                                               | MIN   | TYP   | MAX   | UNIT |

|------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------|-------|-------|-------|------|

| OUTPUT DR              | VERS                                          |                                                                                               |       |       |       |      |

| R <sub>HDHI</sub>      | High-side driver pull up resistance           | $ \begin{array}{l} (V_{BOOT}-V_{SW})=6.4~V,~I_{HDRV}=-100~,\\ T_{J}=25^{\circ}C \end{array} $ |       | 1.25  | 2.5   |      |

| R <sub>HDLO</sub>      | High-side driver pull down resistance         | $(V_{BOOT} - V_{SW}) = 6.4 \text{ V}, \text{ I}_{HDRV} = 100 \text{ mA},$<br>T_J = 25°C       |       | 1.3   | 2.6   | Ω    |

| R <sub>LDHI</sub>      | Low-side driver pull up resistance            | $T_J = 25^{\circ}C$                                                                           |       | 1.25  | 2.5   |      |

| R <sub>LDLO</sub>      | Low-side driver pull down resistance          | $T_J = 25^{\circ}C$                                                                           |       | 0.8   | 1.5   |      |

| t <sub>HRISE</sub>     | High-side driver rise time <sup>(6)</sup>     |                                                                                               |       | 6     | 12.1  |      |

| t <sub>HFALL</sub>     | High-side driver fall time (6)                |                                                                                               |       | 6.3   | 12.6  |      |

| t <sub>LRISE</sub>     | Low-side driver rise time <sup>(6)</sup>      | $-C_{LOAD} = 2.2 \text{ nF}$                                                                  |       | 6     | 12.1  | ns   |

| t <sub>LFALL</sub>     | Low-side driver fall time (6)                 |                                                                                               |       | 4     | 8     |      |

| t <sub>DT</sub>        | Anti-cross conduction time                    | MFR_SPECIFIC_00 bit 0 = 0,<br>(short dead time.)                                              | 20    |       | 50    | ns   |

| I <sub>SW</sub>        | SW pin leakage current (out of pin)           | V <sub>SW</sub> = 0 V                                                                         |       |       | 1     | μA   |

| BOOTSTRAF              |                                               |                                                                                               |       |       |       |      |

| V <sub>BOOT</sub>      | Internal diode voltage drop                   | I <sub>BOOT</sub> = 5 mA                                                                      |       | 0.7   | 1     | V    |

| I <sub>BOOT(lk)</sub>  | BOOT diode leakage current <sup>(6)</sup>     | $(V_{BOOT} - V_{SW}) = 6 V$                                                                   |       | 1     |       | μA   |

| UVLO                   |                                               |                                                                                               | 1     |       |       |      |

|                        | VDD UVLO turn on threshold <sup>(7)</sup>     | Factory default settings (minimum)                                                            | 2.475 | 2.750 | 3.025 |      |

| V <sub>UVLO(on)</sub>  | Accuracy <sup>(7)</sup>                       | 2.25 V $\leq$ V <sub>VDD</sub> $\leq$ 20 V,<br>2.75 V $\leq$ VIN_ON $\leq$ 18 V               | -10%  |       | 10%   | V    |

|                        | VDD UVLO turn off threshold <sup>(7)</sup>    | Factory default settings (minimum)                                                            | 2.25  | 2.5   | 2.75  |      |

| V <sub>UVLO(off)</sub> | Accuracy <sup>(7)</sup>                       | 2.25 V < V <sub>VDD</sub> < 20 V,<br>2.75 V < VIN_OFF < 17.6 V                                | -10%  |       | 10%   | V    |

| REMOTE VO              | LTAGE SENSE AMPLIFIER                         |                                                                                               |       |       |       |      |

| VIOFST                 | Input offset voltage                          |                                                                                               | -10   |       | 10    | mV   |

| R <sub>GAIN</sub>      | Gain setting resistor <sup>(6)</sup>          |                                                                                               | 48    | 60    | 72    | kΩ   |

| 0,111                  |                                               | V <sub>VDD</sub> > 6.5 V                                                                      | 0     |       | 6     |      |

| V <sub>DIFFO</sub>     | Output voltage at DIFFO pin                   | $V_{VDD} = 5 V$                                                                               | 0     |       | 4.5   | V    |

| DIITO                  |                                               | V <sub>VDD</sub> = 3 V                                                                        | 0     |       | 2.5   |      |

| K <sub>DIFF</sub>      | Differential gain of amplifier                |                                                                                               | 0.995 | 1.000 | 1.005 | V/V  |

| V <sub>AGBWP</sub>     | Closed loop bandwidth <sup>(6)</sup>          |                                                                                               | 2     |       |       | MHz  |

| IVAOP                  | Output source current                         | V <sub>SNS+</sub> = V <sub>DIFFO</sub> = 5 V, V <sub>SNS-</sub> = 0 V                         | 1     |       |       | mA   |

| IVAOM                  | Output sink current                           | $V_{SNS+} = 0 V, V_{SNS-} = 4.5 V, V_{DIFFO} = 5 V$                                           | 1     |       |       | mA   |

| POWERGOO               |                                               |                                                                                               |       |       |       |      |

|                        | FB pin voltage upper limit for power good on  |                                                                                               |       | 648   |       |      |

| V <sub>PGON</sub>      | FB pin voltage lower limit for power good on  | Factory default settings                                                                      |       | 552   |       | mV   |

|                        | Accuracy                                      | 540 mV < V <sub>PGON</sub> < 660 mV                                                           | -5%   | -     | 5%    |      |

|                        | FB pin voltage upper limit for power good off |                                                                                               |       | 660   | *     | mV   |

| V <sub>PGOFF</sub>     | FB pin voltage lower limit for power good off | Factory default settings                                                                      |       | 540   |       |      |

|                        | Accuracy                                      | 528 mV < V <sub>PGOFF</sub> < 672 mV                                                          | -5%   | -     | 5%    |      |

| R <sub>PGD</sub>       | Pull down resistance of PGD pin               | $V_{FB} = 0, I_{PGOOD} = 5 \text{ mA}$                                                        |       |       | 50    | Ω    |

| I <sub>PGDLK</sub>     | Leakage current                               | Factory default settings ,<br>550 mV < $V_{FB}$ < 650 mV, $V_{PGOOD}$ = 5 V                   | 3     |       | 15    | μA   |

|                        |                                               |                                                                                               |       |       |       |      |

(6) Ensured by design. Not production tested.

(7) Although specifications appear to overlap, hysteresis is assured for UVLO turn on and turn off thresholds.

SLUS930B - APRIL 2011 - REVISED OCTOBER 2011

www.ti.com

STRUMENTS

ÈXAS

# **ELECTRICAL CHARACTERISTICS (continued)**

## Unless otherwise stated, these specifications apply for $-40^{\circ}C \le T_J \le 125^{\circ}C$ , $V_{DD}= 12$ Vdc, FREQUENCY\_SWITCH = 600 kHz

|                       | PARAMETER                                               | TEST CONDITIONS                                                                                                | MIN  | TYP  | MAX   |     |  |

|-----------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|------|-------|-----|--|

|                       | LTAGE MARGINING                                         | L                                                                                                              |      |      |       |     |  |

|                       | VFB slope during margin voltage transition (8)          | Factory default settings                                                                                       | 250  | 214  | 188   | V/s |  |

| MRG <sub>SLP</sub>    | Accuracy                                                | $3 \text{ V} < \text{V}_{\text{VDD}} < 20 \text{ V}, 600 \ \mu\text{s} < \text{t}_{\text{SS}} < 9 \ \text{ms}$ | -15% |      | 15%   |     |  |

| V <sub>FBMH</sub>     | FB pin voltage after margin high command                | Factory default settings                                                                                       | 650  | 660  | 670   | mV  |  |

| V <sub>FBML</sub>     | FB pin voltage after margin low command                 | Factory default settings                                                                                       | 532  | 540  | 548   | mV  |  |

| V <sub>FBM(max)</sub> | Maximum FB pin voltage with Margin                      | –40°C < T <sub>J</sub> < 125°C                                                                                 | 742  | 750  | 758   | m∖  |  |

| V <sub>FBM(min)</sub> | Minimum FB pin voltage with Margin                      | –40°C < T <sub>J</sub> < 125°C                                                                                 | 445  | 450  | 455   | m∖  |  |

| V <sub>FB(inc)</sub>  | Resolution of FB steps with margin                      |                                                                                                                |      | 2.34 |       | m∖  |  |

| OVERVOLTA             | GE AND UNDERVOLTAGE DETECTION                           |                                                                                                                |      |      |       |     |  |

|                       | FB pin overvoltage threshold (OV flag)                  | Factory default settings                                                                                       | 638  | 672  | 705   |     |  |

| V <sub>OV</sub>       | Accuracy                                                | 3 V < V <sub>VDD</sub> < 20 V, 648 mV < V <sub>OV</sub> < 690 mV                                               | -5%  |      | 5%    | mV  |  |

|                       | FB pin undervoltage threshold (UV flag)                 | Factory default settings                                                                                       | 502  | 528  | 554   |     |  |

| V <sub>UV</sub>       | Accuracy                                                | 3 V < V <sub>VDD</sub> < 20 V,<br>510 mV < V <sub>OV</sub> < 552 mV                                            | -5%  |      | 5%    | m∨  |  |

| PMBus INTE            | RFACE                                                   |                                                                                                                |      |      |       |     |  |

| V <sub>IH</sub>       | High-level input voltage, CLK, DATA, CNTL               |                                                                                                                | 2.1  |      |       | V   |  |

| VIL                   | Low-level input voltage, CLK, DATA, CNTL                |                                                                                                                |      |      | 0.8   | V   |  |

|                       | High-level input current, CLK, DATA, CNTL               |                                                                                                                | -10  |      | 10    |     |  |

| н                     | CNTL                                                    |                                                                                                                | -12  |      | 10    | μA  |  |

|                       | Low-level input current, CLK, DATA, CNTL                |                                                                                                                | -10  |      | 10    |     |  |

| IL                    | CNTL                                                    |                                                                                                                | -12  |      | 10    | μA  |  |

| V <sub>OL</sub>       | Low-level output voltage, DATA, SMBALRT                 | $3.0 \text{ V} \leq \text{V}_{\text{VDD}} \leq 20 \text{ V}, \text{ I}_{\text{OUT}} = 2 \text{ mA}$            |      |      | 0.4   | V   |  |

| ОН                    | High-level open drain leakage current, DATA,<br>SMBALRT | V <sub>OUT</sub> = 3.6 V                                                                                       | 0    |      | 10    | μA  |  |

| Co <sup>(8)</sup>     | Pin capacitance, CLK, DATA                              |                                                                                                                |      | 0.7  |       | pF  |  |

| <sup>f</sup> PMB      | PMBus operating frequency range                         | Slave mode                                                                                                     | 10   |      | 400   | kHz |  |

| BUF                   | Bus free time between START and STOP $^{(8)}$           |                                                                                                                | 4.7  |      |       | μs  |  |

| HD:STA                | Hold time after repeated START <sup>(8)</sup>           |                                                                                                                | 4.0  |      |       | μs  |  |

| SU:STA                | Repeated START setup time <sup>(8)</sup>                |                                                                                                                | 4.7  |      |       | μs  |  |

| t <sub>su:sto</sub>   | STOP setup time <sup>(8)</sup>                          |                                                                                                                | 4.0  |      |       | μs  |  |

|                       | Data hold time <sup>(8)</sup>                           | Receive mode                                                                                                   | 0    |      |       |     |  |

| HD:DAT                |                                                         | Transmit mode                                                                                                  | 300  |      |       | ns  |  |

| SU:DAT                | Data setup time <sup>(8)</sup>                          |                                                                                                                | 250  |      |       | ns  |  |

| TIMEOUT               | Error signal/detect <sup>(8)</sup>                      |                                                                                                                | 25   |      | 35    | μs  |  |

| LOW:MEXT              | Cumulative clock low master extend time <sup>(8)</sup>  |                                                                                                                |      |      | 50    | μs  |  |

| LOW:SEXT              | Cumulative clock low slave extend time <sup>(8)</sup>   |                                                                                                                |      |      | 25    | μs  |  |

| LOW                   | Clock low time <sup>(8)</sup>                           |                                                                                                                | 4.7  |      |       | μs  |  |

| HIGH                  | Clock high time <sup>(8)</sup>                          |                                                                                                                | 4.0  |      |       | μs  |  |

| FALL                  | CLK/DATA fall time <sup>(8)</sup>                       |                                                                                                                |      |      | 300   | ns  |  |

| RISE                  | CLK/DATA rise time <sup>(8)</sup>                       |                                                                                                                |      |      | 1000  | ns  |  |

| PMBus ADD             | RESSING                                                 | · · · · · · · · · · · · · · · · · · ·                                                                          |      |      |       |     |  |

| ADD                   | ADDX pin current                                        |                                                                                                                | 8.23 | 9.75 | 11.21 | μA  |  |

| V <sub>ADD(L)</sub>   | Address pin illegal low voltage threshold               |                                                                                                                |      |      | 0.055 | V   |  |

(8) Ensured by design. Not production tested.

TPS40400 SLUS930B – APRIL 2011 – REVISED OCTOBER 2011

www.ti.com

## ELECTRICAL CHARACTERISTICS (continued)

Unless otherwise stated, these specifications apply for –40°C ≤ T<sub>J</sub> ≤ 125°C, V<sub>DD</sub>= 12 Vdc, FREQUENCY\_SWITCH = 600 kHz

|                            | PARAMETER                                                  | TEST CONDITIONS | MIN  | TYP    | MAX   | UNIT |  |  |

|----------------------------|------------------------------------------------------------|-----------------|------|--------|-------|------|--|--|

| MEASUREMENT SYSTEM         |                                                            |                 |      |        |       |      |  |  |

| t <sub>IDLY</sub>          | Read delay time <sup>(9)</sup>                             |                 | 153  | 192    | 231   | μs   |  |  |

| I <sub>RES</sub>           | Current measurement resolution (LSB) (10) (11)             |                 |      | 122    |       | μV   |  |  |

| I <sub>RNG</sub>           | Current measurement range <sup>(11)</sup> (12)             |                 | -45  |        | 110   | mV   |  |  |

| I <sub>ACC</sub>           | Gain accuracy <sup>(13)</sup>                              |                 | -3%  |        | 3%    |      |  |  |

| I <sub>OFST</sub>          | Offset                                                     |                 | -3   |        | 3     | mV   |  |  |

| V <sub>OUT(res)</sub>      | VOUT measurement resolution (LSB)                          |                 |      | 15.625 |       | mV   |  |  |

| V <sub>OUT(rng)</sub>      | VOUT voltage measurement range                             |                 | 0    |        | 14    | V    |  |  |

| V <sub>OUT(gain)</sub>     | Gain accuracy <sup>(13)(14)</sup>                          |                 | -2   |        | 2     | LSB  |  |  |

| V <sub>OUT(gain_adj)</sub> | Gain adjustment range through PMBus                        |                 | -10% |        | 10%   |      |  |  |

| V <sub>OUT(ofst)</sub>     | Offset <sup>(13)(14)</sup>                                 |                 | -3%  |        | 3%    |      |  |  |

| V <sub>OUT(ofst_adj)</sub> | Gain adjustment range through PMBus                        |                 | -125 |        | 124   | mV   |  |  |

| V <sub>IN(res)</sub>       | V <sub>IN</sub> measurement resolution                     |                 |      | 32.5   |       | mV   |  |  |

| V <sub>IN(rng)</sub>       | V <sub>IN</sub> voltage measurement range                  |                 | 3.0  |        | 20    | V    |  |  |

| V <sub>IN(gain)</sub>      | Gain accuracy <sup>(13)(14)</sup>                          |                 | -2%  |        | 2%    |      |  |  |

| V <sub>IN(gain_adj)</sub>  | Gain adjustment range through PMBus                        |                 | -10% |        | 10%   |      |  |  |

| V <sub>IN(offst)</sub>     | Offset <sup>(13)(14)</sup>                                 |                 | -5.5 | -2     | 1.4   | LSB  |  |  |

| V <sub>IN(offst_adj)</sub> | Offset adjustment range through PMBus                      |                 | -2   |        | 1.968 | V    |  |  |

| THERMAL SH                 | UTDOWN                                                     |                 | t    |        |       |      |  |  |

| T <sub>JSD</sub>           | Junction OT shutdown temperature <sup>(14)</sup>           |                 | 135  | 145    | 155   | °C   |  |  |

| T <sub>JSDH</sub>          | Shutdown hysteresis <sup>(14)</sup>                        |                 | 25   | 30     | 35    | °C   |  |  |

| T <sub>JWRN</sub>          | Junction OT warning threshold <sup>(14)</sup>              |                 | 120  | 130    | 140   | °C   |  |  |

| T <sub>JWRNH</sub>         | Junction OT warning temperature hysteresis <sup>(14)</sup> |                 | 15   | 20     | 25    | °C   |  |  |

(9) All read backs are an average of 16 consecutive measurements - not a rolling average. Time is a delay between parameter updates.

(10) Constrained by the resolution of READ\_IOUT command. This presents as the greater of 122 μV/ IOUT\_CAL\_GAIN or 62.5 mA, the resolution of the READ\_IOUT command

(11) Voltage is converted to current by dividing by IOUT\_CAL\_GAIN, the effective value of the resistance used to sense current in the application. Maximum amount that can be reported via PMBus is 64A.

(12) Current reading is only supported to 0 average. Voltage transients to -45mV are taken into account when computing this average.

(13) PMBus commands provide for calibration of each device on an individual basis for improved overall system accuracy.

(14) Ensured by design. Not production tested.

NSTRUMENTS

**EXAS**

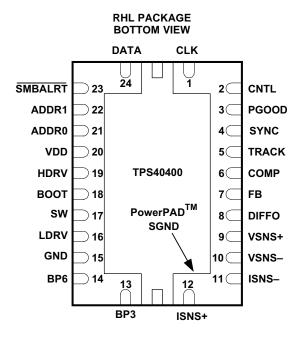

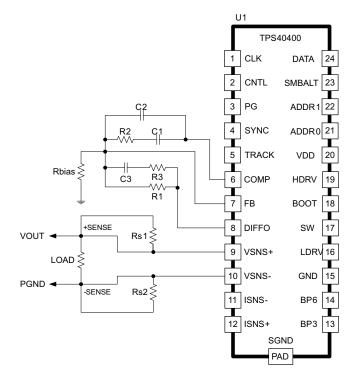

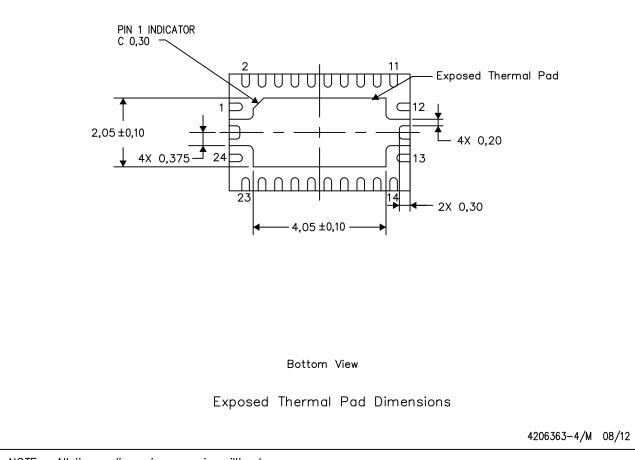

#### **DEVICE INFORMATION**

#### **PIN FUNCTIONS**

| PIN   |     | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                          |

|-------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                          |

| ADDR0 | 21  | Ι   | Low-order address pin for PMBus address configuration. One of eight resistor values must be connected from this pin to SGND to select the low-order octal digit in the PMBus address.                                                                                                                                                                |

| ADDR1 | 22  | I   | High-order address pin for PMBus address configuration. One of eight resistor values must be connected from this pin to SGND to select the high-order octal digit in the PMBus address.                                                                                                                                                              |

| BOOT  | 18  | Ι   | Gate drive voltage for the high-side N-channel MOSFET. A capacitor 100 nF typical must be connected between this pin and SW.                                                                                                                                                                                                                         |

| BP3   | 13  | 0   | Bypass pin for the internal regulator that supplies power to the internal controls of the device. Normal regulation voltage is 3.3 V. Connect a 100 nF or larger capacitor from this pin to GND.                                                                                                                                                     |

| BP6   | 14  | 0   | Bypass pin for the internal regulator that supplies power to the gate drivers. Normal regulation voltage is 6.5 V. Connect a 1-µF or larger capacitor from this pin to GND.                                                                                                                                                                          |

| CLK   | 1   | Ι   | Clock input for the PMBus interface                                                                                                                                                                                                                                                                                                                  |

| CNTL  | 2   | I   | Logic level input that controls the startup and shutdown of the converter, Exact functionality is determined by PMBus options.                                                                                                                                                                                                                       |

| COMP  | 6   | 0   | Output of the error amplifier. Used for control loop compensation.                                                                                                                                                                                                                                                                                   |

| DATA  | 24  | I/O | Data I/O for the PMBus interface                                                                                                                                                                                                                                                                                                                     |

| DIFFO | 8   | 0   | Output of the unity gain remote voltage sense amplifier. Typically connected to the voltage divider on FB                                                                                                                                                                                                                                            |

| FB    | 7   | Ι   | Inverting input to the error amplifier. A voltage divider is connected here to sense the output voltage.                                                                                                                                                                                                                                             |

| GND   | 15  | -   | Common connection for the device. This pin should connect to the thermal pad under the device package and to the power stage ground, preferably close to the source of the Low-side or rectifier FET. Connections should be arranged so that no power level current slow across the pad connected to the thermal pad on the underside of the device. |

| HDRV  | 19  | 0   | Gate drive signal to the high-side FET                                                                                                                                                                                                                                                                                                               |

| ISNS- | 11  | Ι   | Inverting input to the current sense amplifier                                                                                                                                                                                                                                                                                                       |

| ISNS+ | 12  | Ι   | Non-inverting input to the current sense amplifier                                                                                                                                                                                                                                                                                                   |

| LDRV  | 16  | 0   | Output used to drive the gate of the low-side or rectifier FET.                                                                                                                                                                                                                                                                                      |

| PGOOD | 3   | 0   | Power good output. This is an open drain output that pulls low when any fault condition exists within the device or when the device is not operating within a user selectable operating range of the nominal output voltage of the converter.                                                                                                        |

# PIN FUNCTIONS (continued)

| PIN     |     | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SGND    | PAD | -   | Signal ground for the controller. Connect the ground of signal level circuits to this pin. Connections should be arranged so that power level currents do not flow in the pad attached to the thermal plane or in the SGND portion of the circuit.                                                                                                                                                                                                         |

| SMBALRT | 23  | 0   | Output used to signal that PMBus host that the controller needs attention.                                                                                                                                                                                                                                                                                                                                                                                 |

| SW      | 17  | Ι   | This is the common connection for the flying high-side FET driver and also serve as a sense line for the adaptive anti-cross-conduction circuitry                                                                                                                                                                                                                                                                                                          |

| SYNC    | 4   | Ι   | Logic level input to the oscillator inside the controller. The oscillator resets on the rising edge of a pulse train applied to this pin and begin a new switching cycle.                                                                                                                                                                                                                                                                                  |

| TRACK   | 5   | I   | Analog input to the non inverting side of the control loop error amplifier. The error amplifier has three inputs (voltage reference, TRACK and soft-start ramp) to it's "+" side, and the lowest voltage applied to these three inputs dominate and control the output voltage of the whole converter. This pin is to allow the user to configure a voltage divider that allows the controller output follow an external reference voltage during startup. |

| VDD     | 20  | Ι   | Input power connection for the device. 3.0 V to 20 V required.                                                                                                                                                                                                                                                                                                                                                                                             |

| VSNS+   | 9   | Ι   | Non-inverting input to the unity gain remote voltage sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                      |

| VSNS-   | 10  | Ι   | Inverting input to the unity gain remote voltage sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                          |

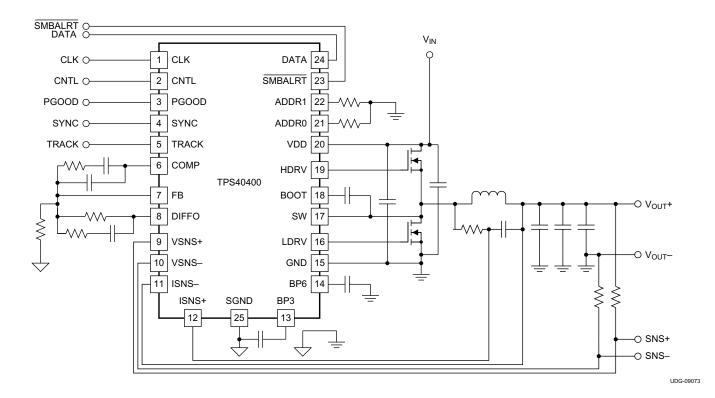

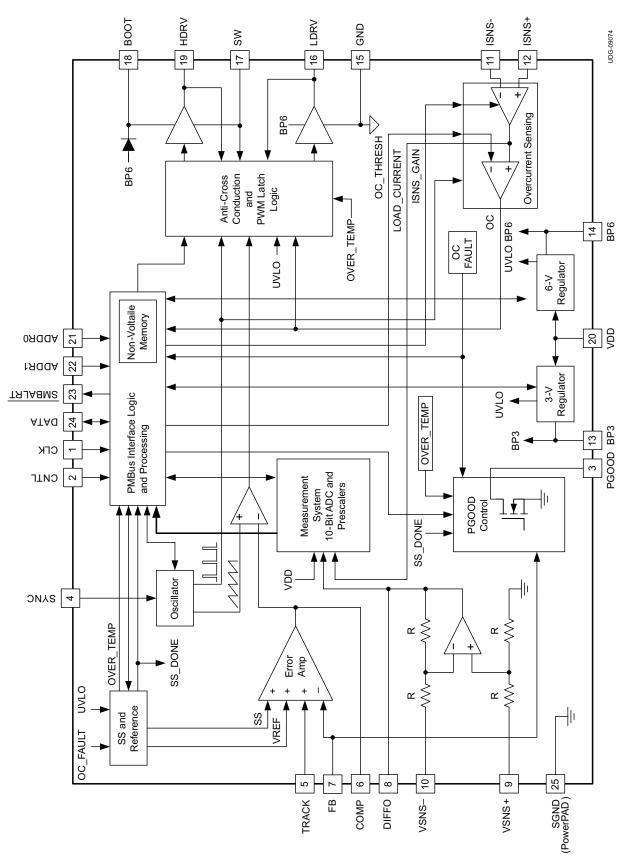

FUNCTIONAL BLOCK DIAGRAM

www.ti.com

TEXAS INSTRUMENTS

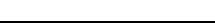

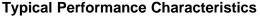

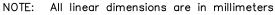

**TYPICAL CHARACTERISTICS**

Figure 6. TRACK Pin Offset Voltage vs. Junction Temperature

vs. Junction Temperature

SLUS930B-APRIL 2011-REVISED OCTOBER 2011

**INSTRUMENTS**

Texas

## TPS40400 SLUS930B – APRIL 2011 – REVISED OCTOBER 2011

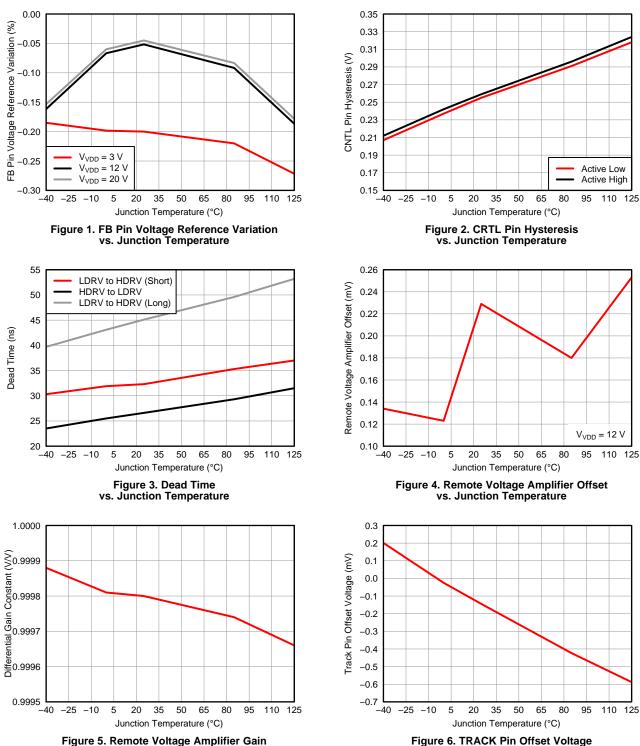

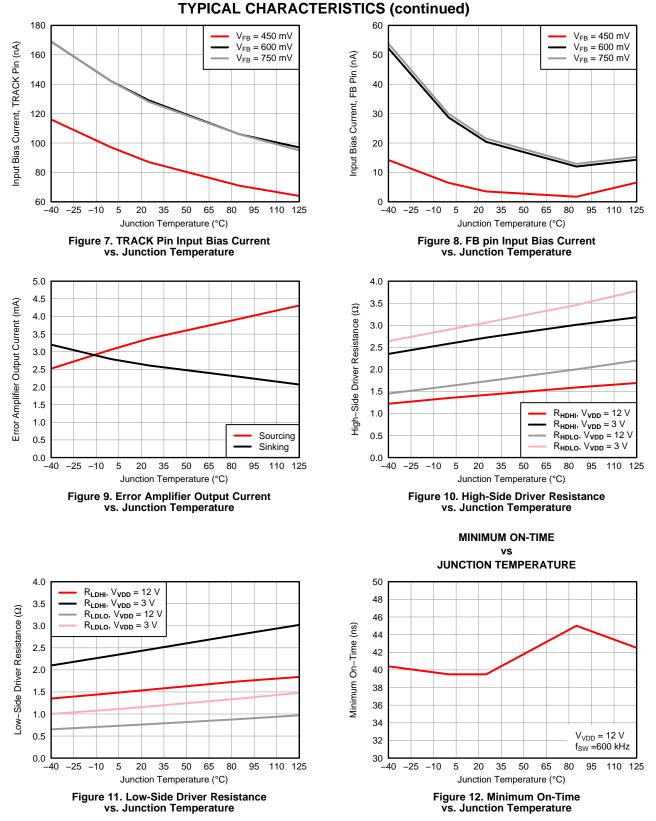

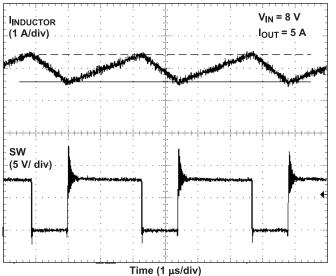

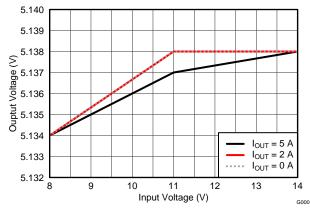

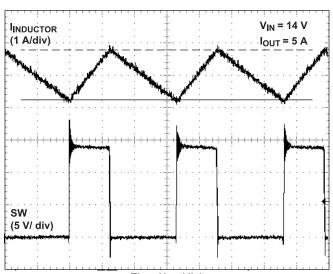

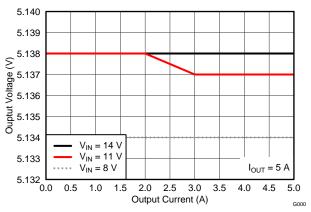

**TYPICAL CHARACTERISTICS (continued)**

# **APPLICATION INFORMATION**

#### **PMBus**

#### **General Description**

Timing and electrical characteristics of the PMBus can be found in the PMB Power Management Protocol Specification, Part 1, revision 1.1 available at <a href="http://pmbus.org">http://pmbus.org</a>. The TPS40400 supports both the 100 kHz and 400 kHz bus timing requirements. The TPS40400 does not stretch pulses on the PMBus when communicating with the master device.

Communication over the TPS40400 device PMBus interface can either support the Packet Error Checking (PEC) scheme or not. If the master supplies CLK pulses for the PEC byte, it is used. If the CLK pulses are not present before a STOP, the PEC is not used.

The TPS40400 supports a subset of the commands in the PMBus 1.1 specification. Most all of the controller parameters can be programmed using the PMBus and stored as defaults for later use. All commands that require data input or output use the literal format. The exponent of the data words is fixed at a reasonable value for the command and altering the exponent is not supported. Direct format data input or output is not supported by the TPS40400. See the SUPPORTED COMMANDS section for specific details.

The TPS40400 also supports the SMBALERT response protocol. The SMBALERT response protocol is a mechanism by which a slave (the TPS40400) can alert the bus master that it wants to talk. The master processes this event and simultaneously accesses all slaves on the bus (that support the protocol) through the alert response address. Only the slave that caused the alert acknowledges this request. The host performs a modified receive byte operation to get the slave's address. At this point, the master can use the PMBus status commands to query the slave that caused the alert. For more information on the SMBus alert response protocol, see the System Management Bus (SMBus) specification.

The TPS40400 contains non-volatile memory that is used to store configuration settings and scale factors. The settings programmed into the device are not automatically saved into this non-volatile memory though. The STORE\_DEFAULT\_ALL command must be used to commit the current settings to non-volatile memory as device defaults. The settings that are capable of being stored in non-volatile memory are noted in their detailed descriptions.

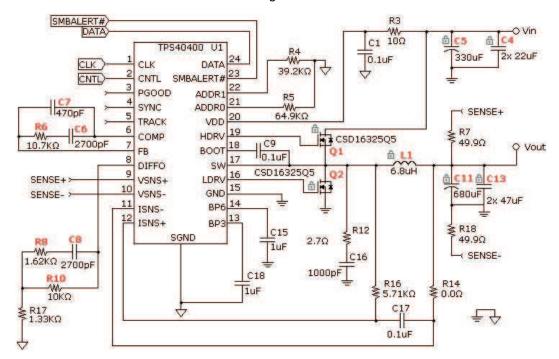

#### Setting up the Controller – Hardware Connections

The TPS 40400 is an analog controller, meaning that it uses traditional analog circuitry to control the output of the converter. Many of the operating parameters are set using the PMBus interface. This section describes how to set the controller parameters in an application.

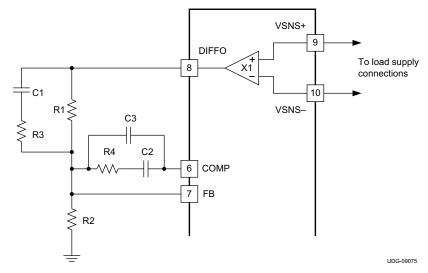

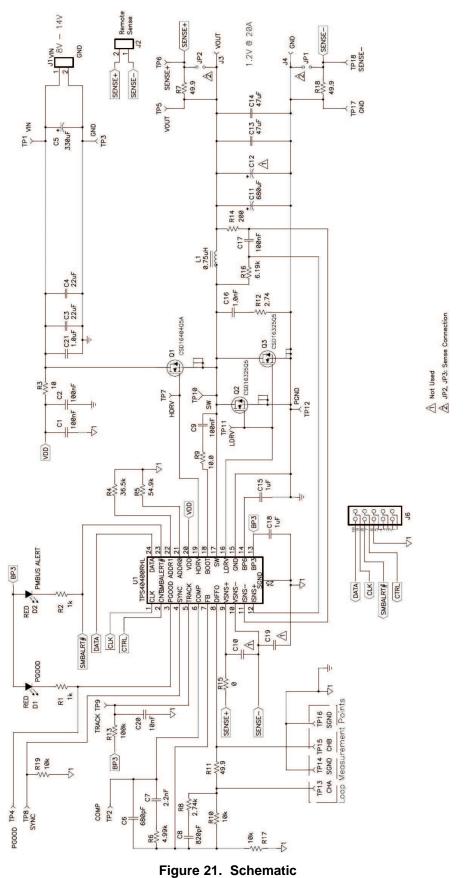

**Output voltage.** The output voltage is set in a very similar to the way to a traditional analog controller using a voltage divider from the output to the feedback (FB) pin. The output voltage must be divided down to the nominal reference voltage of 600mV. Figure 17 shows the typical connections for the controller. The voltage at the load can be sensed using the unity gain differential voltage sense amplifier. This provides better load regulation for output voltages lower than 5V nominal (see electrical specifications for the maximum output voltage directly to the differential sense amplifier). For output voltages above this level, connect the output voltage directly to the junction of R1 and C1, leave DIFFO open do not connect the VSNS inputs to the output voltage. In this case, it is also recommended to connect VSNS+ to BP3 and VSNS- to GND. If desired the differential amplifier may also be used elsewhere in the overall system as a voltage buffer provided the electrical specifications are not exceeded

Figure 17. Setting the Output Voltage

The components in Figure 17 that determine the nominal output voltage are R1 and R2. R1 is normally chosen to make the feedback compensation values (R3, R4, C1, C2 andC3) come close to readily available standard values. R2 is then calculated in Equation 1.

$$R2 = V_{FB} \times \left(\frac{R1}{\left(V_{OUT} - V_{FB}\right)}\right)$$

where

- V<sub>FB</sub> is the feedback voltage

- V<sub>OUT</sub> is the desired output voltage

- R1 and R2 are in the same units

(1)

The feedback voltage can be changed  $\pm 25\%$  from the nominal 600mV using PMBus commands. This allows the output voltage to vary by the same percentage. See the PMBus Functionality and Additional Setup section for further details. Once the output voltage is set and the values of R1 and R2 are known, the VOUT\_SCALE LOOP parameter can be calculated. This parameter is required for the PMBus interface to function properly when making output voltage adjustments.

**Voltage feed forward.** The TPS40400 has input voltage feed forward that maintains a constant power stage gain as input voltage varies and provides for very good response to input voltage transient disturbances. The simple constant power stage gain of the controller greatly simplifies feedback loop design because loop characteristics remains constant as the input voltage changes, unlike a buck converter without voltage feed forward. For modeling purposes, the gain from the COMP pin to the average voltage at the input of the L-C filter is 6V/V.

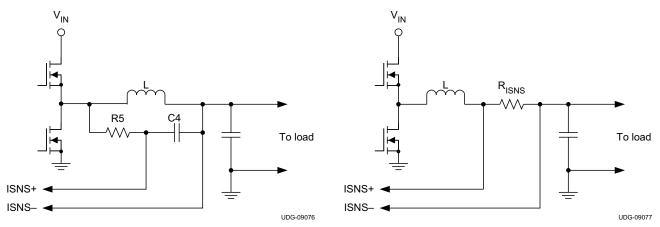

**Output current limit and warning.** The TPS40400 uses a differential current sense scheme to sense the output current. The sense element can be either the series resistance of the power stage filter inductor or a separate current sense resistor. When using the inductor series resistance as in Figure 18, a filter must be used to remove the large AC component of voltage across the inductor and leave only the component of the voltage that appears across the resistance of the R-C filter should be equal to or greater than the time constant of the inductor itself. If the time constants are equal, the voltage appearing across C4 is be the current in the inductor multiplied the inductor resistance. The inductor ripple current is reflected in the voltage across C4 perfectly in this case and there is no reason to have a shorter R-C time constant. The time constant of the R-C filter can be made longer than the inductor time constant because this is a voltage mode controller and the current sensing is done for overcurrent detection and output current reporting only. Extending the R-C filter time constant beyond the inductor time constant lowers the AC ripple component of voltage present at the ISNS pins of the TPS40400 but leaves the correct DC current information intact. This also delays slightly the response to an overcurrent event, but reduces noise in the system leading to cleaner overcurrent performance and current reporting data over the PMBus

TPS40400 SLUS930B – APRIL 2011– REVISED OCTOBER 2011

www.ti.com

**INSTRUMENTS**

FXAS

$$R5 \times C4 \ge \left(\frac{L}{R_{ESR}}\right)$$

where (from Figure 18)

- R5 and  $R_{ESR}$  are in  $\Omega$

- C4 is in F (suggest 100 nF, 10<sup>-7</sup>F)

- Lisin H

(2)

The maximum voltage that the TPS40400 is designed to accept across the ISNS pins is 110 mV. Because most all inductors have a copper conductor and because copper has a fairly large temperature coefficient of resistance, the resistance of the inductor and the current through the inductor should make a DC voltage less than 110 mV when the inductor is at the maximum temperature for the converter. This also applies for the external resistor in Figure 19. The full load output current multiplied by the sense resistor value, must be less that 110 mV at the maximum converter operating temperature.

There is also a constraint on the negative (reverse current) voltage that can be applied to the ISNS pins of the TPS40400. The voltage differential from ISNS+ to ISNS- should not be less than -45 mV. If this condition is not met, inaccurate results from the READ\_IOUT command is the result. This is intended to be a ripple voltage limitation. The net current through the inductor must flow towards the load from the input voltage. Current sinking, while possible for the controller to accommodate, is not supported for overcurrent detection or for the READ\_IOUT command.

In all cases, C4 should be placed as close to the ISNS pins as possible to help avoid problems with noise.

Figure 18. Current Sensing Using Inductor Resistance

Figure 19. Current Sensing Using Sense Resistor

Once the current sensing method is chosen, the TPS40400 needs to be told what the resistance of the current sense element is. This allows the proper calculation of thresholds for the overcurrent fault and warning, as well as more accurate reporting of the actual output current. The IOUT\_CAL\_GAIN command is used to set the value of the sense element resistence of the device. IOUT\_OC\_WARN\_LIMIT and IOUT\_OC\_FAULT\_LIMIT set the levels for the overcurrent warning and fault levels respectively. (See the PMBus Functionality and Additional Setup section for more details.)

**Linear regulators.** The TPS40400 has two on board linear regulators primarily intended to provide suitable power for the internal circuitry of the device. These pins, BP3 and BP6 must be properly bypassed to function properly. BP3 needs a minimum of 100nF connected to GND and BP6 should have approximately  $1\mu$ F connected to GND.

It is permissible to use the external regulator to power other circuits if desired, but care must be taken to ensure that the loads placed on the regulators do not adversely affect operation of the controller. The main consideration is to avoid loads with heavy transient currents that can affect the regulator outputs. Transient voltages on these outputs could result in noisy or erratic operation of the TPS40400.

Current limits must also be observed. Shorting the BP3 pin to GND damages the BP3 regulator. The BP3 regulator input comes from the BP6 regulator output. The current limit circuit on the BP6 regulator is 100 mA so the total current drawn from both regulators must be less than that. This total current includes the TPS40400 operating current  $I_{VDD}$  plus the gate drive current required to drive the power FETs. The total available current from two regulators is found in Equation 3 and Equation 4:

$$I_{\text{LIN}} = I_{\text{BP6}} - (I_{\text{VDD}} + I_{\text{GATE}})$$

$$I_{GATE} = f_{SW} \times \left( Q_{gHIGH} + Q_{gLOW} \right)$$

where