# FEX System ATCA Hub Module: FDR Follow-up

Hub Team Michigan State University

10 December 2018

### Hub Production Plan:

- Hub production run will be 20 cards, no pre-production run is planned.

- Goal: Delivery to CERN by June 2019. More on this in the next presentation(s).

- Hub PRR Goals:

- Action items identified during FDR will be reviewed.

- Additional tests beyond those identified at FDR will be presented for review.

- Firmware aspects directly impacting hardware function, performance and capability will be presented for review.

- If no hardware issues are identified during the PRR, production PCBs will be scheduled for manufacture.

- be scheduled.

### **Today's Presentation Material:**

- Introduction and follow-up of FDR action items This talk:

- Next talk:

- Last talk: Hub production schedule and scope

## **Overview & Goals**

If any hardware-sensitive firmware issues are identified during the PRR, a post-PRR review will

If/when the PRR and any follow-ups are passed, Hub production modules will be assembled.

Review of "beyond FDR" Hub test results & firmware implementation

# **Outline of this Presentation**

## Introductory & background material

Very brief review & status

### Description of Hub test apparatus

Primary source of test data for this review

- Follow-up responses to Final Design Review action items Clock generation and distribution

- Firmware items

- Remaining hardware items

### Many years of experience on the MSU team

- Dan Edmunds, EE

- Yuri Ermoline, EE

- Brian Ferguson, EE

- Philippe Laurens, EE

- Pawel Plucinski, PhD

- Spencer Lee, student

- Kuan Yu Lin, student

- Gabriel Moreau, student

- Wade Fisher, faculty

## Hub Team

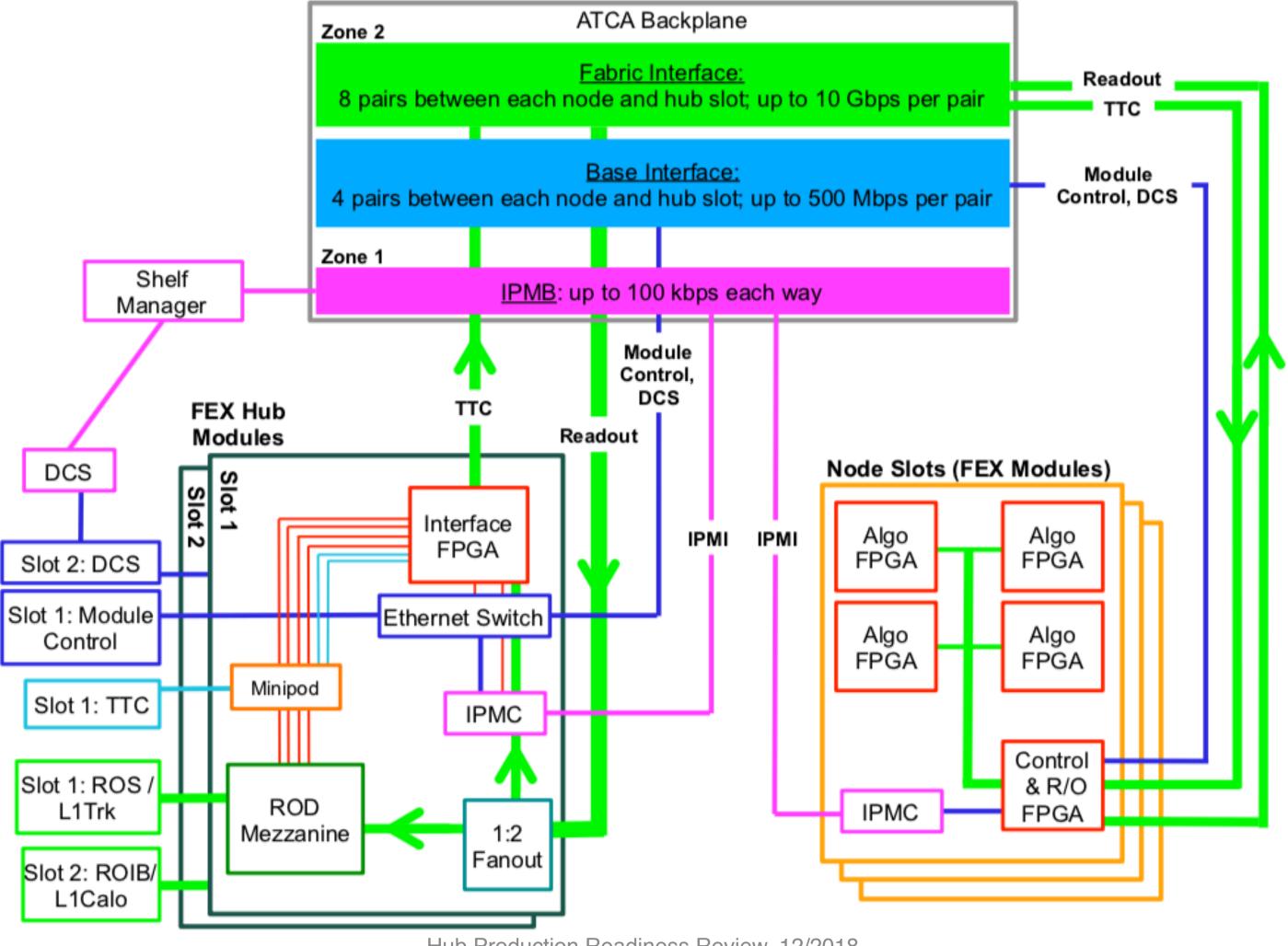

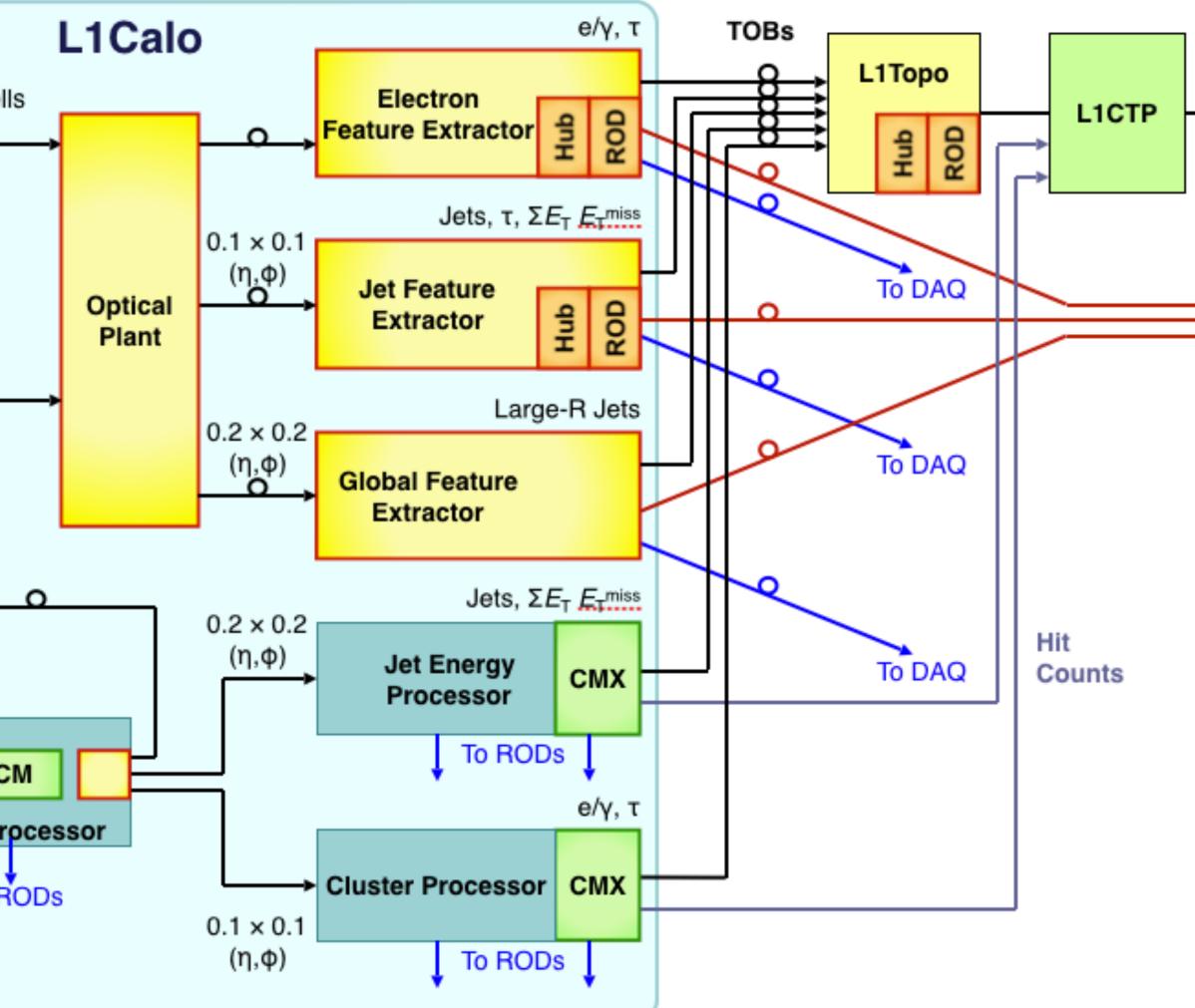

### FEX ATCA Hub module provides a readout interface for L1Calo trigger electronics

## Introduction

| <ol> <li>eFEX Modules, 2 shelves</li> <li>jFEX Modules, 1 shelf</li> </ol>                                                                                                              | LAr<br>(digital)                        | supercells<br>O |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------|

| <ol> <li>L1Topo Modules, 1 shelf</li> <li>ROD Mezzanine, 1 per Hub</li> <li>DAQ/HLT [FELIX]         <ul> <li>TTC</li> </ul> </li> </ol>                                                 |                                         |                 |

| <ul> <li>b) ROD-busy LEMO</li> <li>6. Ethernet <ul> <li>a) DCS</li> <li>b) Run control</li> </ul> </li> <li>7. IPMC</li> <li>8. Board-level <ul> <li>a) JTAG/I2C</li> </ul> </li> </ul> | LAr<br>(analogue)<br>Tile<br>(analogue) | nMCN<br>Pre-pro |

## **External Interfaces**

## **Board Layout**

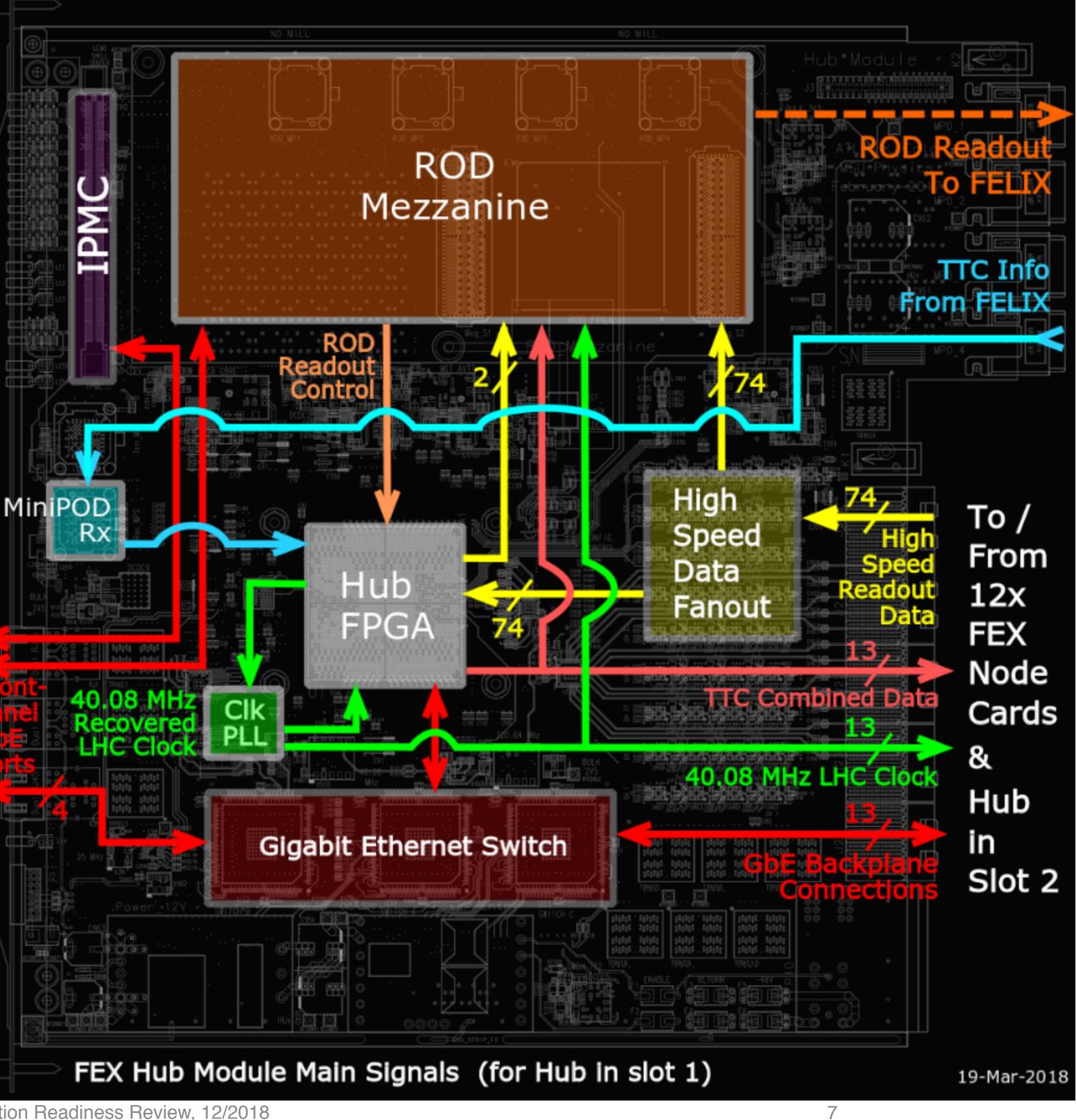

### Core functions of the Hub hardware

- Host the ROD Mezzanine 1)

- Aggregate Zone-2 FEX readout data and 2) provide to the ROD

- 3) Distribute LHC master clock to FEX, Hub and ROD modules

- Distribute TTC and ROD control data to 4) FEX, Hub and ROD modules

- 5) Provide Ethernet switch for the ATCA shelf via the Base Interface

Hub Production Readiness Review, 12/2018

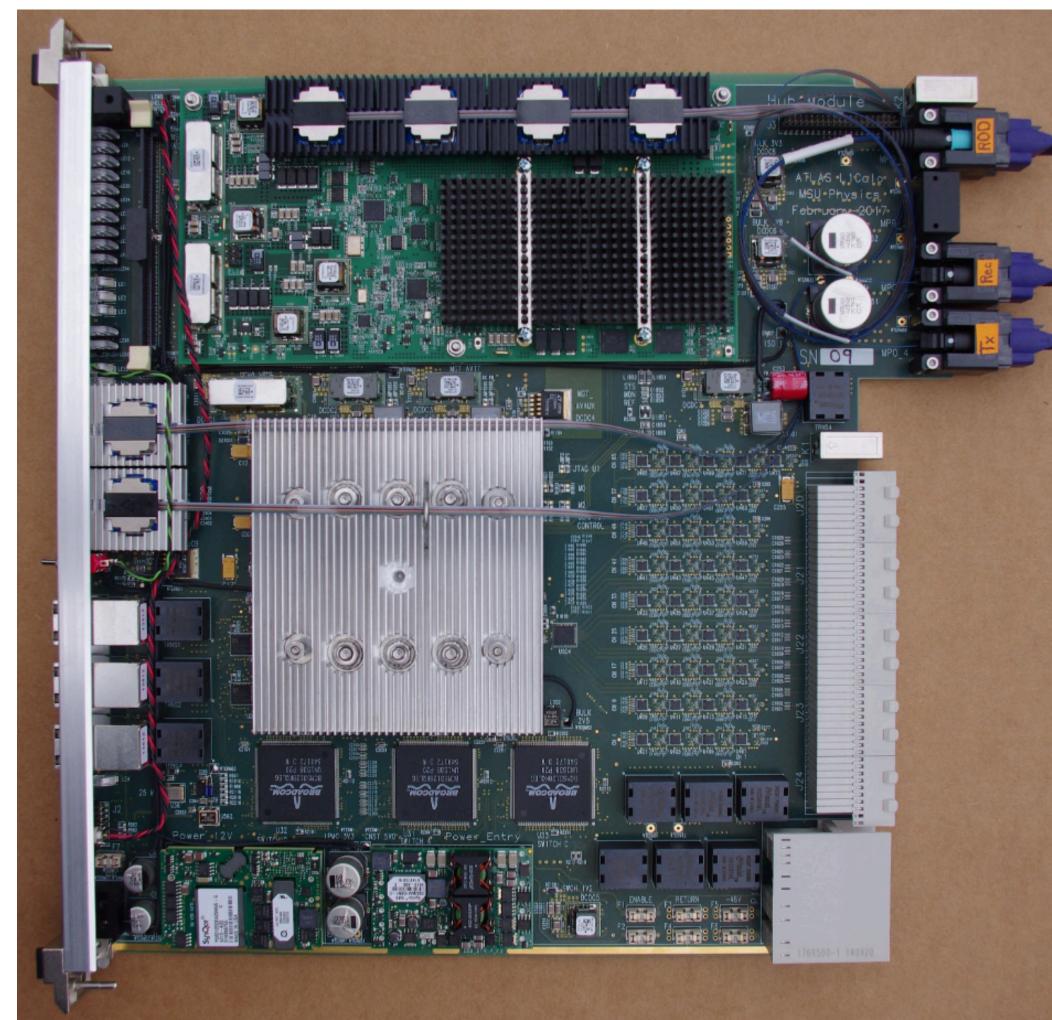

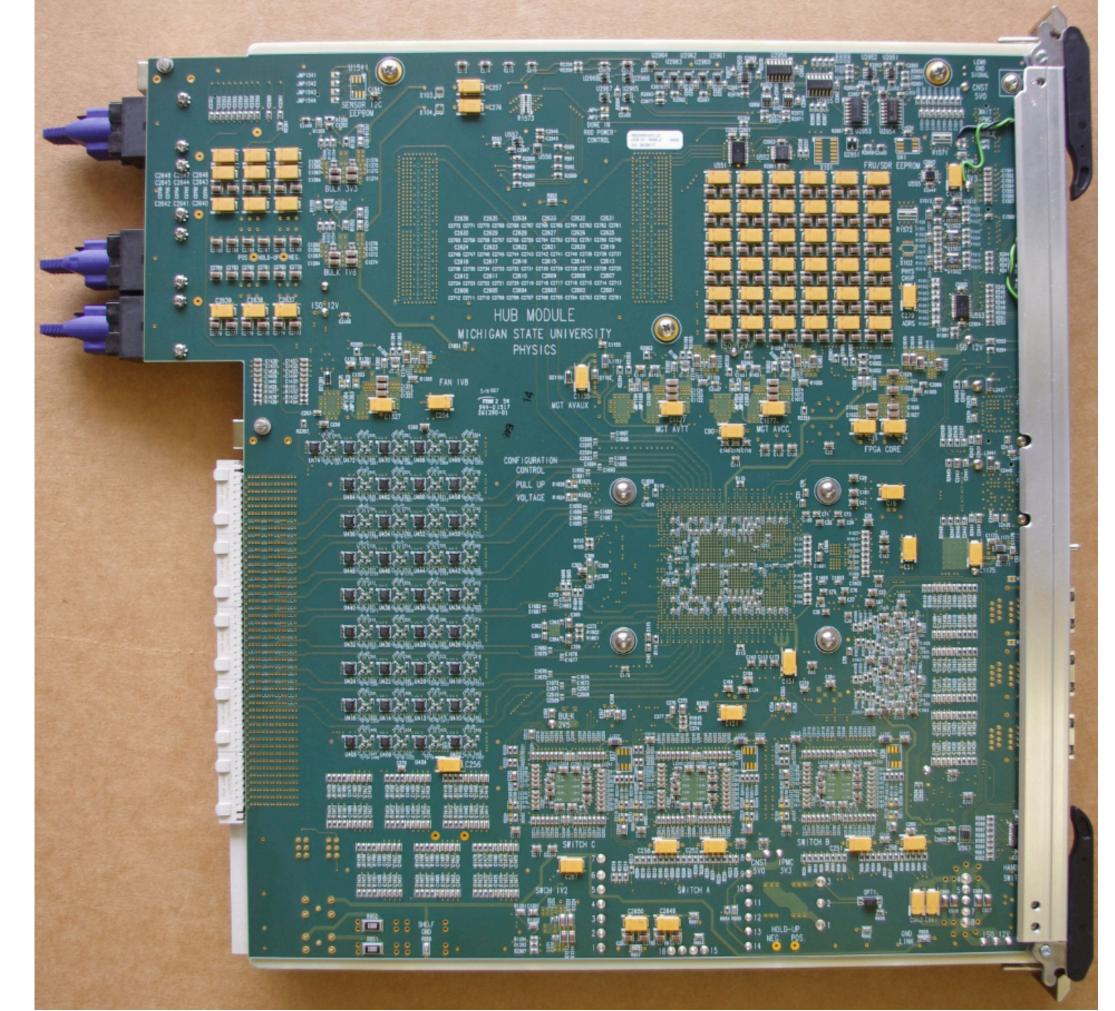

### 9 Hub prototypes were build (8 with FPGAs)

W. Fisher, MSU

# Prototype Hub Modules

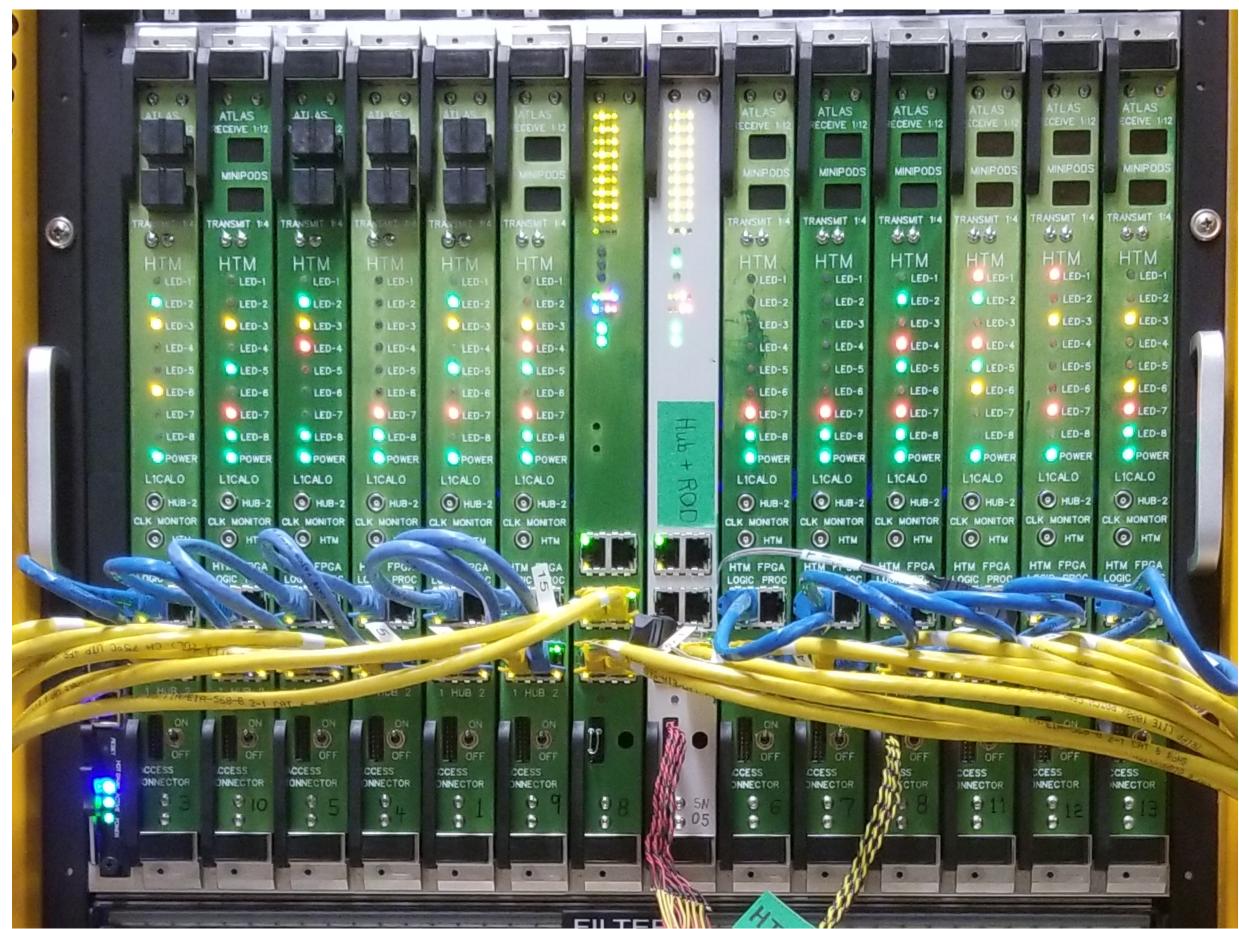

Here: Hub S/N 09 with ROD and optical cabling included to illustrate final installation assembly.

# Hub Firmware

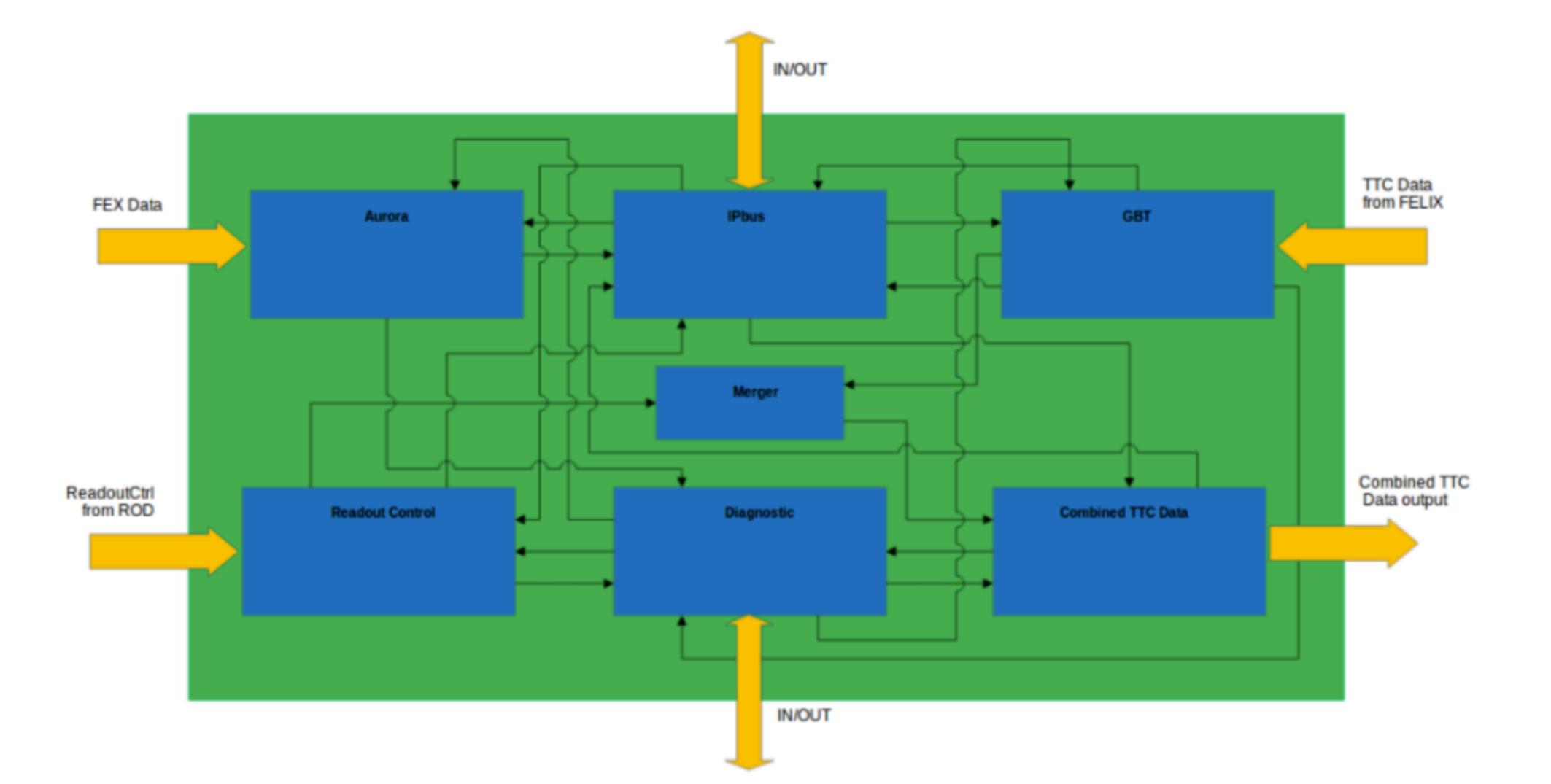

### There are four core firmware requirements for the Hub module ROD power-up and control data interfaces 1)

- TTC/GBT clock recovery and distribution 2)

- TTC/Combined data distribution 3)

- IPbus interfaces for ROD & Hub functionality 4)

- These functions will be described both here and in the Hub firmware specification

- Details pertinent to the Hub FDR will be in this presentation

- Details related to Hub production readiness in the second presentation Allowing to focus on specifics of the FDR action items in this presentation

- Hub hardware details

- Specification: Very minor language changes relative to what was presented at the FDR

- No relevant changes to the Hub PCB or other hardware aspects.

- Ο

- PCB Stackup: No changes WRT what was shown at the FDR

- PLL Chip data sheet: No changes WRT what was shown at the FDR

### Hub firmware specification

- Significant overhaul since FDR

- New descriptions of core Hub firmware

- Details of firmware implementation

- Focus on external interfaces, includes internal details

- Hub GbE test reports

- Full details of Hub GbE switch tests

- Links to MSU L1Calo webpages

- All the details of the build, test results, etc

- https://web.pa.msu.edu/hep/atlas/l1calo/

- Links for Hub and HTM can be found there Ο

## **Review Documentation**

We did swap out our green indicator LEDs for LEDs with lower light intensity, allowing for better reading of dense switch status LED patterns.

# Hub Test Apparatus

W. Fisher, MSU

Hub Production Readiness Review, 12/2018

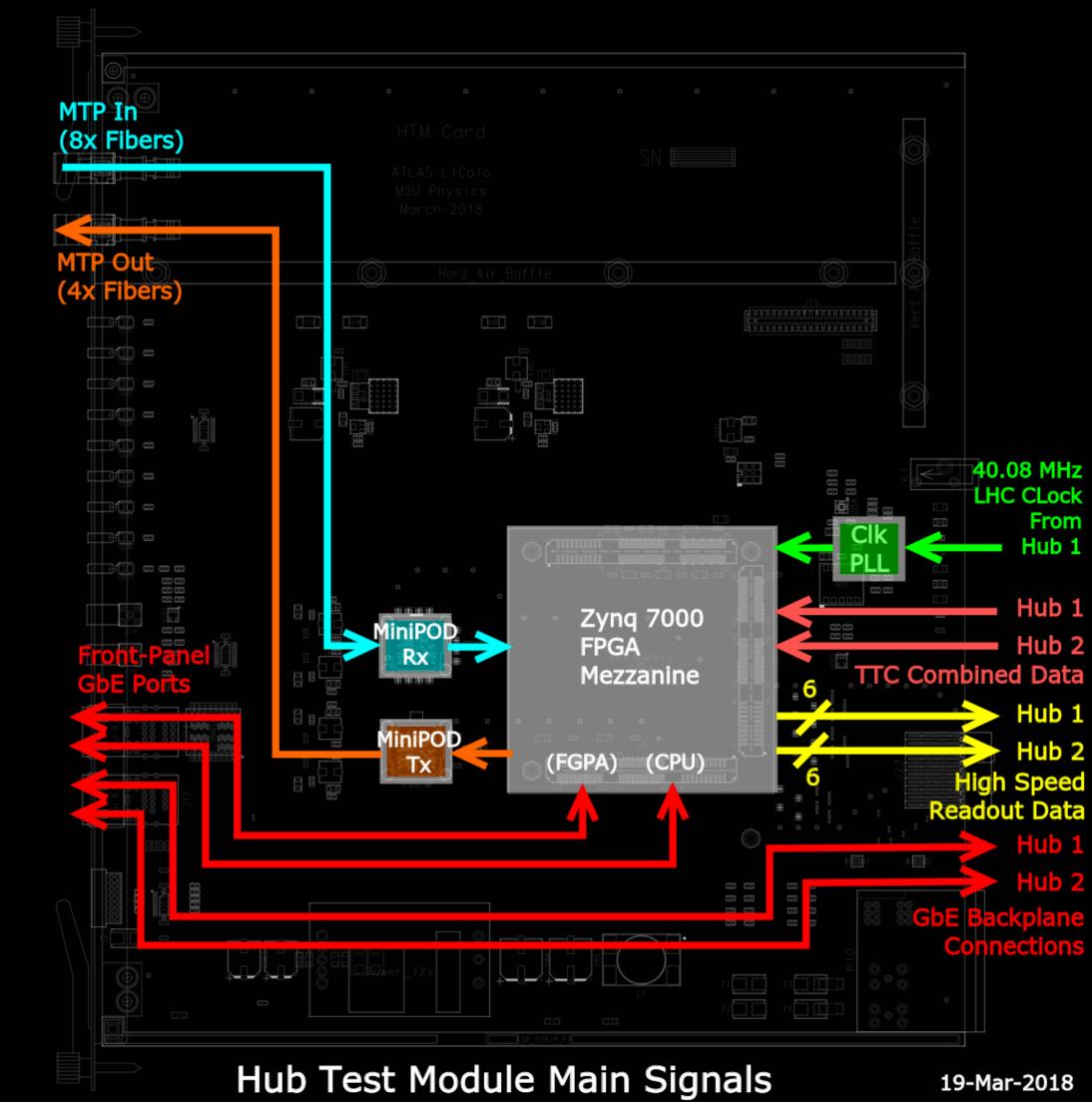

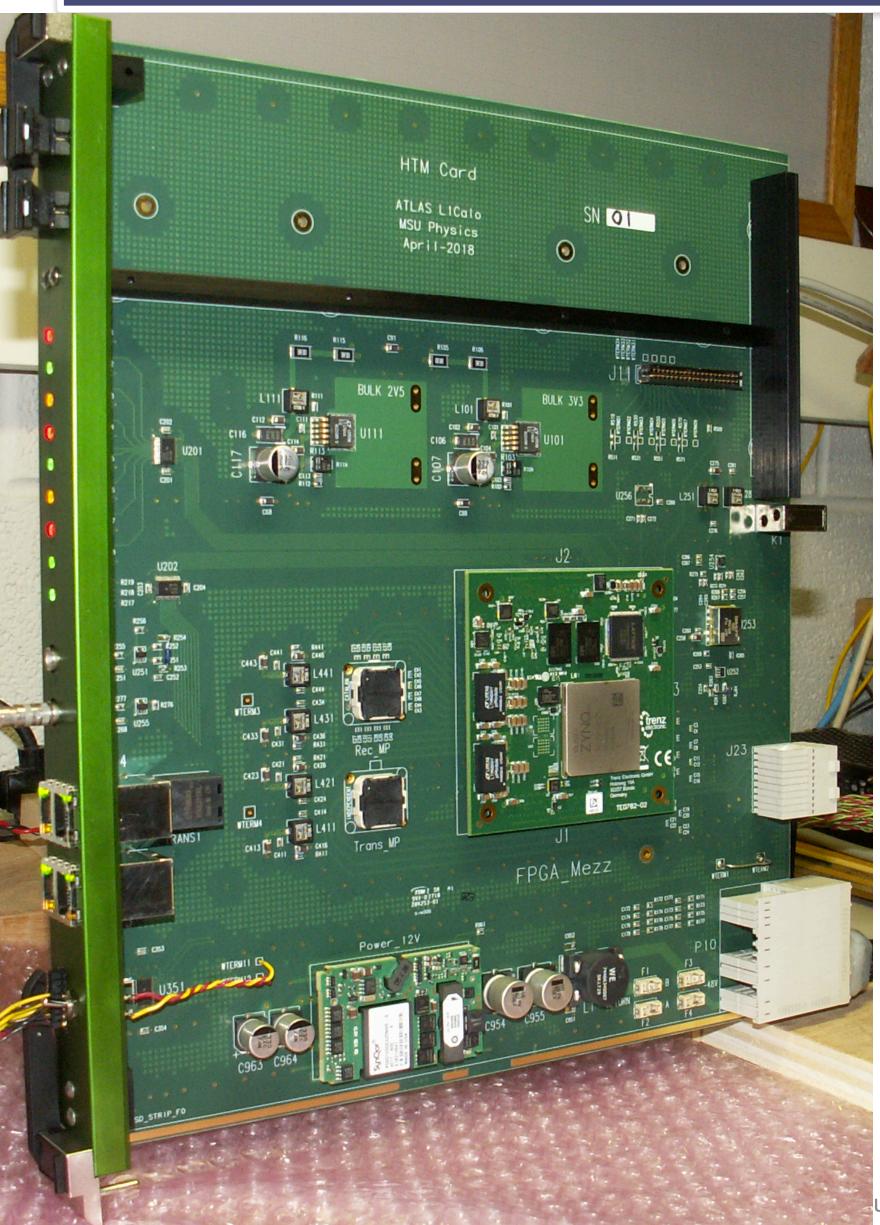

# Hub Test Module

W. Fisher, MSU

### Hub Test Module (HTM) designed to allow full system tests \* far in advance of a full shelf of FEX/FTM cards

Developed at MSU. 20 cards delivered July 2018.

### HTM design specifics \*

- ATCA form factor, 10 layer board

- Hosts a commercial mezzanine card with a 7-series Zynq

- Receives Hub TTC & clock via Zone-2

- Sources 6 lanes of "FEX" data to each Hub slot, up to 10.26 Gbps

- Optional MiniPods to emulate all Hub/ROD optical interfaces

- Connections to both Hub GbE networks

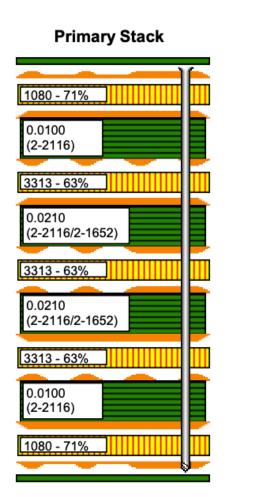

Viasystems Technologies Corp. LLC 8150 Sheppard Ave E Toronto, ON, M1B 5K2

Job Name : 181875 Customer : DEBRON INDUSTRIAL ELECTRONICS Part Num: 40-00643-00LF Part Rev : -Engineer : Yogi Perin

| Layer      | Cust<br>Thickness | Calc<br>Thickness          |

|------------|-------------------|----------------------------|

| Layer - 1  |                   | 0.0005<br>0.0020           |

| Layer - 2  |                   | 0.0038<br>0.0006           |

| Layer - 3  |                   | 0.0100<br>0.0006           |

| Layer - 4  |                   | 0.0040                     |

| -          |                   | 0.0210                     |

| Layer - 5  |                   | 0.0012<br>0.0034           |

| Layer - 6  |                   | 0.0012<br>0.0210           |

| Layer - 7  |                   | 0.0006<br>0.0040           |

| Layer - 8  |                   | 0.0006                     |

| Layer - 9  |                   | 0.0100<br>0.0006           |

| Layer - 10 |                   | 0.0038<br>0.0020<br>0.0005 |

|            |                   |                            |

| Primary Stack             |  |

|---------------------------|--|

| 1080 - 71%                |  |

| 0.0100<br>(2-2116)        |  |

| 3313 - 63%                |  |

| 0.0210<br>(2-2116/2-1652) |  |

| 3313 - 63%                |  |

| 0.0210<br>(2-2116/2-1652) |  |

| 3313 - 63%                |  |

| 0.0100<br>(2-2116)        |  |

| 1080 - 71%                |  |

| <b>Dk / Df</b><br>3.50 / 0.0190 |

|---------------------------------|

| 3.42 / 0.0098                   |

| 3.69 / 0.0089                   |

| 3.48 / 0.0096                   |

| 3.79 / 0.0086                   |

| 3.48 / 0.0096                   |

| 3.79 / 0.0086                   |

| 3.48 / 0.0096                   |

| 3.69 / 0.0089                   |

| 3.42 / 0.0098<br>3.50 / 0.0190  |

|                                 |

Materials: Isola FR408HR High Speed High-Tg FR4

Hub Production Readiness Review, 12/2018

## Hub Test Module

ub Production Readiness Review, 12/2018

### Hub Test Module (HTM) designed to allow full system tests \* far in advance of a full shelf of FEX/FTM cards

Developed at MSU. 20 cards delivered July 2018.

### HTM design specifics

- ATCA form factor, 10 layer board

- Hosts a commercial mezzanine card with a 7-series Zynq

- Receives Hub TTC & clock via Zone-2, optional on-board clock

- Sources 6 lanes of "FEX" data to each Hub slot,  $\leq$  10.26 Gbps

- Optional MiniPods to emulate all Hub/ROD optical interfaces

- Connections to both Hub GbE networks

Viasystems Technologies Corp. LLC 8150 Sheppard Ave E Toronto, ON, M1B 5K2

Job Name : 181875 Customer : DEBRON INDUSTRIAL ELECTRONICS Part Num: 40-00643-00LF Part Rev : -Engineer : Yogi Perin

|            | Cust      | Calc             |

|------------|-----------|------------------|

| Layer      | Thickness | Thickness        |

| Layer - 1  |           | 0.0005<br>0.0020 |

|            |           | 0.0038           |

| Layer - 2  |           | 0.0006           |

|            |           | 0.0100           |

| Layer - 3  |           | 0.0006           |

|            |           | 0.0040           |

| Layer - 4  |           | 0.0006           |

|            |           | 0.0210           |

| Layer - 5  |           | 0.0012           |

|            |           | 0.0034           |

| Layer - 6  |           | 0.0012           |

|            |           | 0.0210           |

| Layer - 7  |           | 0.0006           |

|            |           | 0.0040           |

| Layer - 8  |           | 0.0006           |

|            |           | 0.0100           |

| Layer - 9  |           | 0.0006           |

| -          |           | 0.0038           |

| Layer - 10 |           | 0.0020           |

| -          |           | 0.0005           |

| Description<br>Taiyo 4000-HFX DI<br>1/2oz Mix (Std Plt)          | <b>Dk / Df</b><br>3.50 / 0.0190 |

|------------------------------------------------------------------|---------------------------------|

| 1/202 MIX (Std Pit)<br>FR408HR<br>1/202 P/G                      | 3.42 / 0.0098                   |

| FR408HR                                                          | 3.69 / 0.0089                   |

| 1/2oz Sig<br>FR408HR<br>1/2oz P/G                                | 3.48 / 0.0096                   |

| FR408HR                                                          | 3.79 / 0.0086                   |

| <b>1oz Mix</b><br>FR408HR<br><b>1oz Mix</b><br>FR408HR           | 3.48 / 0.0096<br>3.79 / 0.0086  |

| 1/2oz P/G<br>FR408HR<br>1/2oz Sig                                | 3.48 / 0.0096                   |

| FR408HR<br>1/2oz P/G                                             | 3.69 / 0.0089                   |

| 1/202 P/G<br>FR408HR<br>1/2oz Mix (Std Plt)<br>Taiyo 4000-HFX DI | 3.42 / 0.0098<br>3.50 / 0.0190  |

|                                                                  | 0.007 0.0100                    |

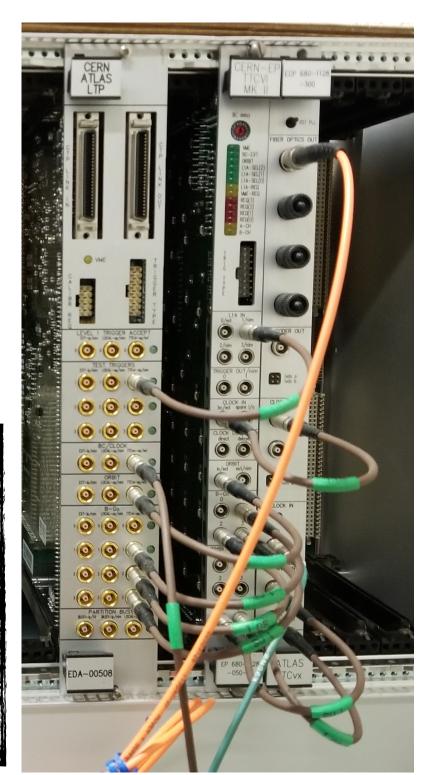

# **MSU Test Stands**

\* MSU has two Hub/HTM test stands available for system tests

- 14 slot ATCA shelf (40G qualified), primarily used for bandwidth tests. Shown here with 12 HTM cards.

- 6 slot ATCA shelf (40G qualified), primarily used for firmware development.

### System test capabilities

- VME TTC system providing 40.08 MHz master clock, L1A, ECR, BCR, etc.

- FELIX functions via TTCfx v3.1 mezzanine on VC709 Xilinx dev board.

- Optical connections between HTMs and Hub/ROD cards

- Full backplane link population with 8 lanes to/from each slot

- 16 PCs to source & sink GbE throughput tests

W. Fisher, MSU

Hub Production Readiness Review, 12/2018

## **MSU Test Stands**

W. Fisher, MSU

# **MSU Test Stands**

A *very* quick word on current test results

- MSU has tested a full shelf of 2 Hubs, 1 ROD and 12 HTMs for long-duration signal reception tests.

- Tests run using Xilinx IBERT firmware with pseudo-random bit sequences of 31 bits in length and at 6.4 Gbps line rates.

- Two long runs have been performed with different Hub modules each run.

- First ran ~30 days to BER<6E-17, no errors observed</li>

- Second ran ~18 days to BER<1E-16, no errors observed</li>

In reality, these modules never stopped running for 2+ months with no errors.

- In reality, these modules never stopped running for 2+

The real metric is more like ~ <2E-18</li>

### Much more on this later and in the next presentation, but this data is relevant throughout this presentation.

# Final Design Review Follow-up

W. Fisher, MSU

Hub Production Readiness Review, 12/2018

# Hub Final Design Review

## Hub final design review (FDR)

### Held 20 March 2018

https://indico.cern.ch/event/713755/

## Report issued 12 July 2018

- Available in EDMS:

- <u>https://edms5.cern.ch/document/1996657/1</u>

### Several recommendations and action items identified

- Clock recovery & distribution

- PCB & Signal fidelity

- FW & SW performance

- FDR Report response document circulated 10 Oct 2018

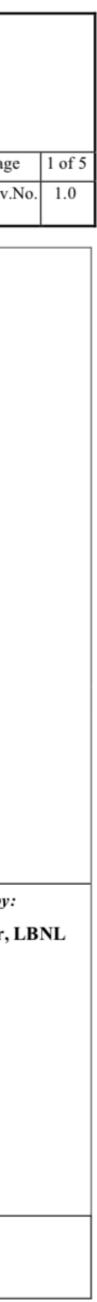

### Final Design Review of the L1Calo Hub Module

| AS Project Document. No. | Institute Document No. | Created : | 06/06/18 | Pag |

|--------------------------|------------------------|-----------|----------|-----|

| ATU-TC-ER-0110           |                        | Modified: | 11/07/18 | Rev |

### **Report of the Final Design Review**

### L1Calo Hub Module

Summar

The final design review of the L1Calo Hub module was held at CERN on March 20, 2016. This report summarises the outcome of the review.

| 1   |             | • • |

|-----|-------------|-----|

| ler | <b>NTIT</b> | ied |

|     |             |     |

| Pre                                        | pared by:   | Check                                                                                                                                                                                                                                  | Checked by:                                                               |                          |  |

|--------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------|--|

| Stefan Haas (                              | (CERN)      | Ian Brawn (RAL)<br>Philippe Farthouat<br>Ed Flaherty (Camb<br>Stefan Haas (CERN<br>Lorne Levinson (W<br>Marek Palka (Jagie<br>Elena Rocco (Mainz<br>David Sankey (RAI<br>Weiming Qian (RAI<br>David Strom (Oreg<br>Stefano Veneziano ( | ridge)<br>()<br>eizmann)<br>Ellonian University)<br>z)<br>L)<br>L)<br>on) | Kevin Einsweiler,        |  |

| for<br>information,<br>you can<br>contact: | Stefan Haas | Tel.<br>+41.22.767 9233                                                                                                                                                                                                                | stefar                                                                    | E-Mail<br>n.haas@cern.ch |  |

### **FDR Action Item(s):**

1) Reception of readout data in the ROD mezzanine installed on the Hub has to be tested from all the FEX slots (could be one at a time). Tests should be performed using IBERT as wells with the Aurora protocol and full data format implemented in the firmware.

2) It is recommend that a combined ROD/Hub intermediate design review be held prior to the Hub to a FEX modules as well as readout data transfer from a FEX through the Hub Hub/ROD and at least one FEX module prototypes.

3) Since many of these tests involve the ROD and since the performance of the ROD heavily depends on various features of the Hub, it is strongly recommended to perform a common PRR of the Hub and the ROD.

launching the pre-production of either module. (...) In addition, a full chain slice test should have been demonstrated, including the transmission of a TTC stream from FELIX through and ROD to FELIX. The test should be performed in a full-size ATCA shelf loaded with the

# Hub FDR Action Items & the ROD

It is clear by now that this is not a joint review of the Hub and ROD. There are good reasons for this. Availability of ROD prototypes has limited the ability to perform many of the requested tests.

- The current demands on the ROD primary engineer are already very high.

- feedback to the ROD design.

- The full slice test with FELIX, ROD and eFEX modules is planned for mid-Dec or early January. • The Hub team will provide FW support, on site if required.

- The US funding profile does not admit a long delay to wait for the ROD project to be ready for PRR. within L1Calo's best interests.

### We therefore have proposed to move forward with the Hub review, identifying areas which require follow-up at the ROD PRR or in a post-PRR Hub follow-up.

• We have thus focused on the independent areas that impact the Hub hardware design, and those which provide critical

• Using HTMs as stand-ins for FEX/L1Topo cards should be sufficient, as the electrical & optical interfaces are identical.

• As noted, the demands on the ROD effort are substantial and pressure to cut corners to meet the Hub review needs is not

### **FDR Action Item:**

A scheme for asserting back-pressure to throttle the readout to prevent buffer overflows needs to be defined and documented. The function required on the Hub have to be *implemented.*

- The ROD can assert back-pressure to FELIX through both: 1) Its optical connection to FELIX 2) Via a LEMO connector to the Hub front panel

The LEMO connection has been shown to have proper electrical connectivity to the ROD, but there has been no systematic test in which the ROD has controlled this signal at MSU.

# **Clock-related Action Items**

W. Fisher, MSU

# **Clock Distribution: Hub PLL Chip**

### **FDR Action Item:**

...[the Hub PLL chip] has to be fully qualified in terms of input-to-output phase variation, including the effect of temperature. The input-to-output skew of the Silicon Labs Si5344 has been measured to be about 20 ps (over 10000 reset cycles) at room temperature. The performance of the selected jitter cleaner should match this figure. The phase-noise spectrum of the output clock used for the MGT reference also needs to be analysed against the requirements from the Xilinx specifications.

- FDR reviewers had the impression that the clock PLL chip chosen for the Hub was not sufficiently characterized and, thus, qualified for the project.

- The Hub uses the Conner Winfield SFX-524G.

- If more reference clock frequencies are required, this chip would not be adequate.

• Furthermore, this chip provides only one MGT reference clock frequency at 320.64 MHz.

# **Clock Distribution: Hub PLL Chip**

- - The choice of quartz yields a Q value of O(50,000) rather than O(50)

- This high Q value does imply a narrower frequency tracking range of ±40 ppm: 40.077097 40.080303 MHz Ο

- This satisfies the PLL operating range in FELIX requirement 2.3.5: 40.078886-40.078973 (proton runs) and Ο 40.078422-40.078973 (heavy ion runs).

- The high Q value gives rise to excellent RMS jitter generation specification for the ConWin SFX-524G • 0.20 ps RMS jitter for a 156.25 MHz clock input

| Symbol            | Parameter                | Minimum | Nominal   | Maximum      | Units       | Notes    |

|-------------------|--------------------------|---------|-----------|--------------|-------------|----------|

| J <sub>GEN2</sub> | Jitter Generation RMS    |         | 0.20      | -            | ps          | 4.0      |

|                   | (12 kHz - 20 MHz)        |         |           |              |             |          |

| J <sub>TRAN</sub> | Jitter Transfer Function | -       | -         | 0.1          | dB          | 5.0      |

| TF                | Input Frequency Tracking | ±40     | -         |              | ppm         |          |

|                   |                          | http:// | /www.conw | in.com/datas | heets/sg/sg | g186.pdf |

The stability of the L1Calo FEX system is in part driven by the quality of the distributed clock. Thus, the Conner Winfield SFX-524G was chosen because it has an extremely high-quality quartz VCO, rather than a PLL device with an LC VCO.

# **Clock Distribution: Hub PLL Chip**

- - operations is negligible.

- The phase noise specification provides plenty of margin relative to the Xilinx MGT specification requirements • Similar to the Si5345 data sheet

| 7-Series     | Ultrascale       | Si5345           | Nominal                                                                                                                                                                                                       | Maximum                                                                                                                                                                                                                                                           | Units                                                                                                                                                                                                                                                                                                                                              | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24G-DFF-A10Z |                  |                  |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                    | 6.0                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| -            | -                | n/a              | -57                                                                                                                                                                                                           | -45                                                                                                                                                                                                                                                               | dBc/Hz                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| -            | -                | -91              | -92                                                                                                                                                                                                           | -80                                                                                                                                                                                                                                                               | dBc/Hz                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|              | -                | -123             | -120                                                                                                                                                                                                          | -110                                                                                                                                                                                                                                                              | dBc/Hz                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| -116         | -105             | -135             | -138                                                                                                                                                                                                          | -135                                                                                                                                                                                                                                                              | dBc/Hz                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| et -124      | -124             | -140             | -150                                                                                                                                                                                                          | -145                                                                                                                                                                                                                                                              | dBc/Hz                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| -131         | -130             | -153             | -157                                                                                                                                                                                                          | -147                                                                                                                                                                                                                                                              | dBc/Hz                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| t –          | -                | -162             | -160                                                                                                                                                                                                          | -150                                                                                                                                                                                                                                                              | dBc/Hz                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|              | 24G-DFF-A10Z<br> | 24G-DFF-A10Z<br> | 24G-DFF-A10Z       -       -       n/a         -       -      91         -       -      123         -       -116      105      135         ot      124      124      140         -      131      130      153 | 24G-DFF-A10Z       -       -       n/a       -57         -       -       -       -91       -92         -       -       -116       -105       -135       -138         ot       -124       -124       -140       -150         -131       -130       -153       -157 | 24G-DFF-A10Z       -       -       n/a       -57       -45         -       -       -91       -92       -80         -       -       -123       -120       -110         -       -       -135       -138       -135         -       -124       -124       -140       -150       -145         -       -131       -130       -153       -157       -147 | 24G-DFF-A10Z       -       -       n/a       -57       -45       dBc/Hz         -       -       -       -91       -92       -80       dBc/Hz         -       -       -       -123       -120       -110       dBc/Hz         -       -       -       135       -138       -135       dBc/Hz         et       -124       -124       -140       -150       -145       dBc/Hz         -131       -130       -153       -157       -147       dBc/Hz |

The stability of the L1Calo FEX system is in part driven by the quality of the distributed clock. Thus, the Conner Winfield SFX-524G was chosen because it has an extremely high-quality quartz VCO, rather than a PLL device with an LC VCO.

Because this PLL has a quartz VCO (rather than LC), the performance over temperature variations expected in the L1Calo

### Bottom line: 2 Hub + 12 HTM have run with BER<6E-17.

### **FDR Action Item:**

The fixed phase of the clock extracted from the FELIX TTC stream needs to be demonstrated across modules resets, FPGA re-configuration and power-cycles. Since the standard GBT-FPGA implementation in a Xilinx Ultrascale FPGA can achieve a delay variation better than 100 ps (60 ps peak-to-peak over 1000 reset cycles), this is the performance figure to be met.

- than 120 MHz or 240 MHz.

- The Hub design restricts clocks to avoid domain crossings and to simplify board design.

• Concern primarily related to the 320 MHz MGT reference clock provided by the Hub, rather

- The Hub module successfully recovers the 40.08 MHz LHC clock using the GBT-FPGA core in "latency-optimized" mode Implemented by generating a 120 MHz MGT reference clock via QPLL • The MGT eventually tracks the 4.8 Gbps serial data stream, no relevant phase noise due to rate conversion.

- "Frame Aligner" status and "Bit Slip Control" status are monitored to ensure proper GBT functionality

- - Clock phase observed to be constant (to better than 100 ps) over a range of repeated tests Monitored via comparison of TTC input clock to Hub output clock

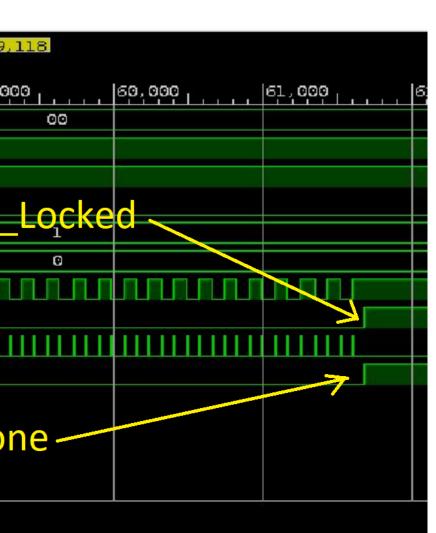

| Value 55,000 56,000 57,000 58,000       | 59<br> 59,0 |

|-----------------------------------------|-------------|

| .t_inst/myRSTcnt[7:0 00                 |             |

| .t_inst/rx_reset_done 1 MGT status      |             |

| nst/ndfsm reset dong 1                  |             |

| tRst_from_bitslipCti 0                  | eader       |

| T_AUTORSTEn_i[1:1] 1 bitSlipEven        | eauer_      |

| TORSTONEVEN_i[1:1] 0                    |             |

| .st/nx_bitslipIsEven_s                  |             |

| t/rx_headerlocked_s_0                   |             |

| .Cmd_to_bitSlipCtrile 0                 |             |

| .from_rxBitSlipContro 0 bitSlip_Request |             |

| bitSl                                   | ip_Do       |

| Updated at: 2018-May-30 05:57:29        |             |

- Manual intervention, force GBT realignment

- Reset receiver MGT on Hub

- Power cycle Hub

- Reconfigure Hub FPGA

- Unplug/reinsert TTC fiber @ TTCfx/VC109

- Reconfigure TTCfx/VC709

- Re-initialize the TTCfx/VC709

- Reset of the TTCfx/VC709

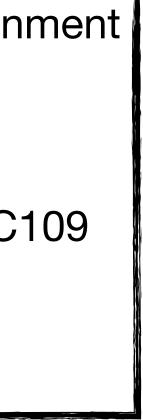

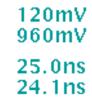

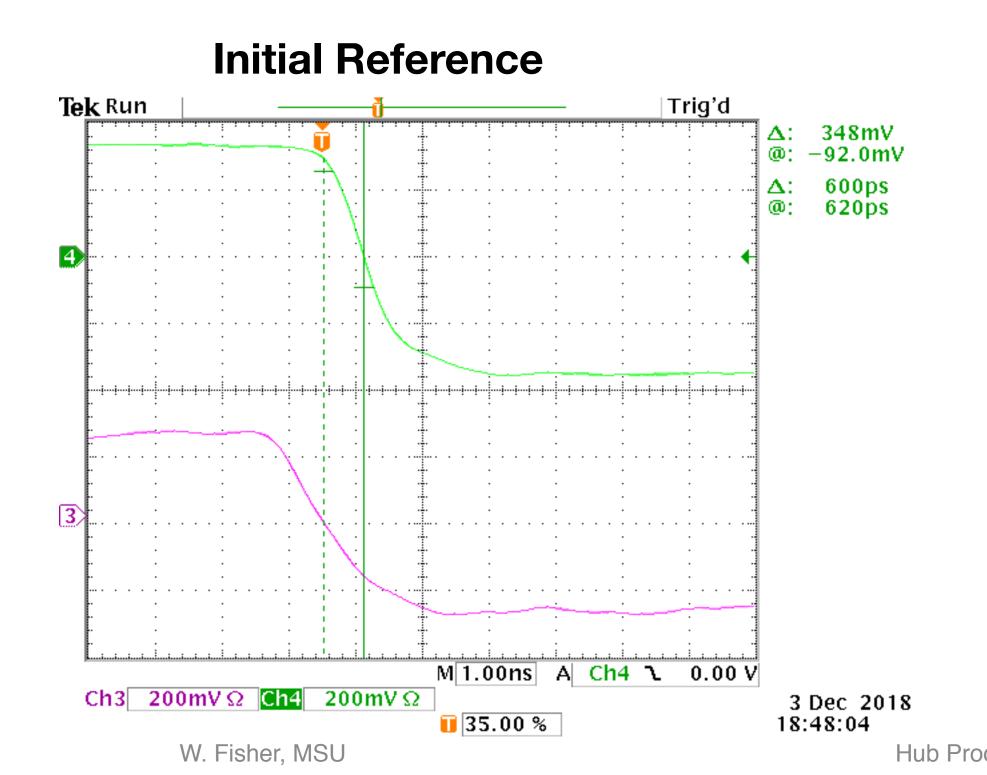

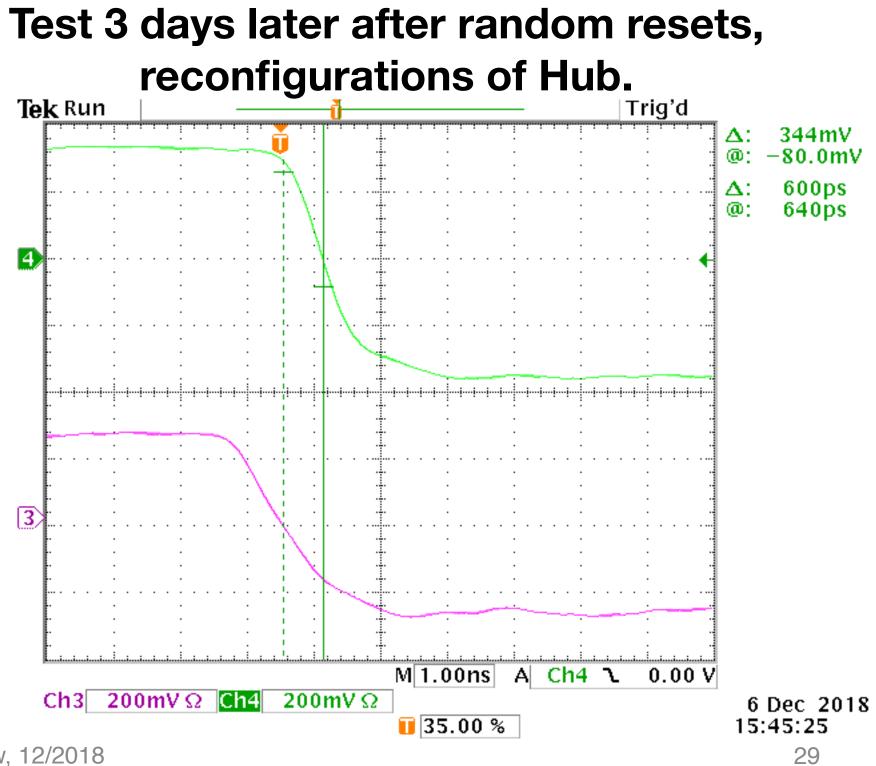

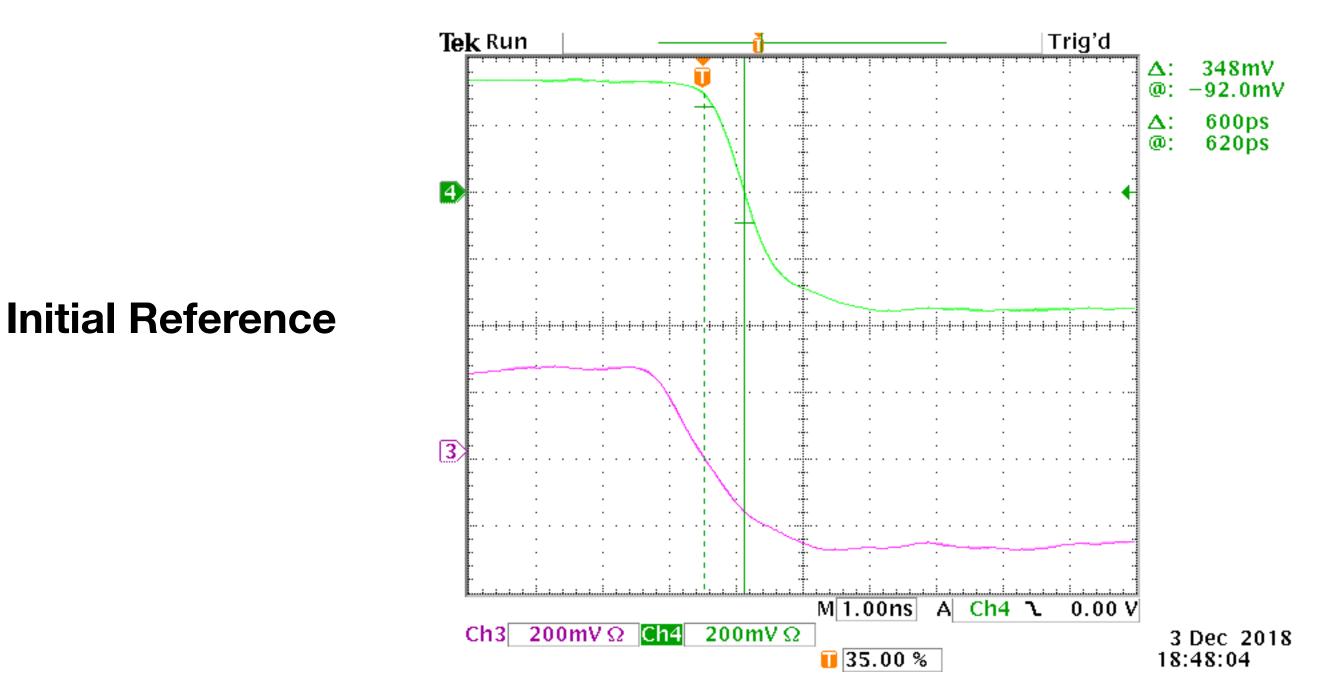

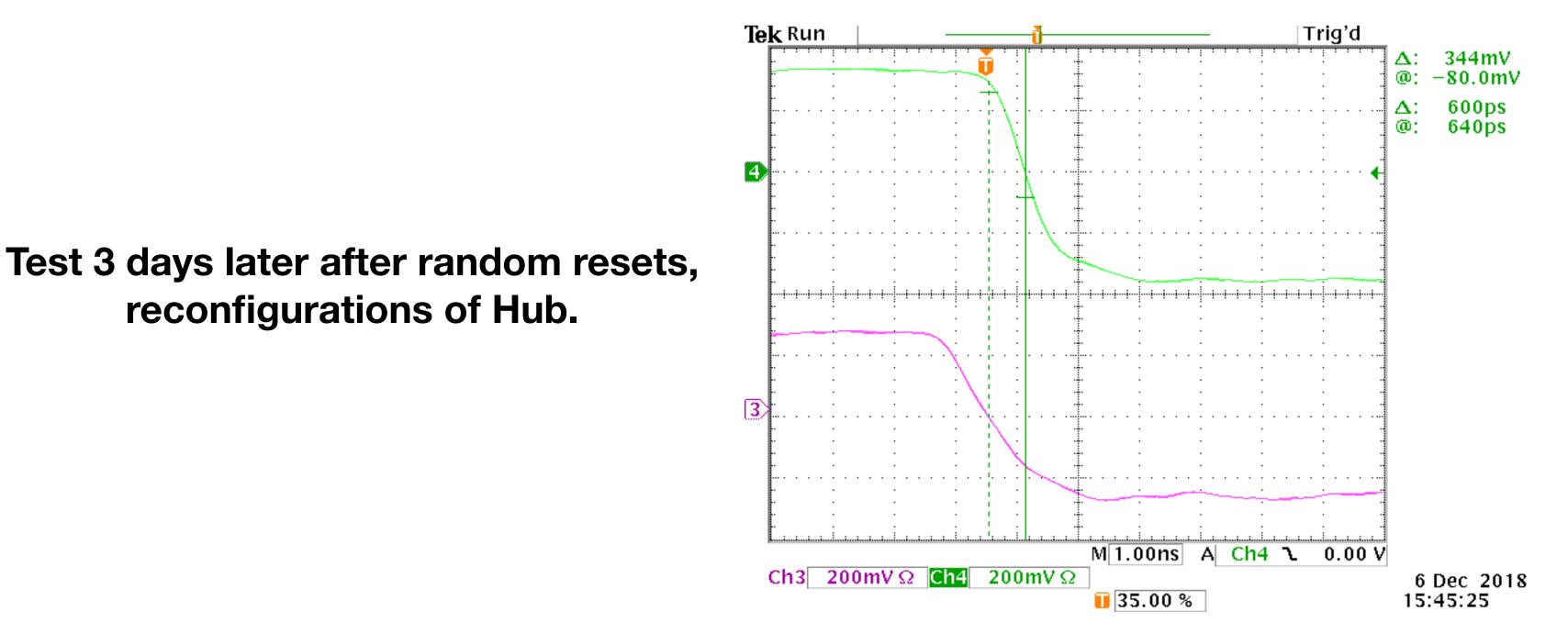

Here we have example scope captures of the recovered clock from the Hub over a few example interventions to the FELIX \* TTC clock.

### **Channel 1: 160 MHz ref clock Channel 2: Recovered Hub clock Channel 4: TTC input clock**

### 10 Oct 2018 17:05:49

- Stability of the clock latency at the FEX (HTM) has also been tested

- The two scope traces below test latency stability between the 40.08 MHz clock:

- 1) Starting at the TTC VME crate,

- 2) through the VC-709 FELIX system,

- 3) through the GBT Receiver, PLL jitter cleaner and reference clock fanout on the Hub,

- 4) Across the ATCA shelf backplane,

- 5) Received on the HTM (FEX) card where it passes through a PLL jitter cleaner to a front-panel clock monitor.

Hub Production Readiness Review, 12/2018

- Stability of the clock latency at the FEX (HTM) has also been tested

- The two scope traces below test latency stability between the 40.08 MHz clock:

- 1) Starting at the TTC VME crate,

- 2) through the VC-709 FELIX system,

- 3) through the GBT Receiver, PLL jitter cleaner and reference clock fanout on the Hub,

- 4) Across the ATCA shelf backplane,

- 5) Received on the HTM (FEX) card where it passes through a PLL jitter cleaner to a front-panel clock monitor.

- Stability of the clock latency at the FEX (HTM) has also been tested

- The two scope traces below test latency stability between the 40.08 MHz clock:

- 1) Starting at the TTC VME crate,

- 2) through the VC-709 FELIX system,

- 3) through the GBT Receiver, PLL jitter cleaner and reference clock fanout on the Hub,

- 4) Across the ATCA shelf backplane,

- 5) Received on the HTM (FEX) card where it passes through a PLL jitter cleaner to a front-panel clock monitor.

# **Clock Distribution: Clock Fanout Logic Level**

### **FDR Action Item:**

There were some questions concerning the logic levels for the fan-out of the bunch clock over the backplane: the Hub uses an LVDS fan-out chip, however it seems that the eFEX would prefer LVPECL levels. The compatibility of the signal level from the Hub with the eFEX, jFEX and L1Topo should be checked and interoperability tests performed.

- Preference from FEX groups to use LVPECL to hopefully improve margin at their MGTs, due to better jitter performance.

- Preference from the Hub group to minimize the noise crossing the FEX data fanout, reduced in LVDS wrt LVPECL due to smaller edge rise.

# **Clock Distribution: Clock Fanout Logic Level**

- The current Hub and FEX/L1Topo card designs are compatible

- Existing FEX/L1Topo designs use PLL chips with universal inputs • No design changes required to use either source

- L1Calo system is not the characteristic use case for LVPECL

- Benefits of LVPECL are found when both ends of the LVPECL link are on the same board (ie, full run of the link)

- $\circ$  ie, full run of the link is over one ground plane and both Rx & Tx are operated from the same positive power plane.

- at high enough frequency.

- When done right, LVPECL can indeed have an advantage over LVDS

- disadvantage WRT LVDS.

- To resolve the issue, eye diagrams at the eFEX MGTs have been studied for the different clock sources. \*\*

- LVPECL when using FTM and LVDS when using the Hub

- No discernible difference in BER or open eye area reported. L1Calo has agreed on the LVDS logic level.

• ECL logic levels are WRT its positive power supply terminal and any trace imperfection spoils the common mode rejection

• However, when operating over a backplane, with separate positive and ground planes at Tx and Rx, then LVPECL is at a

# **Firmware-related Action Items**

W. Fisher, MSU

### FDR Action Item(s):

1) Firmware for the essential functions of the Hub needs to be ready and fully tested. This includes the interface to FELIX as well as to the ROD and the FEX modules with close to final data formats. IPbus should also be fully working. 2) The TTC interface with FELIX need to be fully implemented and characterized. 3) In addition the firmware does not seem to be under revision control yet, the overall L1Calo guidelines on this should be followed.

There are four core firmware aspects for the Hub project. (a) ROD power-up sequence state machine (b) GBT/FELIX TTC clock recovery with deterministic phase (c) TTC/Combined data transmission to node slots with deterministic phase. (d) IPbus functionality to control ROD/Hub configurations and retrieve monitoring data.

## Firmware Management

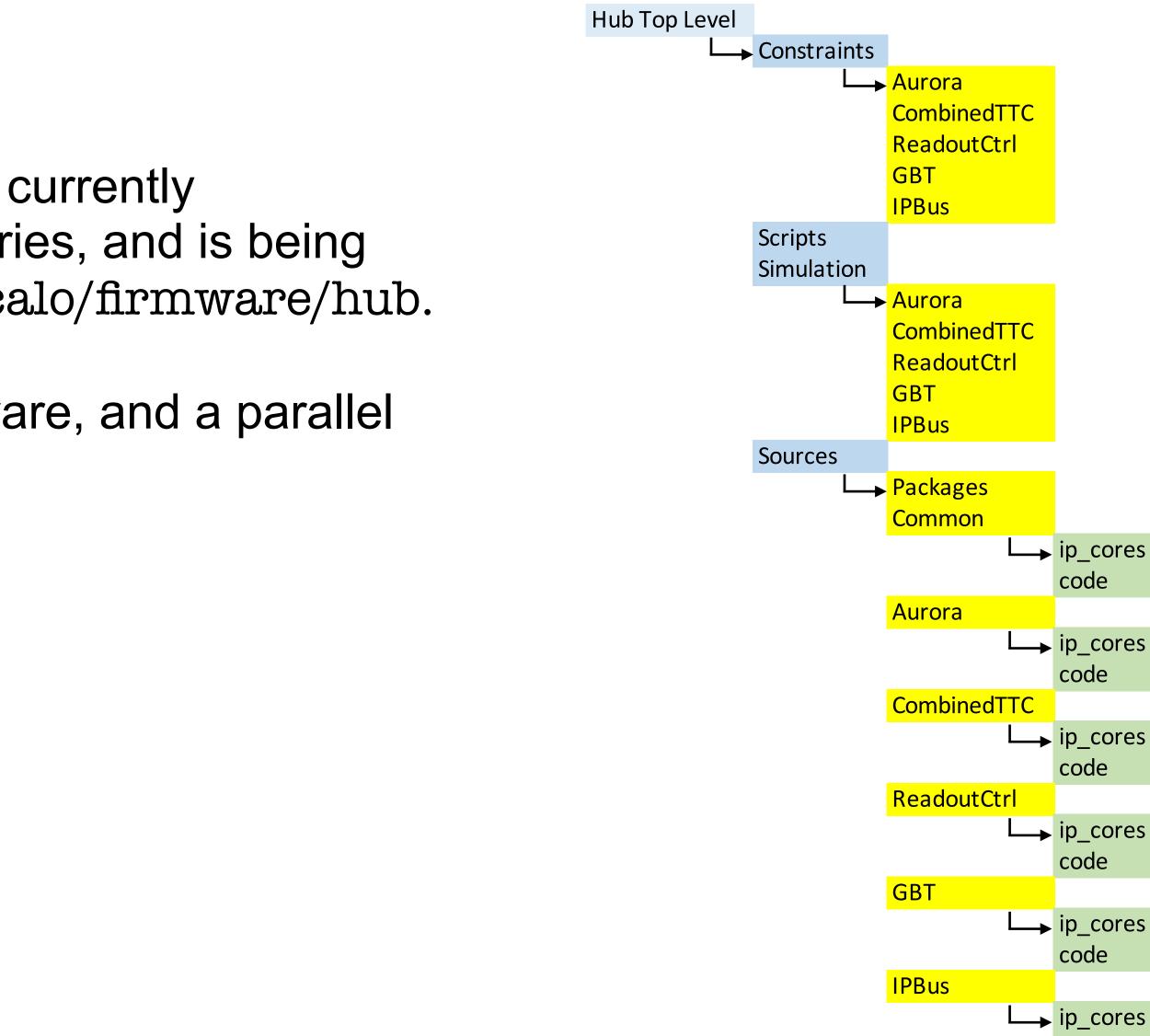

The versioning control of the Hub firmware is currently maintained in CERN gitlab in private repositories, and is being migrated to the CERN gitlab project atlas-llcalo/firmware/hub.

There is a similar structure for the HTM firmware, and a parallel repository for the Hub and HTM software.

## code

36

## Firmware Block Diagram

## Firmware: IPbus Implementation

- level control of all card functions.

- Full set of status/control and test/monitoring registers

- XILIX AXI4 subsystem IPs (via IPbus to AXI4 bridge, similar to ROD)

- 3 AXI IIC Master IP (22 internal registers)

- MiniPODs (temp, light level), DC/DC supplies (temp, voltage, current)

- 3 AXI EthernetLight IP (11 internal registers)

- 3 Broadcom GbE switch chips

- AXI System Management Wizard IP (~100 internal registers)

- FPGA System Monitor (temp, voltage)

| Addr                  | туре   | Name                                  | Content                                                                                                                                              | Bit                                                                                                                    | Comment                                                                                                                                                                                                                                                                                                                                                                   | Addr     | туре   | Name           | Content                                                                                                                                             | E        | Bit                                                                                                                                                     | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------|--------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| This is c<br>All bits | ontrol | control<br>register fo<br>'0' after p | other_hub_Clk<br>fex_clk_en<br>mgt_equ_en<br>i2c_buf_en<br>spare<br>rod_pwr_en_b ?<br>spare<br>mpod_rst_b *<br>spare<br>r the individual<br>ower-on. | [31]<br>[30]<br>[29:17]<br>[16]<br>[15]<br>[14]<br>[13-11]<br>[10]<br>[9]<br>[8:6]<br>[5]<br>[4]<br>[3:0]<br>pins (exe | FPGA internal, selects clock from other Hub<br>Enable clock to FEXS<br>Enable equalization in MGT Fanout chips<br>I2C_Buf_1501_ENABLE<br>I2C_Buf_1502_ENABLE<br>spare bits<br>ROD may turn ON its power supplies<br>ROD may turn ON its power supplies<br>spare bits<br>Trans_MiniPOD_RESET_B<br>Recvr_MiniPOD_RESET_B<br>spare bits<br>eption - other_hub_Clk, Drw: 40A) | ODOOOOOG |        | status         | pll_lock<br>phy_int<br>mpod_int<br>hub_smb_aler<br>hub_pwr_good<br>rod_present_<br>rod_smb_aler<br>rod_status<br>rod_status<br>sw_loop_det<br>spare | t<br>t_b | [31]<br>[30]<br>[29]<br>[28]<br>[27]<br>[26]<br>[25]<br>[24]<br>[23]<br>[22]<br>[21]<br>[22]<br>[19]<br>[18]<br>[18]<br>[18]<br>[18]<br>[15:0]<br>pins. | From PLL lock circuits - pll40_lock<br>From PLL lock circuits - pll320_lock<br>From Eth Phy chips - phyU21_int_b<br>From Eth Phy chips - phyU22_int_b<br>From the MiniPODs - trans_mpod_intr.<br>From the MiniPODs - recvr_mpod_intr.<br>From 7 DCDC Converters<br>From the Power Control circuits<br>ROD is present<br>Power supply problem on the ROD<br>ROD power<br>ROD config<br>spare rod_power_ctrl4<br>Broadcom Switch chips switch_a_loop.<br>Broadcom Switch chips switch_b_loop.<br>Broadcom Switch chips switch_c_loop.<br>spare bits, set to all zeros |

|                       |        | ure implement<br>with (*) are         | ed<br>implemented - mp                                                                                                                               | ood_rst_b                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                           | HUB: all | bits a | are implemente | implemented -                                                                                                                                       |          | [31]<br>[29]<br>[27]<br>[26]                                                                                                                            | PLL_40_MHZ_LOCKED_MON<br>ETH2_INT<br>MP_TRANS_INTR<br>MP_REC_INTR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Both the Hub and HTM cards have successfully integrated IPbus firmware into their respective designs, allowing register-

• Equalizers, LEDs, I2C buffers, ROD control, IPbus lock, clock selector, HW/FW revision, etc.

ock tr\_b tr\_b

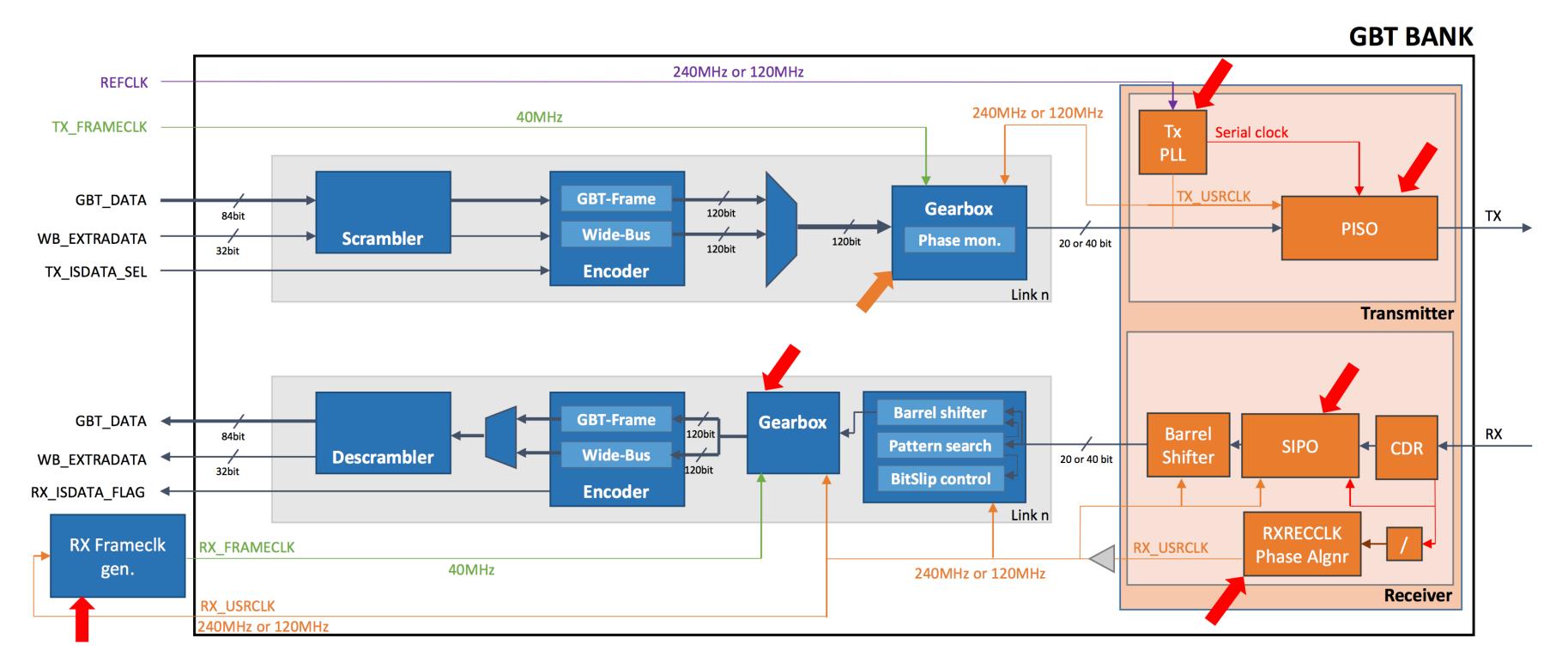

# Firmware: GBT/TTC Clock Recovery

- As stated previously, the LHC clock is recovered from the TTC signal provided via FELIX and decoded via the GBT firmware.

- 120 MHz reference clock generated at MGT quad QPLL

- All features of the firmware behave as expected

- Stable, deterministic latency clock recovered and fanned out. Ο

https://indico.cern.ch/event/489996/contributions/2291863/attachments/1345764/2028939/GBTTutorial\_-\_TWEPP2016.pdf

Hub Production Readiness Review, 12/2018

# Firmware: TTC/Combined Data Fanout

### **FDR Action Item(s):**

1) Tests of the TTC clock reception on the each of the FEX slots as well as the TTC/control link to and from the FEX slots have to be performed under the same conditions as above.

2) The TTC interface with FELIX need to be fully implemented and characterized.

• The L1Calo requirement is that the TTC combined data is provided at the receiving end with a deterministic latency.

# Firmware: TTC/Combined Data Fanout

- To define the phase of the arrival of the TTC/Combined data, we use the LHC master clock as the reference. This minimizes the variation across the system and provides an easily-to-verify, stable reference.

- 128 bits of control data are received from the ROD at a 6.4 Gbps line rate • This data is translated and merged with TTC data in the Hub (L1A, ECR, BCR)

- 128 bits of TTC/Combined data are transmitted from the Hub at a 6.4 Gbps line rate • At the receiver, the data is transferred into a parallel register

- The 128 bits of the TTC/Combined data are provided to the users at the output of a 128 bit wide D register.

- The D register is updated on the positive edge of the FPGA's 40.08 MHz clock that is locked to the LHC backplane reference clock.

- $\circ$  These 128 bits are stable at all times except during the update.

### Receiver FPGA requirements

- MGT reference clock to receive the 6.4 Gbps link

- 40.08 MHz clock locked to the LHC backplane reference clock

### \*\* The Readout Control and Combined TTC Specification (v0.5) is linked to the indico page.

# **Other Hardware-related Action Items**

W. Fisher, MSU

### FDR Action Item(s):

A full-size ATCA shelf should be fully populated with Hub Test Modules and two Hub modules in order to run traffic on all the backplane links to and from the Hub concurrently.

BER tests should be performed in this configuration to check for potential crosstalk issues.

The test should be performed with a ROD mezzanine installed in order to also cover the backplane links to the ROD.

•At the time of the FDR, no full-shelf bandwidth tests had been performed. The primary concern is whether the dense design of the FEX data fanout, clock and TTC/Combined data routing is susceptible to crosstalk.

As noted earlier in this presentation, Hub Test Modules (HTMs) have been produced by MSU. \*\* The HTMs emulate the relevant subset of FEX interfaces to the Zone-2 and optical interfaces for Hub and ROD. The MSU 14-slot shelf and 6-slot shelf both are populated with HTMs.

Hub Production Readiness Review, 12/2018

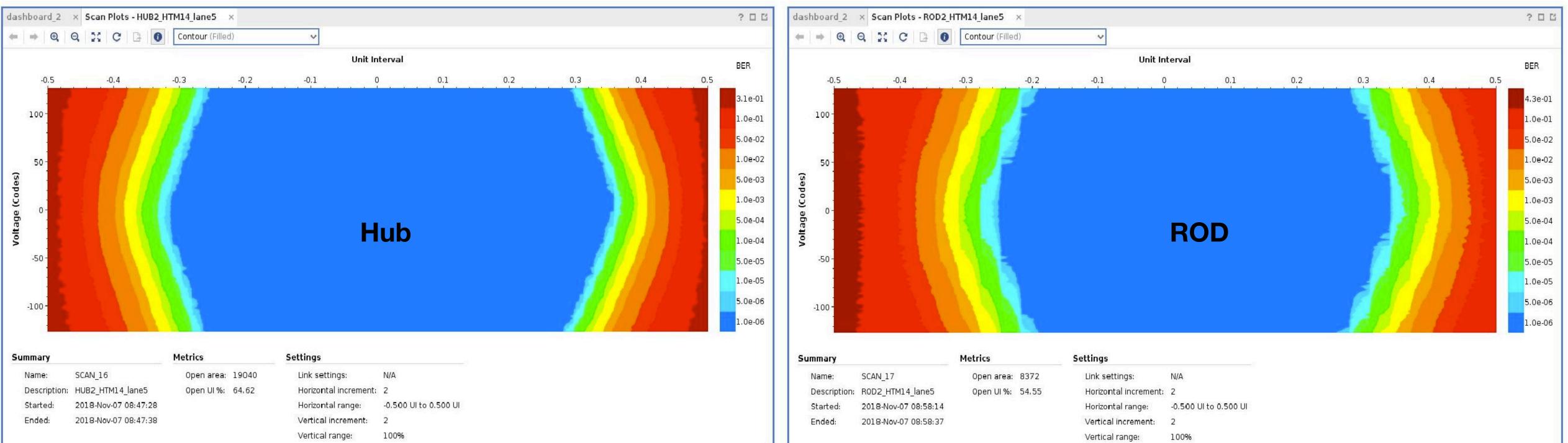

BER tests have been performed with Xilinx IBERT firmware at a line rate of 6.4 Gbps and using PRBS31 Two separate, long-duration runs have been performed and find the full system capable of BER<6E-17. No errors observed. Eye diagrams have been produced for both Hub and ROD data links. They all look very good. Relevant data shown here, much more analysis shown in the next talk.

### Hub Slot 2, HTM Module 14, Data Lane 5: DFE off, Fanout Eq on

- Zone-2 links for Hub and ROD.

- Relevant data shown here, much more analysis shown in the next talk.

BER tests have been performed with Xilinx IBERT firmware at a line rate of 6.4 Gbps and using PRBS31, including all FEX

Two separate, long-duration runs have been performed and find the full system capable of **BER<6E-17**. No errors observed.

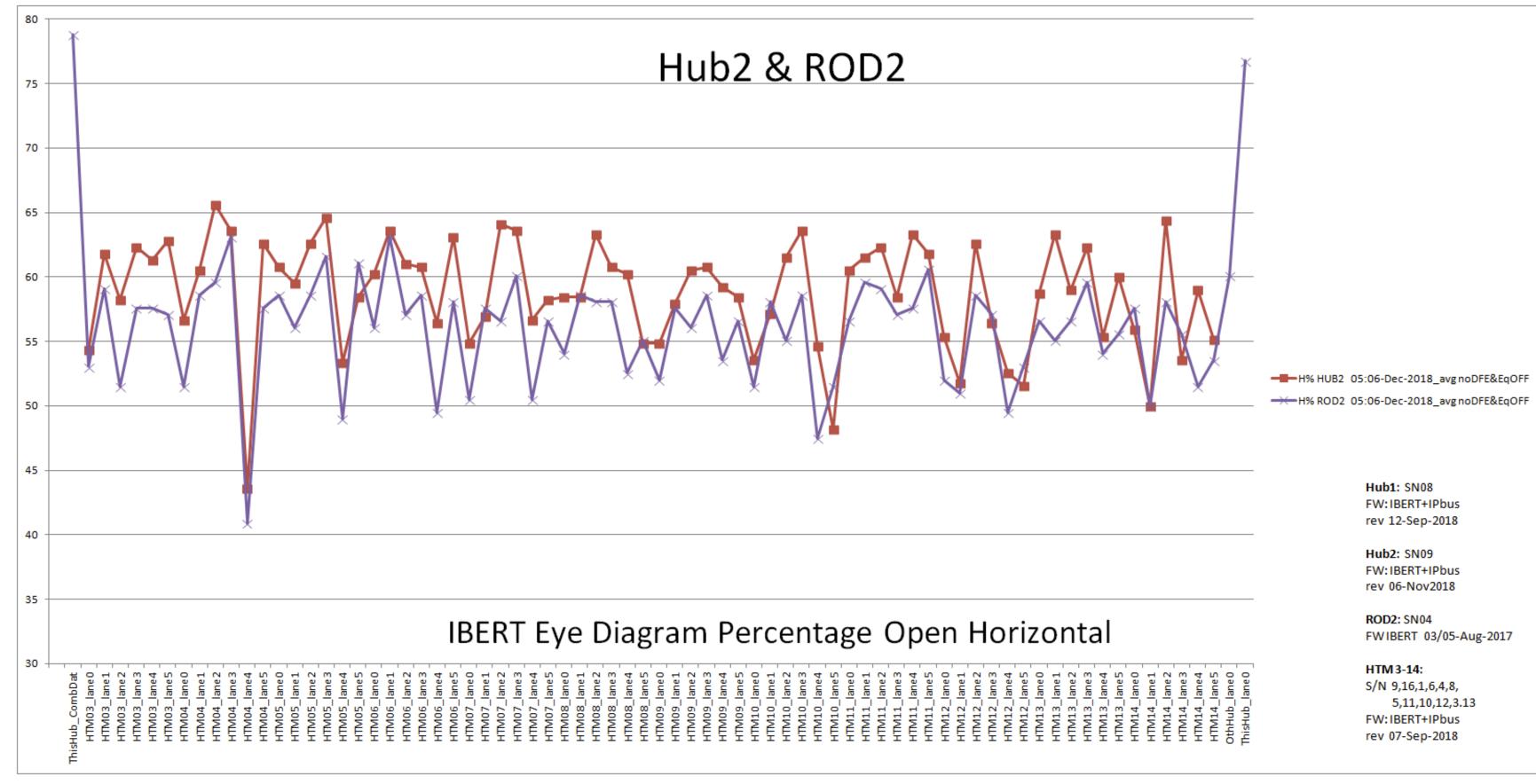

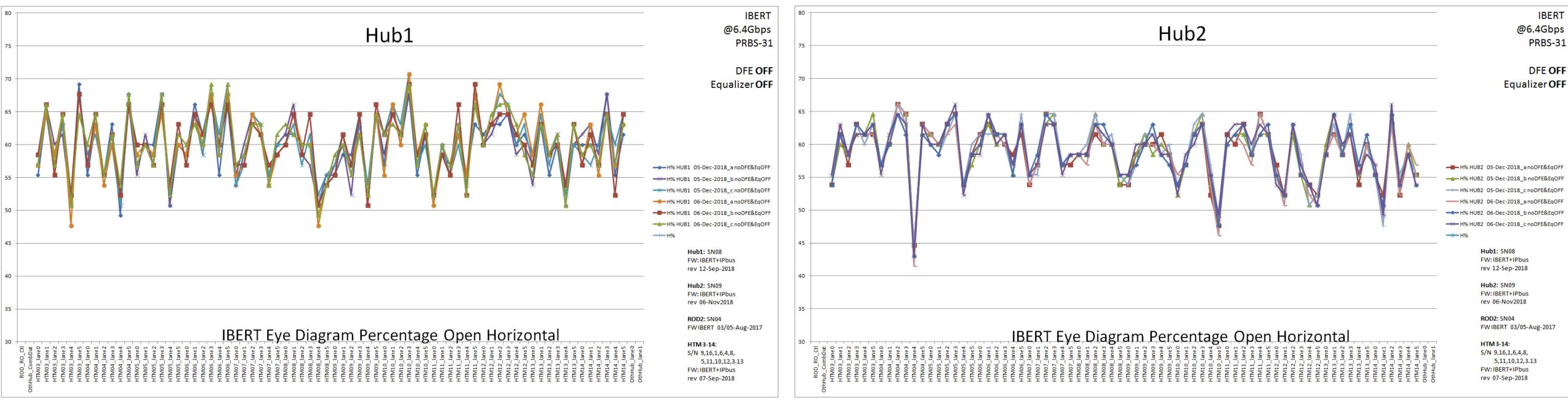

Repeated tests of the Hub eye diagrams illustrate very high uniformity over Hub modules.

- Repeated tests of the same card also show zero variation.

- Quality and uniformity of the Hub PCB manufacturing and assembly processes is very high.

- 6 Hubs shown here, 2 remaining in UK will be tested once we can swap them out.

| HUB2 | 05-Dec-2018_a noDFE&EqOFF |

|------|---------------------------|

| HUB2 | 05-Dec-2018_b noDFE&EqOFF |

| HUB2 | 05-Dec-2018_c noDFE&EqOFF |

| HUB2 | 06-Dec-2018_a noDFE&EqOFF |

| HUB2 | 06-Dec-2018_b noDFE&EqOFF |

| HUB2 | 06-Dec-2018_c noDFE&EqOFF |

|      |                           |

### **FDR Action Item(s):**

1) The Hub blade uses a 22-layer PCB. The dielectric material chosen is Isola FR408HR, which is not a dedicated high-speed laminate. For instance the dissipation factor (Df) of FR408HR is about 2.5 times higher than the one of Megtron-6 or Isola I-Tera, which are the dielectric materials used for the FEX blade PCBs. There was no technical justification given for this choice, in particular since the PCB production house is the same than the one used for the gFEX, Megtron-6 would clearly have been a possible choice. The choice of the dielectric should be reconsidered for the pre-production modules.

2) A signal integrity analysis of the most critical high-speed tracks (probably from the fan-out buffers to the ROD) should be done to assess the impact of the chosen dielectric with respect to a high-speed material such as Megtron-6.

Concern expressed that the Hub PCB laminate will not support the required signal integrity of the high-speed data links.

# Hardware: PCB Laminate

- The choice of Isola FR408HR was intentional, not an oversight. There were three primary considerations:

- this laminate was recommended to give the highest chance of uniformity over a build of 20 PCBs.

- 2) that delamination may only be apparent after years of use, the risk was very high to use these laminates.

- issues.

- 3) clearly the goal of 10+ Gbps bandwidth to all FEX slots and designed to meet that requirement.

**Bottom line(s):**

- 2 Hubs + 12 HTMs have run with BER<6E-17.

Based on consultation with the PCB manufacturer and assembly house, and with a clear understanding of our use case,

Our observation of other attempts to use Tachyon/I-Tera/Megtron-6 laminates is a high frequency of delamination. Given

There are numerous examples in ATLAS & CMS, notably in L1Calo. MSU's first run with the CMX had delamination

MSU's primary electronics design engineer has decades of experience in high-speed digital design. He understood very

## 8 prototype Hubs have been built with extremely high uniformity.

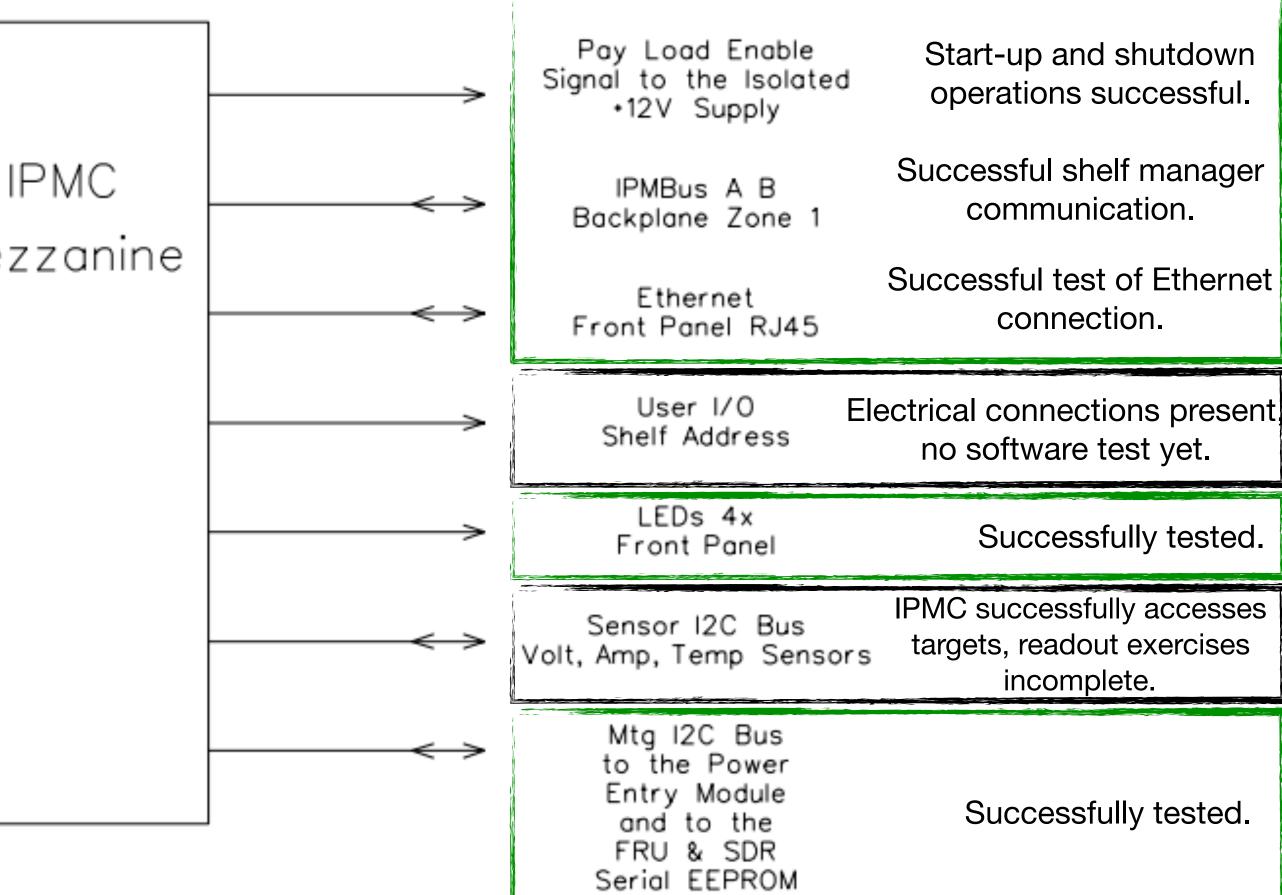

### **FDR Action Item(s):**

1) Monitoring on-board sensors (at the very least for the Hub and ROD FPGA temperatures) using the IPMC has to be tested. The sensor values have to be read out through the ATCA shelf-manager.

2) The I2C bus to access the on-board sensors is shared between two masters: the Hub the sensor bus appears not to have been tested yet. The IPMC requires access to some the ATCA shelf speed regulation through the shelf manager to work. This needs to be demonstrated.

Concern expressed regarding I2C multimastering and ability of proper IPMC functions.

FPGA and the IPMC. It is unclear how the arbitration will work and access from the IPMC to critical temperature sensors (Hub FPGA and ROD FPGA on-chip temperature) in order for

- operations.

- Outside debugging, commissioning and bench testing, only the IPMC will master the I2C bus.

- All Hub & ROD components on the I2C bus are able to be accessed & monitored

- DCDC converters, FPGA sysmon are primary targets.

- We have tested our ability to perform I2C arbitration with the IPMC

- Successfully able to detect bus busy and data FIFO status on the I2C bus.

- Hub IPbus/I2C software reliably detects IPMC cycles, with a state machine designed to wait for successful I2C mastering arbitration.

- O(300k) cycles executed without I2C error in a long test run.

## Hardware: I2C Multimastering

The Hub I2C bus can be isolated from the IPMC I2C bus and we do not require I2C multimastering during "normal" L1Calo

### **Example read of Hub miniPOD transmitter**

| <pre>MiniPod type verified to be: trans_mpod<br/>Minipod internal temperature is 32.22 C<br/>The voltage on the 2.5 Vcc power supply is 2.4657 V<br/>The voltage on the 3.3 Vcc power supply is 3.2596 V<br/>The serial number of the current device: trans_mpod is : A17285016<br/>The operating time is 3038.0 hours or 126.583333333 days<br/>Optical power for channel number trans_mpod is: 0.14646524684 dBm or 103<br/>Optical power for channel number trans_mpod is: 0.911039440903 dBm or 12<br/>Optical power for channel number trans_mpod is: -0.00130307891732 dBm or<br/>Optical power for channel number trans_mpod is: 1.06496870139 dBm or 127<br/>Optical power for channel number trans_mpod is: 0.137217780511 dBm or 100<br/>Optical power for channel number trans_mpod is: 1.09646031091 dBm or 128<br/>Optical power for channel number trans_mpod is: 1.0510124455 dBm or 1273<br/>Optical power for channel number trans_mpod is: 1.0510124455 dBm or 1273<br/>Optical power for channel number trans_mpod is: 1.0510124455 dBm or 1273<br/>Optical power for channel number trans_mpod is: 1.0510124455 dBm or 1273<br/>Optical power for channel number trans_mpod is: 1.3165073809 dBm or 1354<br/>Optical power for channel number trans_mpod is: 1.32080134129 dBm or 1354<br/>Optical power for channel number trans_mpod is: 1.20080134129 dBm or 131<br/>The nominal wavelenght for device trans mpod is: 1.20080134129 dBm or 131</pre> | 33.4<br>999<br>7.9<br>32.1<br>35.8<br>50.4<br>50.4<br>62.3<br>8.5 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| The nominal wavelenght for device trans_mpod is 845.0 nm ( $\pm$ 15.015 nm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                   |

\*

- Due to limitations in obtaining IPMC software, however, this area has not been fully explored.

- L1Calo uncertainty in IPMC choice has not helped clarify how to proceed in this area.

- We are working with both LAPP and CERN IPMCs, possess sufficient LAPP IPMCs for the production run.

| Electrical connections present, no alarm tests yet. | Alarm Signal<br>from the Power<br>Entry Module                 | > |    |

|-----------------------------------------------------|----------------------------------------------------------------|---|----|

| Accesses same<br>signals seen on Hub<br>FPGA        | Hardware<br>Slot Address<br>from the<br>Backplane Zone 1       | > | Me |

| Operates as expected, hot swap demonstrated.        | Front Panel<br>Handle Switch                                   | > |    |

| Start-up and shutdown operations successful.        | IPMC_3V3<br>Management Power<br>from the Power<br>Entry Module | > |    |

### Hardware: IPMC

### We have successfully tested all relevant electrical connections to/from the IMPC, and verified their proper operation.

### **FDR Action Item:**

Temperature (FPGA and MiniPOD) and power dissipation tests with a Hub carrying a ROD mezzanine in a target ATCA shelf, if possible with all slots populated (e.g. with Hub Test Modules), have to be performed.

FPGA silicon temperatures are measured with a full 14-slot shelf of 12 HTMs, 2 Hub modules and 1 ROD. Shelf fan speed set to 6/15 and ambient air used for cooling.

```

FPGA temperature ------

V----- Configuration S

Hub2 power up with safe foundat

Hub2 Config with ibert+ipbus V

ROD2 power ON

Hub2 Turn OFF unused TX

Hub2 Define links (DFE ON)

Hub2 Turn DFE OFF all links

ROD2 Config FPGA with Ed's ibe

ROD2 Define links (DFE ON)

ROD2 Turn OFF all TX except RO

ROD2 Turn DFE OFF all links

```

| >     | Hub2   |      | R0D2   |      |

|-------|--------|------|--------|------|

| Stage | temp C | İ    | temp C | i i  |

|       |        |      |        |      |

| tion  | 26     | İ    | i      | i i  |

| 1.2   | 46     | +20  |        | İ İ  |

|       | 46     |      | 26.5   |      |

|       | 43.5   | -2.5 | 26.5   | i i  |

|       | 43.5   |      | 26.5   | İ İ  |

|       | 42.5   | -1   | 26.5   |      |

| ert   | 42.5   |      | 54.3   | +28  |

|       | 42.5   |      | 54     | 1    |

| Ctrl  | 42.5   |      | 52     | -2   |

|       | 42.5   |      | 49.5   | -2.5 |

|       |        |      |        |      |

# Hardware: Shelf Temperatures

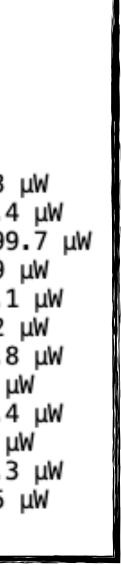

- Hub MiniPOD temps are read via IPbus/AXI interface to I2C

- Temps are quite low, typically around 30C. The Tx MiniPOD is in the Rx MiniPOD shadow, so a bit warmer.

- NB: Hub and ROD MiniPODs are not on the sensor I2C bus that the IPMC monitors. Rather, they are on an isolated I2C bus accessed via their FPGAs.

### **Example read of Hub miniPOD transmitter**

MiniPod type verified to be: recvr\_mpod MiniPod type verified to be: trans\_mpod Minipod internal temperature is 28.45 C Minipod internal temperature is 32.22 C The voltage on the 2.5 Vcc power supply is 2.4807 V The voltage on the 2.5 Vcc power supply is 2.4657 V The voltage on the 3.3 Vcc power supply is 3.2876 V The voltage on the 3.3 Vcc power supply is 3.2596 V The serial number of the current device: recvr\_mpod is : A1719407F The serial number of the current device: trans\_mpod is : A17285016 The operating time is 3052.0 hours or 127.1666666667 days The operating time is 3038.0 hours or 126.583333333 days Optical power for channel number recvr\_mpod is: 0 dBm or 0 µW, is module connected? Optical power for channel number trans\_mpod is: 0.14646524684 dBm or 1034.3 µW Optical power for channel number recvr\_mpod is: 0 dBm or 0 µW, is module connected? Optical power for channel number trans\_mpod is: 0.911039440903 dBm or 1233.4 µW Optical power for channel number recvr\_mpod is: 0 dBm or 0 µW, is module connected? Optical power for channel number trans\_mpod is: -0.00130307891732 dBm or 999.7 μW Optical power for channel number recvr\_mpod is: 0 dBm or 0 µW, is module connected? Optical power for channel number trans\_mpod is: 1.06496870139 dBm or 1277.9 μW Optical power for channel number recvr\_mpod is: 0 dBm or 0 µW, is module connected? Optical power for channel number trans\_mpod is: 0.137217780511 dBm or 1032.1 µW Optical power for channel number recvr\_mpod is: 0 dBm or 0 µW, is module connected? Optical power for channel number trans\_mpod is: 1.09646031091 dBm or 1287.2 µW Optical power for channel number recvr\_mpod is: 0 dBm or 0 µW, is module connected? Optical power for channel number trans\_mpod is: 0.152759066819 dBm or 1035.8 μW Optical power for channel number recvr\_mpod is: 0 dBm or 0 µW, is module connected? Optical power for channel number trans\_mpod is: 1.0510124455 dBm or 1273.8 µW Optical power for channel number recvr\_mpod is: 0 dBm or 0 µW, is module connected? Optical power for channel number trans\_mpod is: -0.220935723629 dBm or 950.4 μW Optical power for channel number recvr\_mpod is: 0 dBm or 0 µW, is module connected? Optical power for channel number trans\_mpod is: 1.3165073809 dBm or 1354.1 µW Optical power for channel number recvr\_mpod is: 0 dBm or 0 µW, is module connected? Optical power for channel number trans mpod is: 0.262471814778 dBm or 1062.3 µW Optical power for channel number recvr\_mpod is: 0 dBm or 0 µW, is module connected? Optical power for channel number trans\_mpod is: 1.20080134129 dBm or 1318.5 µW The nominal wavelenght for device trans mpod is 845.0 nm ( ± 15.015 nm)

• Thus, while we can read the ROD DCDC supplies and FPGA SysMon, we do not see the ROD MiniPODs directly.

### **Example read of Hub miniPOD receiver**

## Hardware: Interoperability Tests

### **FDR Action Item:**

Interoperability tests with close to final *jFEX* and *eFEX* prototype modules need to be performed. These tests have to done in a full size ATCA shelf with a backplane with the same characteristics as the one to be used in the experiment (ideally with the target shelf). Depending on the availability, interoperability tests with L1Topo should also be performed.

At the time of this review, the following interoperability tests have been performed on 40G qualified ATCA shelves: \* • FTM:

- @MSU: IBERT using the Hub clock as input. ROD also present for many tests.

- These tests have also been performed at RAL and Cambridge.

### • eFEX:

- @RAL & Cambridge: IBERT using the Hub clock as input. ROD also present for most tests.

- jFEX:

- @CERN: IBERT using the Hub clock as input. ROD also present for these tests.

### • L1Topo:

• No tests performed yet due to availability of hardware. Tests planned for this week.

Action items identified during the Hub Final Design Review have been presented. Nearly all items have been addressed

reviews

- Performance of Hub + ROD core features in a fully-populated shelf is very encouraging. • Excellent BER performance and open eye diagrams ○ FELIX→Hub→HTM clock and TTC/Combined data requirements are met

of the FDR report and further address Hub production readiness.

- Notably there are 3 FDR action items related to the ROD which must be addressed in ROD

Next presentation will cover tests of the Hub prototype modules that extend beyond the scope

W. Fisher, MSU