# **HUB FW overview**

- HUB FW development process split into several separate stages.

- **IPbus**

- $\rightarrow$  implemented and tested (passed)  $\rightarrow$  implemented and tested (passed)

- Readout Control (@6.4Gbps)

- Combined TTC/Data (@6.4Gbps)  $\rightarrow$  implemented and tested (passed)

- GBT (@4.8Gbps)

- Aurora8b/10b (6.4 Gbps)

- $\rightarrow$  implemented and tested (passed)

- $\rightarrow$  initially implemented and tested on the VU095 Internal loopback tests on the HUB module

- Final step  $\rightarrow$  merging process to provide the production firmware (HUB1 and HUB2) •

- Slice Tests in Cambridge and MSU good occasion to validate the firmware •

- Very comprehensive HUB diagnostic firmware includes several stages:

- (majority of these configurations are provided):

- config 1: IBERT (all Quads) @ 6.4 Gbps

- config 2: IBERT (all Quads) @10.24 Gbps

- - config 3: IBERT (all Quads) @ 6.4 Gbps; integrated with the IPbus

- config 4: IBERT (all Quads Quad224) @ 6.4 Gbps; integrated with the IPbus and GBT

- - config 5: IBERT (all Quads) @ 6.4 Gbps; integrated with the IPbus and GBT

- config 6: IBERT (all Quads) @10.24 Gbps; integrated with the IPbus and GBT

- - config 7: IBERT (all Quads) @ 6.4 Gbps; integrated with the GBT, IBERT controlled by IPbus

- config 8: IBERT (all Quads) @10.24 Gbps; integrated with the GBT, IBERT controlled by IPbus

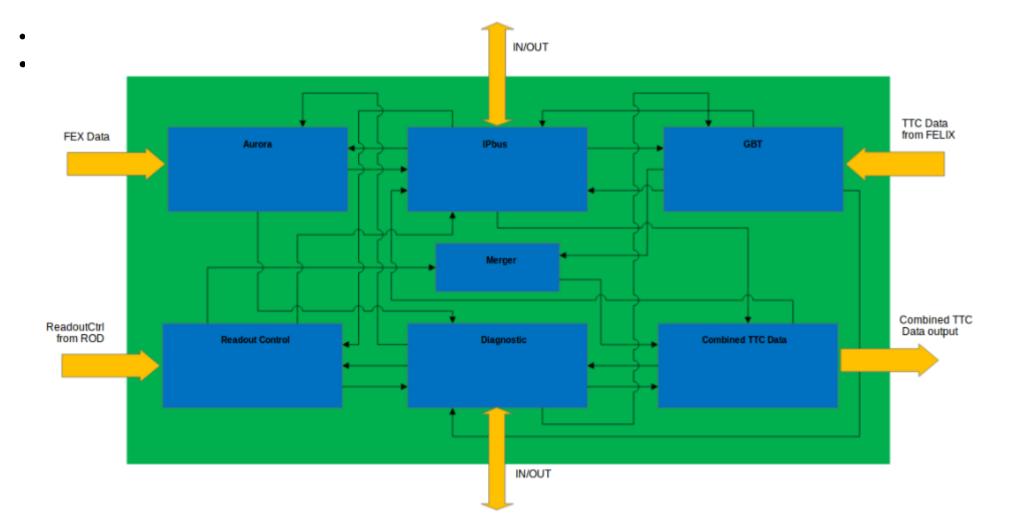

# **HUB FW diagram**

# **GBT, Combined\_TTC/DATA overview**

- HUB module is obliged to distribute TTC information throughout the shelf.

- The combined\_TTC/DATA bits are defined to provide TTC information as well

- as initialization functions (Aurora). The link is set to run at 6.4Gbps raw rate

- •

- The HUB uses MiniPOD optical receiver to receive TTC signals (GBT) from the FELIX system

- •

- •

- Receive the Reset signal (Aurora Initialization) from the Readout\_CTRL stream,

- then merging with the TTC info and distribute it to the appropriate shelf slot

- •

- -

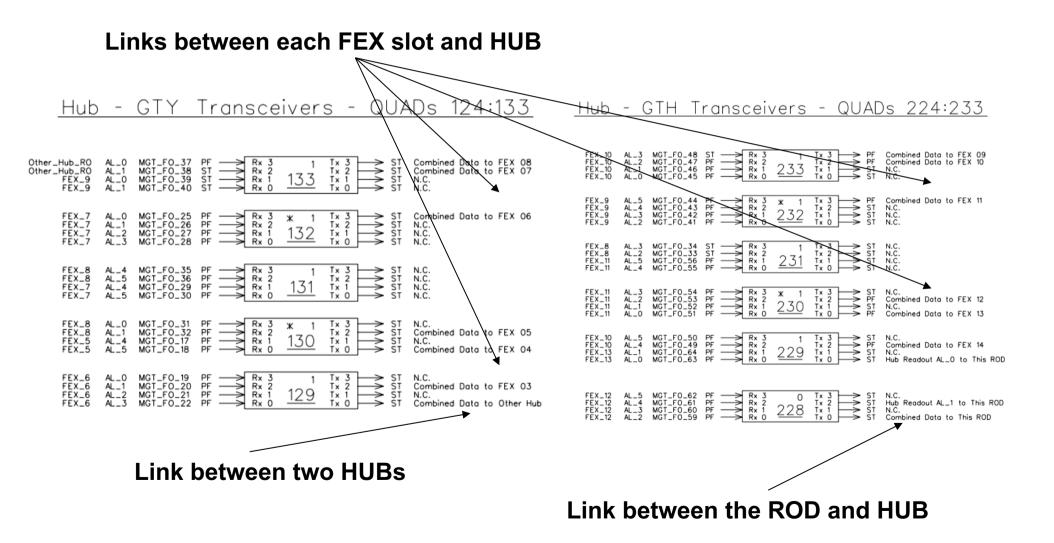

- Several Combined\_TTC links within the shelf; each FEX slot (3-14); one between

- each HUB and ROD; links between two HUBs

- •

- Combined\_TTC/DATA links on the HUB FPGA is implemented with use of several

- components, including the MGT transceivers (GTH and GTY), control and diagnostic logic

# Combined\_TTC/DATA Physical Implementation

- The Combined\_TTC/Data link on the HUB FPGA is implemented with the use of several components,

- including the MGT transceivers (GTH and GTY), control and the diagnostic logic.

- The Combined\_TTC/DATA link is designed to operate at 6.4 Gbps.

- The physical implementation of the Combined\_TTC/DATA stream assumes that there are 4 Control Registers on the Hub TX side, and Shadow Registers on the Rx side (Receiver: FEX, ROD and other HUB).

- The transmitter side generates the 128 bit message from 4 Control registers: Word\_0, Word\_1,

- Word\_2, and Word\_3. The transmitter side logic is in charge to write control information into these

- Control Registers. The contents of these registers are continuously transmitted to the modules

- (within the shelf) which receives the data into a duplicate set of 4 registers referred to as shadow registers. Anything written into a Control Register at the transmitter side will appear in the corresponding Shadow register at the receiving side within the following LHC clock.

- •

- The least significant byte of Word\_0 is reserved for the 8b10b Comma character K28.5.

# Combined\_TTC/DATA Bit definition

Combined\_TTC/DATA bit definitions: The least significant byte of Word\_0 is reserved for the 8b10b Comma Character K28.5

| word 0     |                        | word 1   |          | word 2 |                 | word 3     |                  |

|------------|------------------------|----------|----------|--------|-----------------|------------|------------------|

| <u>bit</u> | 0XBC = K28.5           | bit      |          | bit    |                 | <u>bit</u> |                  |

| 0          | 0                      | 0        | L1ID(0)  | 0      | control channel | 0          | Link_reset(0)    |

| 1          | 0                      | 1        | L1ID     | 1      | control channel | 1          | Link_reset(1)    |

| ~          | 1                      | 2        | L1ID     | 2      | control channel | 2          | Link_reset(2)    |

| 3          | 1                      | 3        | L1ID     | 3      | control channel | 3          | Link_reset 3     |

| 4          | 1                      | 4        | L1ID     | 4      | control channel | 4          | Link_up(0)       |

| 5          | 1                      | 5        | L1ID     | 5      | control channel | 5          | Link_up(1)       |

| 6          | 0                      | 6        | L1ID     | 6      | control channel | 6          | Link_up(2)       |

| 7          | 1                      | 7        | L1ID     | 7      | control channel | 7          | Link_up(3)       |

| 8          | version(0)             | 8        | L1ID     | 8      | control channel | 8          | Link Enable(0)   |

| 9          | version(0)             | 9        | L1ID     | 9      | control channel | 9          | Link Enable(1)   |

| 10         | version(2)             | 10       | L1ID     | 10     | control channel | 10         | Link Enable(2)   |

| 10         | version(2)             | 10       | L1ID     | 10     | control channel | 10         | Link Enable(2)   |

| 12         | version(5)             | 11       | L1ID     | 11     | control channel | 11         | ROD XOFF         |

| 13         |                        | 12       | L1ID     | 13     | control channel | 12         | 0 (ROD reserved  |

| 13         |                        | 13       | L1ID     | 13     | control channel | 13         | 0 (ROD reserved  |

| 15         | reserved               | 15       | L1ID     | 15     | control channel | 15         | 0 (ROD reserved) |

| 15         | leserveu               | 15       | LID      | 15     | control channel | 15         | U(KOD Teserveu)  |

| 16         | L1A                    | 16       | L1ID     | 16     | control channel | 16         | 0 (ROD reserved) |

| 17         | BCR                    | 17       | L1ID     | 17     | control channel | 17         | 0 (ROD reserved) |

| 18         | ECR                    | 18       | L1ID     | 18     | control channel | 18         | 0 (ROD reserved) |

| 19         | Privileged Readout     | 19       | L1ID     | 19     | control channel | 19         | shelf(0)         |

| 20         | felix backpressure(0)  | 20       | L1ID     | 20     | control channel | 20         | shelf(1)         |

| 21         | felix backpressure(1)  | 21       | L1ID     | 21     | control channel | 21         | shelf (2)        |

| 22         | felix backpressure(2)  | 22       | L1ID     | 22     | control channel | 22         | shelf(3)         |

| 23         | felix_backpressure(3)  | 23       | L1ID(23) | 23     | control channel | 23         | CRC (9-bit)      |

| 24         | faliu hadunaaaura(A)   | 24       |          | 24     | control channel | 24         |                  |

| 24         | felix_backpressure(4)  | 24       | ECRID(0) | 24     | control channel | 24         | CRC (9-bit)      |

|            | felix_backpressure(5)  |          | ECRID(1) |        |                 |            | CRC (9-bit)      |

| 26         | felix_backpressure(6)  | 26<br>27 | ECRID(2) | 26     | control channel | 26         | CRC (9-bit)      |

| 27         | felix_backpressure(7)  |          | ECRID(3) |        | control channel | 27         | CRC (9-bit)      |

| 28         | felix_backpressure(8)  | 28       | ECRID(4) | 28     | control channel | 28         | CRC (9-bit)      |

| 29         | felix_backpressure(9)  | 29       | ECRID(5) | 29     | control channel | 29         | CRC (9-bit)      |

| 30         | felix_backpressure(10) | 30       | ECRID(6) | 30     | control channel | 30         | CRC (9-bit)      |

| 31         | felix_backpressure(11) | 31       | ECRID(7) | 31     | control channel | 31         | CRC (9-bit)      |

Specification for Readout Control & Combined TTC Serial links in L1Calo (ver.0.5)

# Combined\_TTC/DATA Link placement

### **Readout\_Control overview**

- The HUB module is obliged to receive the Readout Control (Readout\_CTRL) information from the ROD via serial link named Readout\_CTRL. The HUB module is the only one module within the shelf which gets the Readout Control data from the ROD

- That information is used by the Hub, also fanned out to the rest of the system. The main purpose is to provide resets to all of the data links (Aurora) between the Fex's and the ROD plus HUB module

# Readout\_Control Physical Implementation

- The Readout\_Ctrl link on the HUB module is implemented with the use of MGT Transceiver GTH,

- control and diagnostic logic

- •

- The Readout\_Ctrl link is designed to operate at 6.4 Gbps.

- •

- In order to to control message transmission within a single LHC clock period, the length of the message

- is limited to 128 bits

- ٠

- The HUB Readout Control FW features one receiver (RX). In order to debug the design, the standard

Xilinx diagnostic components are being used to monitor the data flow (as for example like the ILA and VIO)

- VIO).

- The physical layer is configured with the use of GT wizard

- ٠

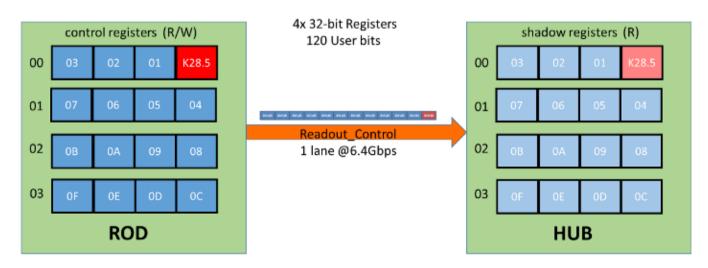

- The physical implementation of the Readout\_CTRL links assumes that there are Control Registers on

- the Tx ROD side, and Shadow Registers on the Rx HUB side. The transmitter side generates the 128

- bit message from 4 Control registers: Word\_0, Word\_1, Word\_2, and Word\_3. The transmitter side

- logic is in charge to write control information into these registers for transmission to the modules

- within the shelf. These registers are continuously transmitted to the HUB which receives the data into

- a duplicate set of 4 registers referred to as Shadow Registers. Anything written into a Control Register

- at the transmitter side will appear in the corresponding Shadow register at the receiving side within the

- following LHC clock.

- •

- 8

#### **Control and Shadow Register**

#### There are Control Registers on the TX side and Shadow Register on the RX side

Figure 1: Control and Shadow Registers

# Readout\_Control Bit definition

- The bits within the Readout Control words are primarily defined to provide initialization functions for

- all of the FEX data links

| und 0.     |                         | amod 1     |                              | and 2      |                      | und 3 |                     |

|------------|-------------------------|------------|------------------------------|------------|----------------------|-------|---------------------|

| <u>hit</u> | OX8C = K285             | <u>hit</u> |                              | <u>hit</u> |                      | hit.  |                     |

| 0          | 0                       | 0          | slot 3 link eset             | 0          | slot 3channel up     | 0     | slot 3LinkEnable    |

| 1          | 0                       | 1          | slot 4 link reset (0)        | 1          | slot4channel.up(0)   | 1     | slot4LinkEnable     |

| 2          | 1                       | 2          | slot5 link reset (0)         | 2          | slotS channel up (0) | 2     | slot5LinkEnable     |

| 3          | 1                       | 3          | slot 6link reset             | 3          | slot 6channel up     | 3     | slot 6LinkEnable    |

| 4          | 1                       | 4          | slot7 link reset             | 4          | slot7 channel up     | 4     | slot7LinkEnable     |

| 5          | 1                       | 5          | slot8 link reset (0)         | 5          | slotSchannel up(0)   | 5     | slot8LinkEnable     |

| 6          | 0                       | 6          | slot 9 link reset (C)        | 6          | slot9 channel up (0) | 6     | slot9 LinkEnable    |

| 7          | 1                       | 7          | slot 10 link reset           | 7          | slot10channel up     | 7     | slot 10 Link Enable |

| 8          | version0                | 8          | slot 11 link reset           | 8          | slot11 channel up    | 8     | slot 11 Link Enable |

| 9          | version1                | 9          | slot12linkreset (0)          | 9          | slot12channel.up(0)  | 9     | slot 12 Link Enable |

| 10         | version 2               | 10         | slot13linkreset (0)          | 10         | slot13channel.up(0)  | 10    | slot 13 Link Enable |

| 11         | version 3               | 11         | slot 34 link reset           | 11         | slot14 channel up    | 11    | slot 14 Link Enable |

| 12         | 0                       | 12         | 0                            | 12         | 0                    | 12    | 0                   |

| 13         | 0                       | 13         | slot 4 link reset (1)        | 13         | slot4channel up (1)  | 13    | 0                   |

| 14         | ROD XOFF (to all slots) | 14         | slot 4 link reset (2)        | 14         | slot4channel up (2)  | 14    | 0                   |

| 15         | Global Link Reset       | 15         | slot 4 link reset (3)        | 15         | slot4channel.up(3)   | 15    | 0                   |

| 16         | 0                       | 16         | slot5 link reset (1)         | 16         | slotS channel up (1) | 16    | 0                   |

| 17         | 0                       | 17         | slot 5 link reset (2)        | 17         | slot5 channel up (2) | 17    | 0                   |

| 18         | 0                       | 18         | slot5 link reset (3)         | 18         | slot5 channel up (3) | 18    | 0                   |

| 19         | 0                       | 19         | slot8 link reset (1)         | 19         | slot8 channel up (1) | 19    | shelf(0)            |

| Ð          | 0                       | ZD         | slot8 link reset (2)         | 20         | slot8 channel up (2) | D     | shelf(1)            |

| 21         | 0                       | 21         | slot8 link reset (3)         | 21         | slot8 channel up (3) | 21    | shelf (2)           |

| 22         | 0                       | 22         | slot9 link reset (1)         | 22         | slot9 channel up (1) |       | shelf(3)            |

| 23         | 0                       | 23         | slot9 link reset (2)         | 23         | slot9 channel up (2) | 23    | CRC (9- bit)        |

| 24         | 0                       | 24         | slot9 link reset (3)         | 24         | slot9 channel up (3) | 24    | CRC (9- bit)        |

| z          | 0                       | Z          | slot12linkreset (1)          | Z          | slot12channel up (1) | 25    | CRC (9- bit)        |

| 26         | 0                       | 26         | slot12linkreset (2)          | 26         | slot12channel up (2) | 26    | CRC (9- bit)        |

| 27         | 0                       | 27         | slot12link <i>r</i> eset (3) | 27         | slot12channel up (3  | 27    | CRC (9- bit)        |

| 洒          | 0                       | 25         | slot13link <i>r</i> eset (1) | 26         | slot13channel up (1) | 28    | CRC (9- bit)        |

| Э          | 0                       | Э          | slot13linkreset (2)          | 29         | slot13channel up (2) | Э     | CRC (9- bit)        |

| 30         | 0                       | 30         | slot13link <i>r</i> eset (3) | 30         | slot13channel up (3  | 30    | CRC (9- bit)        |

| 31         | 0                       | 31         | 0                            | 31         | 0                    | 31    | CRC (9- bit)        |

Specification for Readout Control & Combined TTC Serial links in L1Calo (ver.0.5)