# **ATLAS Level-1 Calorimeter Trigger Update**

# **HUB Firmware Specification**

# **Draft for PRR**

Version: 1.3

**09 December 2018**

# Table of Contents

| 1.0 FEX HUB Overview                            | 3  |

|-------------------------------------------------|----|

| 1.1 HUB Functionality                           | 3  |

| 1.1.1 Support of the ROD Mezzanine              | 3  |

| 1.1.2 FEX and FEX-HUB Readout Data Distribution | 3  |

| 1.1.3 TTC Clock and Data Stream Distribution    | 4  |

| 1.1.4 Ethernet Network Switch                   | 4  |

| 1.1.5 Slow Control (Ipbus to HUB and ROD)       | 4  |

| 2.0 IPbus Register Map                          | 12 |

| 3.0 TTC clock recovery/GBT                      | 18 |

| 3.1 Implementation                              | 18 |

| 3.2 Latency Measurements                        | 19 |

| 4.0 Readout Control                             | 23 |

| 4.1 ROD power-up scheme                         | 23 |

| 4.2 Control Bit Definition                      |    |

| 4.3 Readout Control/Implementation              | 27 |

| 5.0 Combined TTC                                | 29 |

| 5.0 CombinedTTC/Implementation                  | 29 |

| 5.1 Control bits definition                     | 33 |

| 5.2 Latency Measurements                        | 36 |

# 1. HUB overview

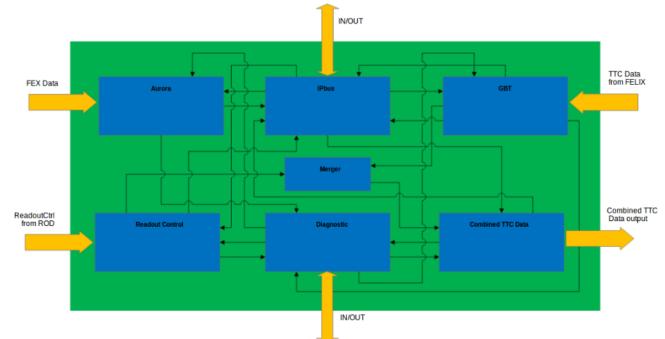

The Hub module is an integral part of the L1Calo system. Its primary functions are to support FEX system readout, provide switching functionality for module control and DCS IPbus networks and to distribute timing and control signals to the FEX modules. There are to be two Hub modules per shelf. Both Hub modules will receive multi-gigabit FEX data over the ATCA Fabric Interface, which will be fanned out to a ROD mezzanine on the Hub and to the Hub's own FPGA. This high-speed data path will include two data channels from the other Hub module. The Hub module in logical slot 1 will provide switching capability for a network that routes module control signals on the base interface, while the Hub in logical slot 2 will provide switching for a network that routes DCS information. The Hub module in slot 1 will further receive TTC information from the FELIX system, and these signals will be decoded and fanned out to the FEX modules, ROD modules and also to the Hub in slot 2. The fanned-out TTC control data stream will be interleaved with ROD-to-FEX communications including, for example, backpressure signals. The Hub module has connections to the other slots in the ATCA shelf over three distinct electrical interfaces. ATCA backplane Zone-2 consists of the Fabric Interface and the Base Interface. The Fabric Interface provides 8 differential pairs (channels) from each node slot to each Hub slot (8 to Hub-1 and 8 to Hub-2). There are a total of 8 Fabric Interface channels between Hub-1 and Hub-2 (not 16 total). The Fabric Interface pairs have a nominal bandwidth specification of 10 Gbps / channel. The Base Interface provides 4 differential pairs between each node slot and each Hub slot. There are a total of 4 Base Interface channels between Hub-1 and Hub-2. The Base Interface lines have a nominal bandwidth specification of 500 Mbps / channel, suitable for Gbps Ethernet protocol. Finally, ATCA backplane Zone-1 provides each node and Hub slot with a connection to the Intelligent Platform Management Bus (IPMB) with a total bandwidth of 100 kbps. The Hub module will provide MPO connectors in the ATCA Zone-3 region, which will allow for the routing of fiber-optic cables to/from the MiniPODs on the Hub and ROD modules. The L1Calo FEX-Hub system will consist of eight modules. There will be two eFEX shelves, one iFEX shelf and one L1Topo shelf, each hosting two Hub modules.

# **1.1 HUB Functionality**

# 1.1.1 Support of the ROD Mezzanine Card

The FEX Hub physically holds the ROD Mezzanine Card and provides electrical connections to it through two 400 pin Meg-Array connectors.

# 1.1.2 FEX and Hub Readout Data Distribution

The Hub receives over the Fabric Interface 6 serial streams of Readout Data from each FEX Module. Each FEX-Hub also receives over the Fabric Interface 2 serial streams of Readout Data from the other FEX-Hub in the crate. These 74 high speed serial streams are fanned out on the FEX-Hub. One copy of each stream is sent to the ROD and one copy is sent to the Hub's own UltraScale FPGA. The Hub FPGA also sends 2 serial streams with its own Readout Data to its own ROD. Each ROD thus receives a total of 76 high speed Readout Data streams: 6 streams from each FEX, 2 streams from the local Hub FPGA and 2 streams from the other Hub's Hub FPGA. The data rate per readout stream will be 10 Gbps or less.

# 1.1.3 TTC Clock and Data Stream Distribution

The Hub in Slot 1 uses a 12-channel MiniPOD optical receiver to receive TTC signals from the upstream FELIX system. The FEX-Hub receives two types of TTC signals: a copy of the LHC clock and TTC control data. These signals need to be fanned out to each FEX module, to the local ROD, to the local Hub FPGA and to the FEX-Hub in Slot 2 (including its ROD). The LHC clock is directly forwarded without any processing on the FEX-Hub. The TTC control data will be merged with additional control information coming from the ROD module from each FEX-Hub before being fanned out. The FEX-Hub uses two ports from the Fabric Interface Channel to each Node Slot to fanout these two signals to each FEX. These two TTC and control signals sent to the FEX plus the 6 Readout Data streams received from each FEX use all 8 signals pairs of each Fabric Channel connecting one FEX to the FEX-Hub, albeit with an unconventional port direction usage. The FEX-Hub in Slot 2 does receive the TTC information from FELIX directly, but receives the TTC Clock and the TTC/ROD readout control stream from the FEX-Hub in Slot 1. The FEX-Hub in Slot 2 sends any required ROD readout control data generated by its own ROD to the FEX-Hub in Slot 1 for inclusion in the combined TCC/ROD readout control data stream.

# 1.1.4 Ethernet Network Switch

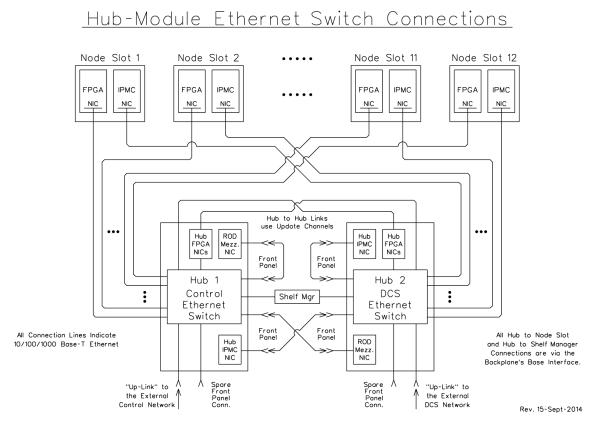

The FEX-Hub hosts an un-managed 10/100/1000 Base-T switch to provide the following 19 Gigabit Ethernet connections [see Figure 1]:

- 1 connection on the front panel for the "up-link"

- 12 connections to the "FEX Node" modules in this crate via the Base Channel Fabric

- 1 connection to the ROD on this Hub (or IPMC on the other Hub) via the front panel

- 1 connection to the ROD on the other Hub (or IPMC on this Hub) via the front panel

- 1 connection to the other Hub's UltraScale FPGA via the Update Channel Interface

- 1 spare front panel connection

# 1.1.5 Slow Control (IPbus to HUB and ROD)

HUB: An IPbus interface provides high-level, functional control of the FEX-Hub module. This allows, for example, setting any firmware parameters, controlling modes of operation and reading monitoring data. Figure below shows the Hub's Base Interface Ethernet Switch in the context of the other cards in the ATCA shelf. ROD: An Ethernet link is provided from the main ROD FPGA to the Ethernet switch on the Hub. This will allow a computer using IPbus to:

- Access registers within the ROD FPGA, setting parameters and controlling modes of operation.

- Store FPGA configurations into the SPI-Flash Configuration Memory.

- Initiate the loading of configurations from the SPI-Flash.

This can be used to load a configuration from one of a number of other SPI-Flash sectors. These sectors can be written via IPbus.

Figure 1: Illustration of FEX-Hub Ethernet network connections.

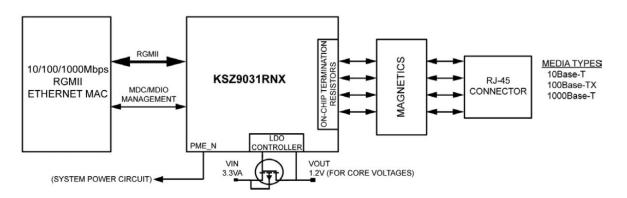

The Hub Module requires two physical chips for the Ethernet Base Interface connections to its FPGA (Micrel KSZ9031RNX <u>http://ww1.microchip.com/downloads/en/DeviceDoc/00002117B.pdf</u> – it can operate with a 1.8V RGMII port and thus directly connect to the Virtex7 HP I/O pins). Two FPGA MACs are connected to the physical chips via RGMII ports. This chip has both the RGMII signal connection to the FPGA that is used to move the actual Ethernet data and provides access to internal registers and also has a 2 wire serial "Management Data" port.

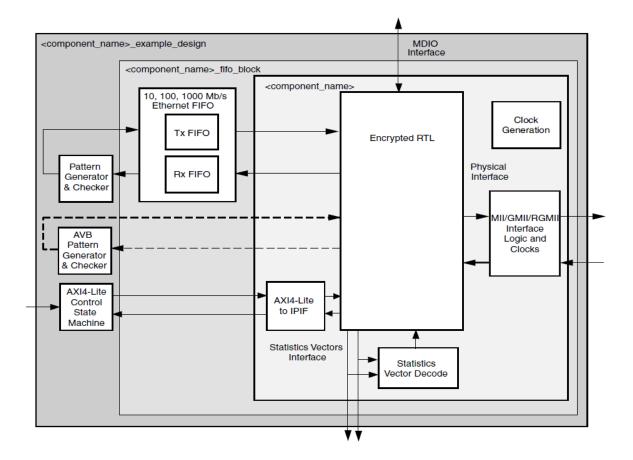

Figure 2: Illustration of Xilinx ETHERNET MAC IP and PHYS chip (KSZ9031RNX).

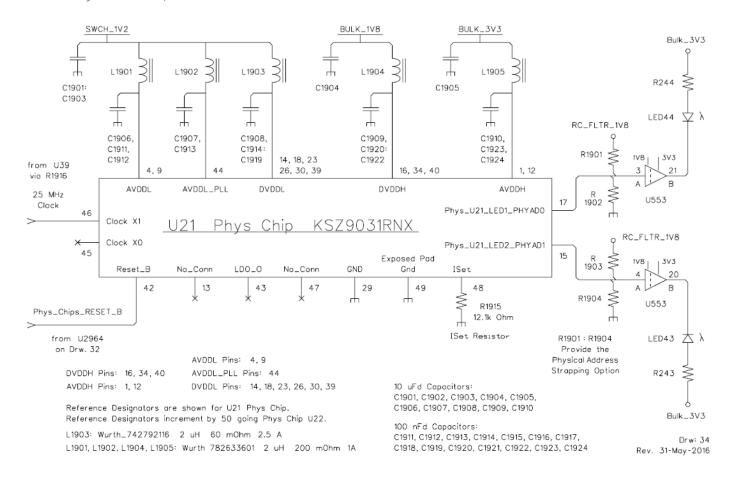

# Phys Chip - Power, Clock, Reset, and LED Circuits

Figure 3: Schematic view of U21 Phys chip: Power, Clock, Reset.

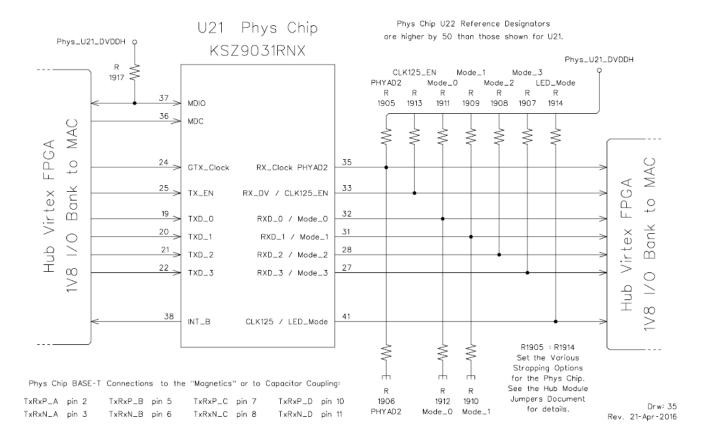

# Phys Chip - RGMII, MDC/DMIO, and Base-T Circuits

Figure 4: Scheme of Phys Chip: RGMII, MDC/DMIO, and Base-T Circuits.

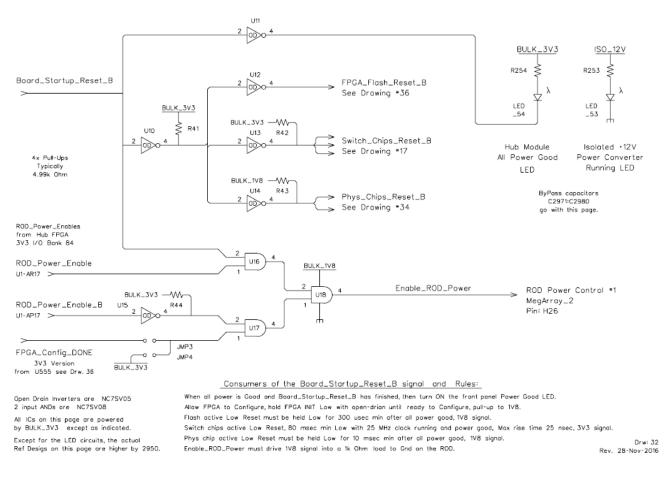

# Board Reset Distribution - ROD Power Control

Figure 5: Board Reset Distribution, ROD Power Control.

For each of its two Ethernet Phys Chips (PHY) the Hub's FPGA will need to instance a MAC that supports an RGMII connection (along with MDIO/MDC lines) to the PHY. All of these signals to/from the PHY are currently routed through the 1V8 HP Select I/O Bank 68.

After power-up the KSZ9031RNX is configured to RGMII mode if the MODE [3:0] strap-in pins are set to one of the RGMII mode capability options.

There is no reset signal to the KSZ9031RNX from FPGA. An ad hoc manual push button was attached to the PHY chip on the HUB for debugging purposes.

The KSZ9031RNX RGMII port connects to HP I/O pins on the FPGA. The RGMII port consists of 12 signals:

- Transmit Clock to the KSZ9031RNX

- Transmit Control (enable) to the KSZ9031RNX

- Transmit Data 0:3 to the KSZ9031RNX

- Receive Clock from the KSZ9031RNX

- Receive Control (enable) from the KSZ9031RNX

- Receive Data 0:3 from the KSZ9031RNX

The KSZ9031RNX includes a MII Management port. This type of port is also called MDIO Management Data Input/Output. This port allows higher-level devices to monitor and control the KSZ9031RNX. This port allows direct access to the IEEE defined MIIM registers, and the vendor specific registers. This port also allows indirect access to the MMD address space and registers. This port consists of signals: MDC - the clock and MDIO - the data line.

The Hub Module has two KSZ9031RNX PHY chips. There are 14 jumpers associated with each of these PHY chips. These jumpers are resistors that bias a pin in one direction or the other and this value is read when the PHY chip first powers up or is reset.

The KSZ9031RNX has 9 pins (called "Strapping Options") that are read in this way at power up. Because of space limitations and because there is an obvious why that the Hub Module wants some of these Strapping Options set, 4 of them have only one jumper to pull that pin in the direction that is obviously needed for rational operation of the Hub Module.

The PHYADx jumpers set the address of the Management Interface Port on the KSZ9031RNX. The Management Port PHYAD bits 3 and 4 are internally always set to 0,0. Bits 2, 1 and 0 set to Low. Therefore, the PHYADx set to 0.

The Hub Module provides easy control of only the Mode\_0 and Mode\_1 lines. This provides the following 4 options for the Phys chip (Mode bits listed Mode\_3, ..., Mode\_0).

- 1100 RGMII 1000 Base-T full duplex only

- 1101 RGMII 1000 Base-T full or half duplex

- 1110 RGMII 10/100/100 all but 1000 half duplex

- 1111 RGMII 10/100/1000 full or half duplex

Mode: SET MODE {3..0} = 1100 - RGMII 1000 Base-T full duplex only

The Xilinx Tri-Mode Ethernet MAC core is a parameterizable core, in 1000 Mbps mode, the TEMAC core can also connect with industry standard PHY devices. Optional MDIO interface to managed objects in PHY layers (MII Management).

Figure 6: Scheme of Xilinx MAC Example HDL Design (UltraScale).

The following design approach is based on the suggestion by Ed Flaherty (University of Cambridge): Step 1: Generate Xilinx MAC Example Design (UltraScale RGMII).

Step 1. Generate Allinx MAC Example Design (Ultrascale RGM

Step 2: Modify the Example Design to HUB board hardware.

Step 3: Generate Tx packets with built-in Simple Frame Generator and capture them in Wireshark.

Step 4: Packet generation logic replaced with simple read fifo (Rx looped back to Tx).

Step 5: Packets sent from server (Ostinato) returned via the loopback proving Rx and Tx paths.

Step 6: Use Wireshark to check returned packets

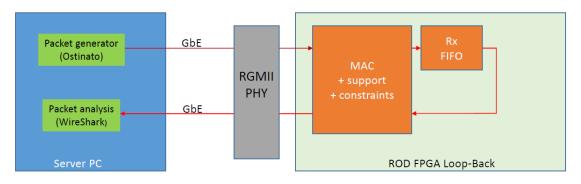

# IPBus porting: 3 Steps Step 2: Stripped down RGMII Example Design

#### Stripped-down example design

- Packet generation logic replaced with simple read fifo (looped back)

- · All of the example design MAC+Support logic and constraints retained

- Verification: Packets sent from server were returned via the loopback proving Rx and Tx paths

Ed Flaherty 7-June-2016

Figure 7: IPBus porting.

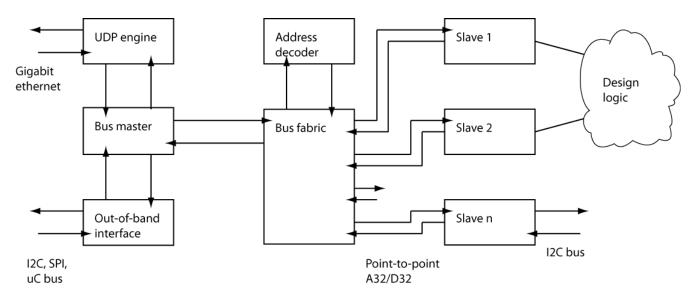

As soon as the MAC part works, the IPbus control part and the IPbus slaves can be added to the design, as described in the note: Notes on Firmware Implementation of an IPbus SoC Bus, V1.0 23/5/2012, DMN".

Figure 8: IPBus topology.

The SoC bus is fully synchronous, and operates from a single system clock. There is no constraint on the relationship of the bus clock to the 125MHz GbE clock, as the firmware contains handshaking logic. For slaves, which do not require wait states, the 32b data path on the SoC bus allows full utilization of the Ethernet interface as long as it runs at >32MHz; this allows straightforward timing closure for complex multi-slave designs. Designs therefore typically drive the Ipbus clock at <sup>1</sup>/<sub>4</sub> of the GbE clock (i.e. 31.25MHz).

#### 2. IPbus Register Map

Current Rev. 05-Nov-2018 All IPbus registers are 32-bit. Address is HEX Bit allocation inside the register can be changed if needed Overview: (\*) - not all bits are implemented \_\_\_\_\_ 1. Set of registers for the external FPGA control/status pins (IO) 00000000 RW control HUB + HTM(\*) HUB + HTM 00000001 RW lock HUB + HTM HUB + HTM 00000002 RW leds 00000003 RW test

HUB + HTM

00000004

RO module

HUB + HTM

00000005

RO address

HUB + HTM(\*)

00000006

RO status

HUB + HTM(\*)

00000007

RO tmp

2. Test/Monitoring registers 00000008-0000000F testreg HUB + HTM 8 registers 00000010 RW w count HUB + HTM

00000008-0000000 restreg

HUD + HTM

00000010 RW w\_count

HUB + HTM

00000011 RW r\_count

HUB + HTM

00001000-000013FF ram

HUB + HTM

00002000 RW pram\_addr

HUB + HTM

00002001 RW pram\_data

HUB + HTM

3. Block of 8 GPIO RW registers in the FPGA Block Design for tests 40000000-40070000 gpio regs HUB + HTM 8 registers 4. Transmitter and Receiver MiniPOD Control registers 40800000 Trans\_MiniPOD HUB + HTM 40810000 Recvr MiniPOD HUB + HTM 5. Registers for the interface to the DCDC Converters 40820000 DCDC Converters HUB 6. Registers for the interface to the Si Lab 5338A 40830000 HTM's SiLab 5338A нтм 7. Registers for the interface to the switches 40E00000 Chip A HUB 40E10000 Chip B HUB 40E20000 Chip C HUB 8. System Monitor registers 44A00000 System Monitor HUB + HTM 9. Test registers

9. Test registers

0000012 RW test2

HUB + HTM

00001400 RW test3

HUB + HTM

00002002 RW test4

HUB + HTM

40080000 RW test5\_1

HUB + HTM

40801000 RW test5\_2

HUB + HTM

40811000 RW test5\_3

HUB + HTM

40821000 RW test5\_4

HUB + HTM

40831000 RW test5\_5

HUB + HTM

| 40E01000<br>40E11000 | RW | test5_7       | HUE | 3 + | HTM<br>HTM |

|----------------------|----|---------------|-----|-----|------------|

| 40E21000             |    | · · · · · _ · |     |     | HTM        |

| 44A01000             | RW | test5_9       | HUE | 5 + | HTM        |

10. Control/status registers for the internal FPGA logic - TBD

Additional information about HUB/HTM FPGA signal Types can be found in: HUB: https://web.pa.msu.edu/hep/atlas/l1calo/hub/hardware/details/hub\_0\_ab\_fpga\_signal\_types.txt HTM: https://web.pa.msu.edu/hep/atlas/l1calo/htm/hardware/details/htm fpga mezz connections.txt

1. Set of registers for the external FPGA control/status pins (IO)

| Addr     | Туре | Name    | Content                                                                             | Bit                                     | Comment              |

|----------|------|---------|-------------------------------------------------------------------------------------|-----------------------------------------|----------------------|

| 00000000 | RW   | control | <pre>fex_clk_en mgt_equ_en i2c_buf_en spare rod_pwr_en ? rod_pwr_en_b ? spare</pre> | [16]<br>[15]<br>[14]<br>[13-11]<br>[10] | Enable clock to FEXs |

This is control register for the individual pins (exeption - other\_hub\_Clk, Drw: 40A) All bits set to '0' after power-on.

HUB: all bits are implemented HTM: only bits with (\*) are implemented - mpod\_rst\_b

NB: rod\_pwr\_en and rod\_pwr\_en\_b needs clarification

| Addr     | Туре | Name | Content     | Bit                  | Comment                                |

|----------|------|------|-------------|----------------------|----------------------------------------|

| 00000001 | RW   | lock | arbitration | [31:2]<br>[1]<br>[0] | access key<br>lock bit<br>watchdog bit |

A single R/W register to arbitrate access between multiple IPbus clients and implement timeout Bits 31 downto 2 provide an access key, bit 1 is the lock bit, bit 0 is the watchdog bit Generic IPbus arbitration, David Sankey, Monday, 12 June 2017: https://indico.cern.ch/event/641268/

| Addr     | Туре | Name | Content | Bit               | Comment                                                                |                                                              |                                                                                                                                              |

|----------|------|------|---------|-------------------|------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 00000002 | RW   | leds | LEDs    | [31]              | leds_control                                                           |                                                              |                                                                                                                                              |

|          |      |      |         | [2]<br>[1]<br>[0] | HUB:<br>Front palnel led50<br>Front palnel led51<br>Front palnel led52 | HTM:<br>[7]<br>[6]<br>[5]<br>[4]<br>[3]<br>[2]<br>[1]<br>[0] | LED_1_TOP_CONTROL<br>LED_2_CONTROL<br>LED_3_CONTROL<br>LED_4_CONTROL<br>LED_5_CONTROL<br>LED_6_CONTROL<br>LED_7_CONTROL<br>LED_8_BOT_CONTROL |

This register is implemented in the HUB and the HTM

Lower two LEDs display the IPbus Rx and Tx transactions when leds\_control is set to '0' (also after power-on),

HUB:HTM:Front palnel led51 <= IPbus pkt\_rx\_led;</td>LED\_7\_CONTROL <= IPbus pkt\_rx\_led;</td>Front palnel led52 <= IPbus pkt\_tx\_led;</td>LED\_8\_BOT\_CONTROL <= IPbus pkt\_tx\_led;</td>

When leds control is set to '1', they are controlled by this register (see above).

All other LEDs are controlled by this register independently of leds\_control.

| Addr      | Туре  | Name         | Content          | Bit               | Comment                                                                                          |

|-----------|-------|--------------|------------------|-------------------|--------------------------------------------------------------------------------------------------|

| 00000003  | RW    | test         | ******           | [31:0]            | test register                                                                                    |

| Addr      | Туре  | Name         | Content          | Bit               | Comment                                                                                          |

| 00000004  | RO    | module       |                  | [23:16]<br>[15:8] | HUB: X"01" HTM: X"02"<br>HUB: X"01" HTM: X"01"<br>HUB: X"01" HTM: X"01"<br>HUB: X"01" HTM: X"01" |

| This is s | tatus | information, | set internally i | n the FW,         | will be properly set upou decision.                                                              |

| Addr     | Туре | Name    | Content                                           | Bit     | Comment                                                                                                                 |

|----------|------|---------|---------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------|

| 00000005 | R0   | address | shelf_addr<br>slot_addr *<br>addr_to_rod<br>spare | [23:16] | Shelf Address from the IPMC<br>Backplane Hardware Slot Address<br>Hardware Address to the ROD (generated)<br>spare bits |

\_\_\_\_\_

This is external information (shelf adrs and slot adrs) and internally generated (addr to rod).

HUB: all bits are implemented

HTM: only bits with (\*) are implemented - Backplane Hardware Slot Address

| Addr     | Туре | Name                           | Content           | Bit          | Comment                                                                     |

|----------|------|--------------------------------|-------------------|--------------|-----------------------------------------------------------------------------|

| 00000006 | RO   | status                         | pll_lock *        |              | From PLL lock circuits - pll40_lock<br>From PLL lock circuits - pll320_lock |

|          |      |                                | phy_int *         |              | From Eth Phy chips - phyU21_int_b                                           |

|          |      |                                | mpod_int *        |              | From the MiniPODs - trans_mpod_intr_b                                       |

|          |      |                                | hub smb alert     |              |                                                                             |

|          |      |                                |                   |              | From the Power Control circuits                                             |

|          |      |                                | rod present b     |              |                                                                             |

|          |      |                                | rod_smb_alert_b   | [22]         | Power supply problem on the ROD                                             |

|          |      |                                | rod_status        |              | ROD power                                                                   |

|          |      |                                |                   | [20]         | 5                                                                           |

|          |      |                                | rod_status        |              |                                                                             |

|          |      |                                | sw_loop_det       | [18]<br>[18] | Broadcom Switch chips switch a loop det                                     |

|          |      |                                |                   | [18]         |                                                                             |

|          |      |                                | spare             |              | spare bits, set to all zeros                                                |

|          |      | s informatior<br>re implemente | n from individual | pins.        |                                                                             |

|          |      |                                |                   | [31]         | PLL_40_MHZ_LOCKED_MON                                                       |

| -        |      |                                | -                 |              | ETH2 INT                                                                    |

|          |      |                                |                   | [27]         | MP_TRANS_INTR                                                               |

|          |      |                                |                   | [26]         | MP_REC_INTR                                                                 |

|          |      |                                | Content           | Bit          | Comment                                                                     |

| 00000007 | RO   |                                | test_bits         | [31:0]       | for tests, now set to all zeros                                             |

2. Test/Monitoring registers

Addr

Type Name

Content

Bit

Comment

00000008- RW

testreg

xxxxxxxx

[31:0]

8 test RW registers

0000000F

Block of 8 RW registers in the FPGA logic for tests

| Addr                 | Туре | Name               | Content             | Bit | Comment                                     |

|----------------------|------|--------------------|---------------------|-----|---------------------------------------------|

| 00000010<br>00000011 |      | w_count<br>r_count | xxxxxxx<br>xxxxxxxx |     | Write packet counter<br>Read packet counter |

These two registers are packet counters for monitoring packet loss Counters are reset by any write

| Addr                  | Туре     | Name                   | Content         | Bit             | Comment                                                           |

|-----------------------|----------|------------------------|-----------------|-----------------|-------------------------------------------------------------------|

| 00001000-<br>000013FF | RW       | ram                    | block ram       | [31:0]          | 1Kword array of registers                                         |

| Addr                  | Туре     | Name                   | Content         | Bit             | Comment                                                           |

| 00002000              | RW<br>RW | pram_addr<br>pram_data | address<br>data | [9:0]<br>[31:0] | 1Kword test RAM pointer register<br>1Kword test RAM data register |

3. Block of 8 GPIO RW registers in the FPGA Block Design for tests

|                                                                                                                        |                                              |                                                                                        |                                                                                                                                      |                                                                                        | -                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Addr                                                                                                                   | Туре                                         | Name                                                                                   | Content                                                                                                                              | Bit                                                                                    | Comment                                                                                                                                                                                                                                                                                                      |

| $\begin{array}{c} 40000000\\ 40010000\\ 40020000\\ 40030000\\ 40040000\\ 40050000\\ 40060000\\ 40070000\\ \end{array}$ | RW<br>RW<br>RW<br>RW<br>RW<br>RW<br>RW<br>RW | gpio_0<br>gpio_0<br>gpio_0<br>gpio_0<br>gpio_0<br>gpio_0<br>gpio_0<br>gpio_0<br>gpio_0 | test register<br>test register<br>test register<br>test register<br>test register<br>test register<br>test register<br>test register | [31:0]<br>[31:0]<br>[31:0]<br>[31:0]<br>[31:0]<br>[31:0]<br>[31:0]<br>[31:0]<br>[31:0] | Base address to GPIO test register<br>Base address to GPIO test register |

| Addr                                                                                                                   | Туре                                         | Name                                                                                   | Content                                                                                                                              | <br>Bit                                                                                | Comment                                                                                                                                                                                                                                                                                                      |

| 40080000                                                                                                               | RW                                           | test5_1                                                                                | <br>XXXXXXXX                                                                                                                         | [31:0]                                                                                 | test RW register                                                                                                                                                                                                                                                                                             |

#### 4. Transmitter and Receiver MiniPOD Control registers

| Addr                 | Туре | Name                     | Content | Bit | Comment                                                                      |

|----------------------|------|--------------------------|---------|-----|------------------------------------------------------------------------------|

| 40800000<br>40810000 |      | trans_mpod<br>trans mpod |         |     | Base address to access Trans_MiniPOD<br>Base address to access Recvr MiniPOD |

These two registers are base addresses to access to the Transmitter and Receiver MiniPODs. The I2C master interfaces are implemented as XILINX IP in the AXI sybsystem. Each interface provides a set of 22 RW registers to generate I2C bus transactions.

| 5. Regist | ers fo | or the interfa | ce to the DCDC C | onverters |                                              |

|-----------|--------|----------------|------------------|-----------|----------------------------------------------|

| Addr      | Туре   | Name           | Content          | Bit       | Comment                                      |

| 40820000  |        | hub dcdc       |                  |           | Base address to access Hub's DCDC Converters |

This Master I2C bus makes connection to the Hub's DCDC Converter power supplies. The I2C master interface is implemented as XILINX IP in the AXI sybsystem. It provides a set of 22 RW registers to generate I2C bus transactions.

| 6. Regist | ers fo | or the interfa | ce to the Si Lab | 5338A |                                          |

|-----------|--------|----------------|------------------|-------|------------------------------------------|

| Addr      | Туре   | Name           | Content          | Bit   | Comment                                  |

| 40830000  |        | htm_silab      |                  |       | Base address to access HTM's SiLab 5338A |

This Master I2C bus makes connection to the HTM's SiLab 5338A. The I2C master interface is implemented as XILINX IP in the AXI sybsystem. It provides a set of 22 RW registers to generate I2C bus transactions.

#### $7.\ \mbox{Registers}$ for the interface to the switches

| Addr                             | Туре | Name                             | Content | Bit | Comment                                                                                                                                         |

|----------------------------------|------|----------------------------------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 40E00000<br>40E10000<br>40E20000 |      | switch_a<br>switch_b<br>switch_c |         |     | Base address to access Ethernet Switch Chip A<br>Base address to access Ethernet Switch Chip B<br>Base address to access Ethernet Switch Chip C |

These three registers are base addresses to access to the Ethernet Switch Chips. The MDIO interfaces are implemented as XILINX IP in the AXI system. Each interface provides a set of 4 RW registers to generate MDIO bus transactions.

#### 8. System Monitor registers

| Addr     | Туре | Name       | Content   | Bit | Comment                                    |

|----------|------|------------|-----------|-----|--------------------------------------------|

| 44A00000 |      | hub_sysmon | volt&temp |     | Base address to access FPGA System Monitor |

This is a base register to access the FPGA SysMon from IPbus.

Interface to the System Monitor can be implemented with AXI interface and read via IPbus, I2C interface of the System Monitor will be connected to the Slave I2C interface.

9. Test registers

| Addr         Type         Name         Content         Bit         Comment           00000012         RW         test2         xxxxxxx         [31:0]         test RW register           00001400         RW         test3         xxxxxxx         [31:0]         test RW register           00002002         RW         test4         xxxxxxx         [31:0]         test RW register           40080000         RW         test5_1         xxxxxxxx         [31:0]         test RW register           40801000         RW         test5_2         xxxxxxxx         [31:0]         test RW register           40811000         RW         test5_3         xxxxxxxx         [31:0]         test RW register           40831000         RW         test5_4         xxxxxxxx         [31:0]         test RW register           40831000         RW         test5_5         xxxxxxxx         [31:0]         test RW register           40E01000         RW         test5_6         xxxxxxxx         [31:0]         test RW register |                                  |                |                               |                                  |                            |                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------|-------------------------------|----------------------------------|----------------------------|----------------------------------------------------------|

| 00001400       RW       test3       xxxxxxxx       [31:0]       test RW register         00002002       RW       test4       xxxxxxxx       [31:0]       test RW register         40080000       RW       test5_1       xxxxxxxx       [31:0]       test RW register         40801000       RW       test5_2       xxxxxxxx       [31:0]       test RW register         40811000       RW       test5_3       xxxxxxxx       [31:0]       test RW register         40821000       RW       test5_4       xxxxxxxx       [31:0]       test RW register         40831000       RW       test5_5       xxxxxxxx       [31:0]       test RW register                                                                                                                                                                                                                                                                                                                                                                                 | Addr                             | Туре           | Name                          | Content                          | Bit                        | Comment                                                  |

| 40080000       RW       test5_1       xxxxxxx       [31:0]       test RW register         40801000       RW       test5_2       xxxxxxx       [31:0]       test RW register         40811000       RW       test5_3       xxxxxxx       [31:0]       test RW register         40821000       RW       test5_4       xxxxxxx       [31:0]       test RW register         40831000       RW       test5_5       xxxxxxx       [31:0]       test RW register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00001400                         | RW             | test3                         | XXXXXXXX                         | [31:0]                     | test RW register                                         |

| 40831000 RW test5_5 xxxxxxxx [31:0] test RW register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40801000                         | RW<br>RW       | test5_1<br>test5_2            | XXXXXXXX<br>XXXXXXXX             | [31:0]<br>[31:0]           | test RW register<br>test RW register                     |

| 40E11000         RW         test5_7         xxxxxxx         [31:0]         test RW register           40E21000         RW         test5_8         xxxxxxxx         [31:0]         test RW register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40831000<br>40E01000<br>40E11000 | RW<br>RW<br>RW | test5_5<br>test5_6<br>test5_7 | XXXXXXXX<br>XXXXXXXX<br>XXXXXXXX | [31:0]<br>[31:0]<br>[31:0] | test RW register<br>test RW register<br>test RW register |

| 44A01000 | RW | test5 9 | XXXXXXXX | [31:0] | test RI | W register |

|----------|----|---------|----------|--------|---------|------------|

|          |    |         |          |        |         |            |

| 10. Control/sta                                                          | tus registers     | for the interna | al FPGA | logic                              |

|--------------------------------------------------------------------------|-------------------|-----------------|---------|------------------------------------|

| Addr Type                                                                | Name              | Content         | Bit     | Comment                            |

| These registers<br>- HUB-ROD inter<br>- HUB-GBT/TTC i<br>- HUB-IPMC inte | face<br>.nterface | control/status  | inform  | ation for the internal FPGA logic: |

Table 1: The initial HUB FPGA register map.

# 3. TTC Clock recovery/GBT

The Hub in Slot 1 uses a 12-channel MiniPOD optical receiver to receive TTC signals from the upstream FELIX system. The Hub receives two types of TTC signals: a copy of the LHC clock and TTC control data.

# **3.1 Implementation**

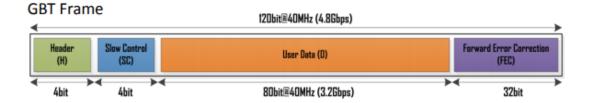

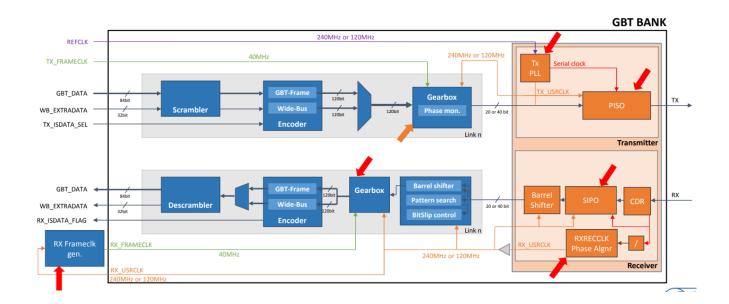

Trigger system require a fixed and deterministic latency in the transmission of the clock and data. In order to recover the LHC clock with the fixed latency, the HUB FW uses the GBT-FPGA component [8,9] which is being developed and supported by EP-ESE-BE section at CERN. The GBT-FPGA firmware supports the "Latency-fixed" implementation. In addition, the GBT-FPGA supports all three available encoding/decoding scheme: "GBT-Frame" (Reed-Solomon), "Wide-Bus" and "8b10b". The HUB FW uses a "GBT-Frame" scheme [Table 2]. The GBT FW is implemented with MGT transceiver and complexcontrol logic [Figure 9]. It is set to run at 4.8 Gbps (MGT REF CLK – 320.64 MHz, User/Internal Data Width – 40 bits, CPLL or QPLL).

Table 2. GBT-Frame (based on Reed-Solomon) structure.

Figure 9. The GBT-FPGA implementation method.

# **3.2 Latency Measurement**

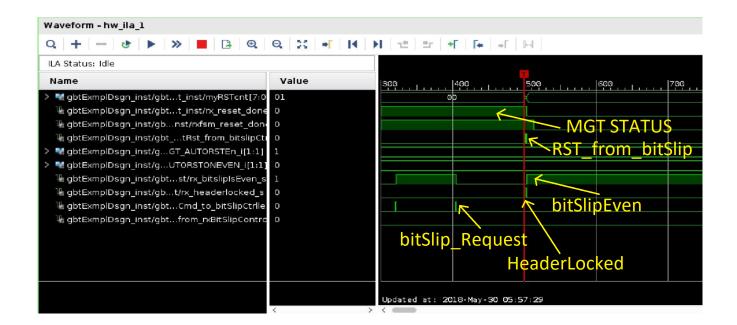

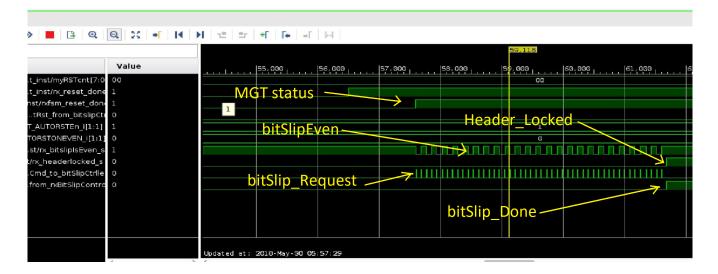

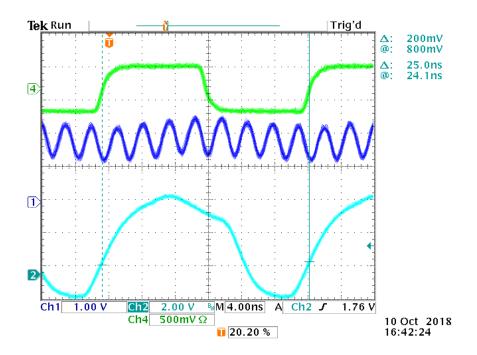

The Hub module successfully recovers the 40.08 MHz LHC [Figure 10] clock using the GBT-FPGA core in "latency-optimized" mode. The MGT eventually tracks the 4.8 Gbps serial data stream, no relevant phase noise due to rate conversion. The "Frame Aligner" status and "Bit Slip Control" status are monitored to ensure proper GBT functionality. The clock phase observed to be constant (to better than 100 ps) over a range of repeated tests.

# **GBT/MGT** status if the reset is hold:

| Q ≚ ≑ + =                                    |               |          |           |          |

|----------------------------------------------|---------------|----------|-----------|----------|

| Name                                         | Value         | Activity | Direction | V10      |

| 🍉 gbtRxReady_from_gbtExmplDsgn               | •             |          | Input     | hw_vio_2 |

| > 🍓 countBitsModified[31:0]                  | [H] 0000_0000 |          | Input     | hw_vio_2 |

| > 🍓 countWordReceived[31:0]                  | [H] 0000_0000 |          | Input     | hw_vio_2 |

| > 🐚 DEBUG_CLK_ALIGNMENT_debug[2:0]           | [H] O 👻       |          | Output    | hw_vio_2 |

| 🐚 txFrameClkPllLocked_from_gbtExmplDsgn      | •             |          | Input     | hw_vio_2 |

| 🍉 rxisData_from_gbtExmplDsgn                 | •             |          | Input     | hw_vio_2 |

| 🍗 txAlignComputed_from_gbtbank               | •             |          | Input     | hw_vio_2 |

| 🍗 txAligned_from_gbtbank_latched             | •             |          | Input     | hw_vio_2 |

| 🍉 rxDataErrorSeen_from_gbtExmplDsgn          | •             |          | Input     | hw_vio_2 |

| 🍗 rxExtrDataWidebusErSeen_from_gbtExmplDsgn  | •             |          | Input     | hw_vio_2 |

| 🖕 rxFrameClkReady_from_gbtExmplDsgn          | •             |          | Input     | hw_vio_2 |

| 🍗 gbtRxReadyLostFlag_from_gbtExmplDsgn       | [B] O         |          | Input     | hw_vio_2 |

| 🍗 latOptGbtBankRx_from_gbtExmplDsgn          | [B] 1         |          | Input     | hw_vio_2 |

| 🍗 latOptGbtBankTx_from_gbtExmplDsgn          | [B] 1         |          | Input     | hw_vio_2 |

| 🖕 mgtReady_from_gbtExmplDsgn                 | •             |          | Input     | hw_vio_2 |

| 🐱 probe_in4                                  | [B] O         |          | Input     | hw_vio_2 |

| > 🍓 probe_in5[5:0]                           | [H] 00        |          | Input     | hw_vio_2 |

| > 🍓 rxBitSlipRstCount_from_gbtExmplDsgn[7:0] | [H] 00        |          | Input     | hw_vio_2 |

| 🎍 probe_inl1                                 | [B] O         |          | Input     | hw_vio_2 |

# **GBT/MGT** status if the reset is released:

| Name              |                                 | Value              | Activity | Direction | VIO      |

|-------------------|---------------------------------|--------------------|----------|-----------|----------|

| 🍗 gbtRxReady      | _from_gbtExmplDsgn              | •                  |          | Input     | hw_vio_2 |

| > 🍓 countBitsMa   | dified[31:0]                    | [H] 0000_0000      |          | Input     | hw_vio_2 |

| > 🍓 countWordF    | leceived[31:0]                  | [H] 0A08_173B      | 1        | Input     | hw_vio_2 |

| > 🍓 DEBUG_CLK     | ALIGNMENT_debug[2:0]            | [H] 0 👻            |          | Output    | hw_vio_2 |

| 🍗 txFrameClkF     | llLocked_from_gbtExmplDsgn      | ۲                  |          | Input     | hw_vio_2 |

| 🍗 nxisData_fro    | m_gbtExmplDsgn                  | ۲                  |          | Input     | hw_vio_2 |

| 🍗 txAlignComp     | outed_from_gbtbank              | ۲                  |          | Input     | hw_vio_2 |

| 🍗 txAligned_fr    | om_gbtbank_latched              | •                  |          | Input     | hw_vio_2 |

| 🍗 n/DataError     | Seen_from_gbtExmplDsgn          | •                  |          | Input     | hw_vio_2 |

| 🍗 nxExtrDataW     | /idebusErSeen_from_gbtExmplDsgn | ۲                  |          | Input     | hw_vio_2 |

| 🍗 nxFrameClkF     | leady_from_gbtExmplDsgn         | •                  |          | Input     | hw_vio_2 |

| 🍗 gbtRxReady      | LostFlag_from_gbtExmplDsgn      | [B] O              |          | Input     | hw_vio_2 |

| 🍗 latOptGbtBa     | nkRx_from_gbtExmplDsgn          | [8] 1              |          | Input     | hw_vio_2 |

| 🍗 latOptGbtBa     | nkTx_from_gbtExmplDsgn          | [B] 1              |          | Input     | hw_vio_2 |

| 🍗 mgtReady_f      | rom_gbtExmplDsgn                | •                  |          | Input     | hw_vio_2 |

| 🍗 probe_in4       |                                 | [B] O              |          | Input     | hw_vio_2 |

| > 🍗 probe_in5[5   | :0]                             | [H] 00             |          | Input     | hw_vio_2 |

| > 🍓 rxBitSlipRst( | Count_from_gbtExmplDsgn[7:0]    | [H] 00             |          | Input     | hw_vio_2 |

| 🍗 probe_inl1      |                                 | [B] O              |          | Input     | hw_vio_2 |

| 🛥 manualRese      | etRx_from_user                  | [B] 0 <del>*</del> |          | Output    | hw_vio_2 |

| 🛥 clkMuxSel_fr    | om_user                         | [B] 0 👻            |          | Output    | hw_vio_2 |

| > 🍓 loopBack_fr   | om_user[2:0]                    | [H] O 👻            |          | Output    | hw_vio_2 |

### **GBT** startup, part 1:

The MGT status OK. Th bitSlipEven, \*must\* be \*odd\*. But, in this case is \*even\*, that's why the MGT RST is issued. The GBT startup procedure will be repeated.

**GBT startup, part 2:**

The MGT status OK. The bitSlipEven, must be \*odd\*. Yes, in this case is \*odd\*. The GBT startup is completed.

# The 40.08 MHz LHC recovered clock (light blue)

- · Manual intervention, force GBT realignment

- Reset receiver MGT on Hub

- Power cycle Hub

- Reconfigure Hub FPGA

- Unplug/reinsert TTC fiber @ TTCfx/VC109

- Reconfigure TTCfx/VC709

- Re-initialize the TTCfx/VC709

- Reset of the TTCfx/VC709

Figure 10. The Hub module successfully recovers the 40.08 MHz LHC.

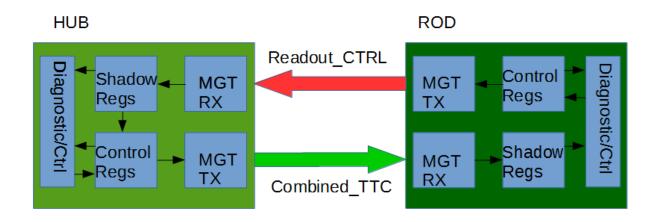

### 4.0 Readout Control (Readout\_Ctrl)

The HUB module is obliged to receive the Readout Control (Readout\_CTRL) information from the ROD via serial link named Readout\_CTRL [2]. The HUB module is the only one module within the shelf which gets the Readout Control data from the ROD. That information is used by the Hub, also

fanned out to the rest of the system. The main purpose is to provide resets to all of the data links (Aurora) between the Fex's and the ROD plus HUB module.

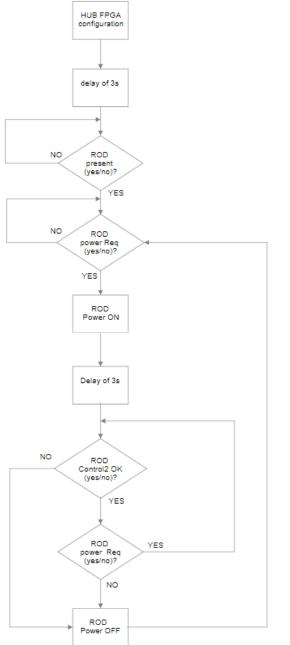

# 4.1 ROD Power Up scheme

When the HUB FPGA is configured, ROD is power-up automatically. This procedure is implemented with the use of the state machine. Once the HUB FPGA is configured, the logic is obliged to check if the ROD is present. In order to do so, the ROD\_PRESENT\_B\_TO\_FPGA signal is check. This signal is a pull-down resistor on the ROD when ROD is not present this signal goes 'HI' on the HUB. In addition, the IPbus register (ROD\_Power\_Req) provides the information if there is a request to power-up the ROD. If the ROD power Req goes 'HI', the ROD is powered-up. This is done with the use of two signals: ROD\_Power\_Enable and ROD\_Power\_Enable\_B. These two signals are output from the HUB FPGA that through some hardwired logic on the HUB inform the ROD when it may turn ON its power supplies. After the delay of 3 seconds, the logic starts to monitor the ROD\_Power\_Control\_2\_FPGA signal. When 'HI', this signal indicates that all power supplies on the ROD are operating correctly. If there are no problems with the power supplies, the logic checks if the ROD Power Req is 'HI'. If so, the ROD Power Control 2 FPGA signal is also checked. In cases

where, there is a problem with the power supplies or there is a request to power-down the ROD, the ROD is powered-down and the engine returns to its initial state.

The ROD\_Power\_Req signal is treated as an extra signal for the test purposes and it might be removed from the power up engine in the production firmware.

In addition, there are two signals that are not being used by the power up engine: ROD\_Power\_Control\_3\_FPGA, this is an input to the HUB's FPGA. When 'HI' this signal indicates that the ROD is configured and fully ready for normal L1Calo operation. The FPGA\_RODs\_SMBALERT\_B, this is an input to the HUB's FPGA that when 'LOW' indicates a power supply problem on the ROD. During normal operation this signal should be 'HI'.

- 1. Signals that are being used by the power up engine

- 1.a ROD\_PRESENT\_B\_TO\_FPGA

This signal is a pull-down resistor on the ROD. When the ROD is NOT present this signal goes HI on the Hub.

- 1.b ROD\_Power\_Control\_2\_FPGA

- This is an input to the Hub's FPGA. When HI this signal indicates that all power supplies on the ROD are operating correctly.

- ROD\_Power\_Enable ROD\_Power\_Enable\_B

These two signal are outputs from the Hub FPGA that through some hardwired logic on the Hub tell the ROD when it may turn ON its power supplies.

- 1.c ROD power request is controlled by the IPbus register

- 2. Signals that are not being used by the power up engine

- 2.a ROD\_Power\_Control\_3\_FPGA

- This is an input to the Hub's FPGA. When HI this signal indicates that the ROD is Configured and fully ready for normal L1Calo operation.

- 2.b FPGA\_RODs\_SMBALERT\_B

This is an input to the Hub's FPGA that when LOW indicates a power supply problem on the ROD. During normal operation this signal should always be HI.

Figure 11. The ROD power up scheme

# 4.2 Control Bit definition

The bits within the Readout Control words are primarily defined to provide initialization functions for all of the FEX data links.

# **Comma Character**

Bits 7 to 0 of Word\_0 contain the Comma character that maintains alignment of the 4 shadow registers with their corresponding Control registers. The chosen character is K28.5 = 0xBC.

# Version

The 4-bit value contains the version number of this overall bit assignment. It will be held at "0000" through the initial debug phases, where many changes may occur.

# ROD\_XOFF

When active, this signal indicates that the ROD cannot currently accept further data from Fex sources. This signal is fanned-out to the shelf FEX's by the Hub via the Combined\_TTC link. This control halts data from ALL FEX's as a group. There is no mechanism for halting individual FEX's. This bit remains active for the duration of the time that data should be paused.

# Global\_Link\_Reset

This single bit is used to reset <u>ALL</u> of the data (Aurora) links within the shelf. The primary use is in the first initialisation after power-up. The ROD can hold this reset active for an indefinite amount of time. On the trailing edge (deactivation), the eFex's should provide additional timing control for the GTReset and Reset signals on the Aurora interface. This signal is fanned-out to the shelf FEX's by the Hub via the Combined\_TTC link.

# Slot\_N\_link\_reset\_M

These signals allow the ROD to reset <u>individual</u> links providing data to it. It is asserted when the ROD is attempting to bring up a link which has gone down for some reason.

The appropriate bits (as defined by logical slot) are placed into the Combined\_TTC link to each node by the Hub. Within the Combined\_TTC link, they are referred to as Link\_Reset[3:0].

The node module (FEX) should use the signal to reset its Aurora interface plus any additional logic required to resume normal data transmission.

The active time of these bits is indeterminate, and may be only a few broadcast cycles. On the trailing edge (deactivation), the nodes should provide additional timing control for the GTReset and Reset signals on the Aurora interface.

The jFEX modules will electrically connect to logical slots 04, 05, 08, 09, 12, and 13. Each jFEX module has four independent Aurora data links which can be controlled separately. Four independent Link Resets are therefore provided for these logical slots.

In slots where multiple resets are provided, eFEX modules, having only one Aurora interface, should use only the M=0 reset bits.

# Slot N Channel Up M

These bits report on whether each slot's Aurora Channel is 'UP' or 'Down'. The information is rebroadcast to each FEX slot in the so that the Aurora transmitter knows if the receiver side of the channel (the ROD) is up. If a channel goes down, the ROD shall attempt to reset both Rx and Tx ends of the link.

Slots 3-8 have four channel up status bits each. This is to cover the case of jFex where each of four processors has its own data link to the ROD. It is expected that eFex boards in these slots will only use the M=0 Channel Up bit.

# **Slot N Link Enable**

The ROD may disable the links from some boards within the shelf. This would happen in the case where a link reset had been applied, however the link still does not come up. It can also be used during commissioning to eliminate processing of selected slots. Note that in the case of jFEX, all four aurora links should be disabled if the slot enable is not present (='1').

# **Shelf Number**

These bits are currently reserved. There is a possibility to derive the Shelf Number from a rotary switch on the ROD. Use of this option is still TBD.

# CRC (9-bit)

CRC is included to provide additional robustness on this link. Erroneous resets could cause loss of data. Choice of polynomial is from <u>https://users.ece.cmu.edu/~koopman/crc/index.html</u>

The chosen polynomial is 0x17d in Koopman format of 0x2fb in explicit+1 format.

The CRC is calculated over all four words of each transmission. When a CRC error occurs, all four of the associated words must therefore be ignored.

All bits within the four-word broadcast will be held active for at least two four-word broadcast periods in order to reduce the probability of missing an active signal due to CRC error.

| veau0  | ut_CTRL register bit d  |        | <u> </u>               |        |                       |        |                    |

|--------|-------------------------|--------|------------------------|--------|-----------------------|--------|--------------------|

| word 0 |                         | word 1 |                        | word 2 |                       | word 3 |                    |

| bit    | 0XBC = K28.5            | bit    |                        | bit    |                       | bit    |                    |

| 0      | 0                       | 0      | slot 3 link reset      | 0      | slot3 channel up      | 0      | slot 3 Link Enable |

| 1      | 0                       | 1      | slot 4 link reset (0)  | 1      | slot4 channel up(0)   | 1      | slot 4 Link Enable |

| 2      | 1                       | 2      | slot 5 link reset (0)  | 2      | slot5 channel up(0)   | 2      | slot 5 Link Enable |

| 3      | 1                       | 3      | slot 6 link reset      | 3      | slot6 channel up      | 3      | slot 6 Link Enable |

| 4      | 1                       | 4      | slot 7 link reset      | 4      | slot7 channel up      | 4      | slot 7 Link Enable |

| 5      | 1                       | 5      | slot 8 link reset (0)  | 5      | slot8 channel up(0)   | 5      | slot 8 Link Enable |

| 6      | 0                       | 6      | slot 9 link reset (0)  | 6      | slot9 channel up(0)   | 6      | slot 9 Link Enable |

| 7      | 1                       | 7      | slot 10 link reset     | 7      | slot10 channel up     | 7      | slot 10 Link Enabl |

| •      | _                       |        |                        |        |                       |        |                    |

| 8      | version 0               | 8      | slot 11 link reset     | 8      | slot11 channel up     | 8      | slot 11 Link Enabl |

| 9      | version 1               | 9      | slot 12 link reset (0) | 9      | slot12 channel up(0)  | 9      | slot 12 Link Enabl |

| 10     | version 2               | 10     | slot 13 link reset (0) | 10     | slot13 channel up(0)  | 10     | slot 13 Link Enabl |

| 11     | version 3               | 11     | slot 14 link reset     | 11     | slot14 channel up     | 11     | slot 14 Link Enabl |

| 12     | 0                       | 12     | 0                      | 12     | 0                     | 12     | 0                  |

| 13     | 0                       | 13     | slot 4 link reset (1)  | 13     | slot4 channel up (1)  | 13     | 0                  |

| 14     | ROD_XOFF (to all slots) | 14     | slot 4 link reset (2)  | 14     | slot4 channel up (2)  | 14     | 0                  |

| 15     | Global_Link_Reset       | 15     | slot 4 link reset (3)  | 15     | slot4 channel up (3)  | 15     | 0                  |

|        |                         |        |                        |        |                       |        |                    |

| 16     | 0                       | 16     | slot 5 link reset (1)  | 16     | slot5 channel up (1)  | 16     | 0                  |

| 17     | 0                       | 17     | slot 5 link reset (2)  | 17     | slot5 channel up (2)  | 17     | 0                  |

| 18     | 0                       | 18     | slot 5 link reset (3)  | 18     | slot5 channel up (3)  | 18     | 0                  |

| 19     | 0                       | 19     | slot 8 link reset (1)  | 19     | slot8 channel up (1)  | 19     | shelf(0)           |

| 20     | 0                       | 20     | slot 8 link reset (2)  | 20     | slot8 channel up (2)  | 20     | shelf(1)           |

| 21     | 0                       | 21     | slot 8 link reset (3)  | 21     | slot8 channel up (3)  | 21     | shelf (2)          |

| 22     | 0                       | 22     | slot 9 link reset (1)  | 22     | slot9 channel up (1)  | 22     | shelf(3)           |

| 23     | 0                       | 23     | slot 9 link reset (2)  | 23     | slot9 channel up (2)  | 23     | CRC (9-bit)        |

| 24     | 0                       | 24     | slot 9 link reset (3)  | 24     | slot9 channel up (3)  | 24     | CRC (9-bit)        |

| 25     | 0                       | 25     | slot 12 link reset (1) | 25     | slot12 channel up (1) | 25     | CRC (9-bit)        |

| 26     | 0                       | 26     | slot 12 link reset (2) | 26     | slot12 channel up (2) | 26     | CRC (9-bit)        |

| 27     | 0                       | 27     | slot 12 link reset (3) | 27     | slot12 channel up (3) | 27     | CRC (9-bit)        |

| 28     | 0                       | 28     | slot 13 link reset (1) | 28     | slot13 channel up (1) | 28     | CRC (9-bit)        |

| 29     | 0                       | 29     | slot 13 link reset (2) | 29     | slot13 channel up (2) | 29     | CRC (9-bit)        |

| 30     | 0                       | 30     | slot 13 link reset (3) | 30     | slot13 channel up (3) | 30     | CRC (9-bit)        |

| 31     | 0                       | 31     | 0                      | 31     | 0                     | 31     | CRC (9-bit)        |

# 4.3 Readout Control/Implementation

Table 3: Readout\_Ctrl bit assignments.

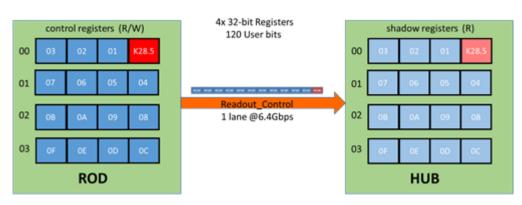

The Readout\_Ctrl link on the HUB module is implemented with the use of MGT Transceiver GTH, control and diagnostic logic. The Readout\_Ctrl link is designed to operate at 6.4 Gbps. When 8b/10b overhead is accounted for, the effective rate is reduced to  $6.4 \ge 0.8 = 5.12$  Gbps. In order to to control message transmission within a single LHC clock period, the lengh of the message is limited tp 128 bts. The HUB Readout Control FW features one receiver (RX). In order to debug the design, the standard Xilinx diagnostic components are being used to monitor the data flow (as for example like the ILA and VIO). The physical layer is configured with the use of GT wizard.

The physical implementation of the Readout\_CTRL links assumes that there are Control Registers on the Tx ROD side, and Shadow Registers on the Rx HUB side. The transmitter side generates the 128 bit message from 4 Control registers: Word\_0, Word\_1, Word\_2, and Word\_3. The transmitter side logic is in charge to write control information into these registers for transmission to the modules within the shelf. These registers are continuously transmitted to the HUB which receives the data into a duplicate set of 4 registers referred to as Shadow Registers. Anything written into a Control Register at the transmitter side will appear in the corresponding Shadow register at the receiving side within the following LHC clock. The least significant byte of Word\_0 is reserved for the 8b10b Comma character K28.5.

# (1/(6.4 Gbps \*0.8)) \* 128 bits = 2.5 ns = 1/40 MHz

Figure 12. Control and Shadow Register

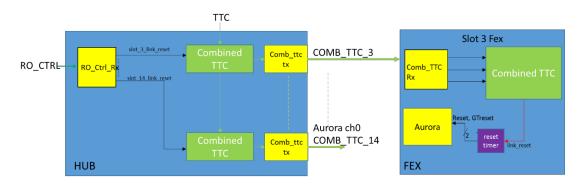

# 5. Combined\_TTC/DATA

The HUB FW is obliged to distribute TTC information throughout the shelf [2]. There are several Combined\_TTC links within the shelf, one between each Fex slot (slots 3-14) and each Hub, also one between each Hub and ROD and 2 links between two HUBs.

The additional feature allow to transmit the Reset signal (Aurora Initialization, Figure 12) from the Readout\_Ctrl link and distribute it to the appropriate shelf slot. In total, we have the following number of links:

- 12 links between each FEX slot and each HUB

- 1 link between the ROD and each HUB

- 2 links between two HUBs

Figure 13. Example of link Reset Routing.

# 5.1 Combined\_TTC/Implementation

The Combined\_TTC/Data link on the HUB FPGA is implemented with the use of several components, including the MGT transceivers (GTH and GTY), control and the diagnostic logic. The Combined\_TTC/DATA link is designed to operate at 6.4 Gbps. The physical implementation of the Combined\_TTC/DATA links assumes that there are 4 Control Registers on the Hub TX side, and Shadow Registers on the Rx side (Receiver: FEX, ROD and other HUB). The transmitter side generates the 128 bit message from 4 Control registers: Word\_0, Word\_1, Word\_2, and Word\_3. The transmitter side logic is in charge to write control information into these Control Registers. The contents of these registers are continuously transmitted to the modules (within the shelf) which receives the data into a duplicate set of 4 registers referred to as shadow registers. Anything written into a Control Register at the transmitter side will appear in the corresponding Shadow register at the receiving side within the

following LHC clock. The least significant byte of Word\_0 is reserved for the 8b10b Comma character K28.5.

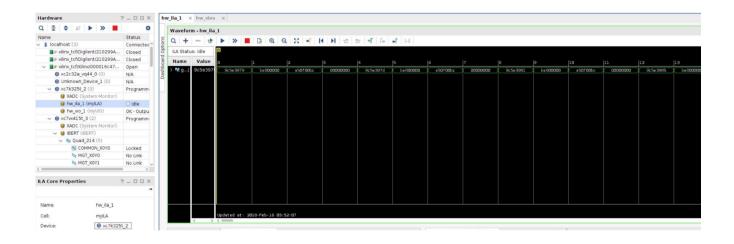

The Combined\_TTC/DATA FW development comprises several stages. In terms of Combined\_TTC/DATA link, the first stage assumes to transmit the Combined\_TTC/Data stream to the ROD module, also to the FEX slot 3 (see Figure 14 and 15). In order to debug the design, the standard Xilinx diagnostic components are being used to monitor the data flow (as for example like the ILA and VIO). The physical layer is configured with the use of GT wizard.

For the purpose of the initial test, the HUB transmitter side generates the 128 bits from 4 Control registers but only some static patterns are written into these registers. In the next step, the Readout\_Ctrl data received on the HUB from ROD module are retransmitted as the Combined\_TTC/Data stream to the ROD and FTM module in slot 3. Once the communication between the HUB and other modules within shelf is established, a test pattern generator will be replaced by real GBT/TTC component. Next development steps assumes to add (gradually) the remaining receivers in the shelf.

Figure 14. The HUB and ROD setup to test the Readout\_Ctrl and Combined\_TTC/Data link.

| ardware ?                                                               |            | lashboard_1   | 1 × hw       | _ila_1 | k hw_i      | la_2 × | hw_i  | ila_3 > | das     | hboard     | 2 × 1 | w_ila_ | 4 × 1    | w_ila_ | 5 X    | hw_ila_ | 6 X I   | hw_ila_7 | ×h    | w_ila_8 | ×h    | w_ila_9 | ×h     | w_ila_10 | × h   | w_ila_11 | × hw_    | ila_12 × |

|-------------------------------------------------------------------------|------------|---------------|--------------|--------|-------------|--------|-------|---------|---------|------------|-------|--------|----------|--------|--------|---------|---------|----------|-------|---------|-------|---------|--------|----------|-------|----------|----------|----------|

| 2 풒 ♦ 🖉 🕨 ≫ 📕                                                           | 0          | Waveform      | n - hw_ila_i | 8      |             |        |       |         |         |            |       |        |          |        |        |         |         |          |       |         |       |         |        |          |       |          |          |          |

| ame<br>ame nw_vio_4 (nuo_gun_co                                         | Status     | Q +           | - 3          | ► ×    |             | D (    | a a   | 8       | -       | <b>н</b> н | 12 2  | - H    | Te la    | •F   H |        |         |         |          |       |         |       |         |        |          |       |          |          |          |

| hw_vio_5 (hub_gth_co                                                    | OK - Outpu | ILA Statu     | s Idle       | 0      |             |        |       |         |         |            |       |        |          |        |        |         |         |          |       |         |       |         |        |          | _     |          |          |          |

| 1 hw_vio_6 (hub_gty_co                                                  | OK - Outpu |               |              |        |             |        |       |         |         |            |       |        |          |        |        |         |         |          |       |         |       |         |        |          |       |          |          |          |

| hw_vio_7 (hub_gty_co                                                    | OK - Outpu | Name          | Value        | 0      |             | 5      |       | 10      |         | 15         |       | 20     |          | 25     |        | 30      |         | 35       |       | 40      |       | 45      |        | 50       |       | 55       | 60       |          |

| hw_vio_8 (hub_gty_co                                                    | OK - Outpu |               | 0000000      |        | XOXO        |        | XX    |         | XX      |            |       |        | XXX      |        |        |         |         |          |       |         |       |         |        |          |       |          | XOX      |          |

| M hw_ila_3 (myiLA_ReadC                                                 | O Idle     | > ₩ b]        | 0            | 0      | <u>)</u> 2) | 0 2    | X O   | 2       | 0       | 2          | 3)2   | 0      | 2        | 0)     | 2 0    | 2       | 0       | 2        | 3)2   | 0       | 2     | 0 X     | 2 0    | X2X      | 0     | 2 0      | 2        | 0)2/     |

| <ul> <li> <ul> <li>xc7vx550t_1 (18)             </li> </ul> </li> </ul> | Programm   | > ₩ b         | 2            | 2 0    | 2           | 0      | 2     | 0 2     | ) 0     | 2          | 0     | 2) 0   | 2        | 0      | 2      | 0 X     | 2) 0    | 2)       | 0     | 2 0     | 2     | 0       | 2      | 0 2      | X O   | 2        | 2)       | 0 2      |

| MADC (System Monitor)                                                   |            |               | a50f00bc     |        |             |        |       |         |         |            |       |        |          |        |        |         |         |          |       |         |       |         | a50f   | 60bc     |       |          |          |          |

| 1 hw_axi_1 (AXI)                                                        |            | > 🖬 b]        | 0000000      | $\sim$ |             |        |       |         |         |            |       |        |          |        |        |         |         |          |       |         |       |         | CGCG   | ccco     |       |          |          |          |

| M hw ila_4 (ILA_axi_ch0)                                                | Oldle      | > № b]        | 076196c      | 0      | 076196d     | 076    | 196d5 | 076196  | id9 🔾 🕻 | 76196dd    | 0761  | 96e1   | 076196e  | 5 07   | 6196e9 | 07619   | 6ed 🔾 🕻 | 376196f1 | 0761  | 96f5 🔨  |       | 9 07    | 6196fd | 076197   | 01 07 | 619705   | 07619709 | 07619    |

| M hw ila 5 (ILA axi ch2)                                                | O Idle     | > ₩b          | 1            | 1/2/3  | 01          | 2 3 0  | 12    | 3 0 1   | 2/3     | 01         | 2 3 0 | 1/2/3  |          | 2 3    | 3/1/2  | 30      | 1/2/3   | 0(1)     | 2)3)0 | 12      | 3 0 1 | 23      | 0 1 2  | 301      | 23    | 0 1 2 5  |          | 2/3/0/1  |

| 1 hw vio 9 (aurora mon)                                                 | OK - Outpu | \ <b>∯ ba</b> | 1            |        |             |        |       |         |         |            |       |        |          |        |        |         |         |          |       |         |       |         |        |          |       |          |          |          |

| bw ila_6 (backplane/a                                                   | Oldle      | ₩ ba          | 1            |        |             |        |       |         |         |            |       |        |          |        |        |         |         |          |       |         |       |         |        |          |       |          |          |          |

| # hw vio 10 (backplane/                                                 | OK - Outpu | ₩ b           | 1            |        |             |        |       |         |         |            |       |        |          |        |        |         |         |          |       |         |       |         |        |          |       |          |          |          |

| 9 hw ila 7 (backplane/a                                                 | Oldle      | > 🖬 b         | Of00bcbe     |        | XXX         | XX     | XX    |         | XX      |            |       |        | $\infty$ |        |        |         | XX      |          |       |         |       |         |        |          |       |          |          |          |

| W hw vio_11 (backplane/                                                 | OK - Outpu | > ₩ b]        | be80000      |        |             |        |       |         |         |            |       |        |          |        |        |         |         |          |       |         |       |         | be80   | 0000     |       |          |          |          |

| W hw ila 8 (backplane/c                                                 | O Idle     |               |              |        |             |        |       |         |         |            |       |        |          |        |        |         |         |          |       |         |       |         |        |          |       |          |          |          |

| W hw vio 12 (backplane/                                                 | OK         |               |              |        |             |        |       |         |         |            |       |        |          |        |        |         |         |          |       |         |       |         |        |          |       |          |          |          |

|                                                                         | >          |               |              |        |             |        |       |         |         |            |       |        |          |        |        |         |         |          |       |         |       |         |        |          |       |          |          |          |

|                                                                         |            |               |              |        |             |        |       |         |         |            |       |        |          |        |        |         |         |          |       |         |       |         |        |          |       |          |          |          |

| Core Properties ?                                                       | ×          |               |              |        |             |        |       |         |         |            |       |        |          |        |        |         |         |          |       |         |       |         |        |          |       |          |          |          |

|                                                                         | 33         |               |              |        |             |        |       |         |         |            |       |        |          |        |        |         |         |          |       |         |       |         |        |          |       |          |          |          |

|                                                                         |            |               |              |        |             |        |       |         |         |            |       |        |          |        |        |         |         |          |       |         |       |         |        |          |       |          |          |          |

| ame: hw ila 8                                                           |            |               |              |        |             |        |       |         |         |            |       |        |          |        |        |         |         |          |       |         |       |         |        |          |       |          |          |          |

Figure 15. The Combined\_TTC Data link test: A correct Combined\_TTC stream on the ROD (upper plot) and on the FTM module in slot 3 (lower plot).

| word 0 |                        | word 1 |          | word 2 |                 | word 3 |                  |

|--------|------------------------|--------|----------|--------|-----------------|--------|------------------|

| bit    | 0XBC = K28.5           | bit    |          | bit    |                 | bit    |                  |