# The Pre-Processor Module (PPM)

# for the ATLAS Level-1 Calorimeter Trigger

Version 1.1

Okt.2009

The ATLAS group at the KIP Heidelberg

Contact: P. Hanke (hanke@kip.uni-heidelberg.de)

#### Abstract

The Pre-Processor of the ATLAS Level-1 Calorimeter Trigger prepares pipe-lined digital data as input to subsequent processors, which identify objects for the decision making on Level-1. The Pre-Processor system receives appr. 7200 analog signals from the entire calorimetry of the ATLAS experiment. The calorimetric detectors are divided into an electro-magnetic and a hadronic part along depth. Lateral division for the purpose of triggering gives cells of size 0.1 \* 0.1 along azimuth and pseudo-rapidity. The signals represent deposits of 'transverse energy' in the electro-magnetic and the hadronic part respectively.

The Pre-Processor has to attribute digital values of transverse energy to the 'bunch-crossing', in which the proton-proton collision took place. The values are transmitted in 'real-time' as serial data-streams to the object-defining processors to obtain a trigger-decision without introduction of 'dead-time'. Furthermore, trigger data are made available for readout, since the signals of trigger cells are not accessible otherwise. Control and monitoring of the trigger performance is a major task in the experiment.

This document describes the most important entity of the Pre-Processor electronics - the Pre-Processor Module. The system comprises a large number (appr.128) of such identical modules covering the trigger space spanned by the ATLAS calorimeters.

## 1. Introduction

#### 1.1 Overview.

The Pre-Processor Module (PPM) is the essential building block forming the Pre-Processor system. It receives analog signals from the ATLAS calorimeters on front-panel connectors. The differential signals are converted to uni-polar form and transmitted further for digitisation. In parallel, a discriminator checks the crossing of a threshold to determine a time-reference. This reference can be used later to relate an 'accepted event' to the 'bunch-crossing' in the LHC storage ring. 'Bunch crossings' occur repetitively at a rate of 40.08 MHz.

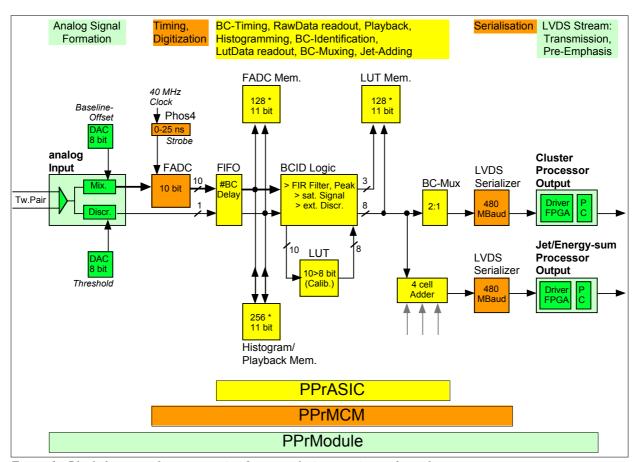

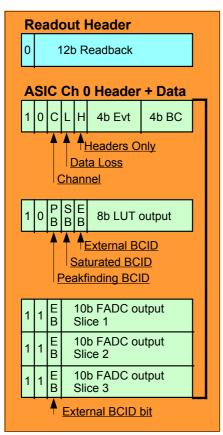

The actual signal processing is located on a Multi-Chip-Module (PPrMCM). Digitisation in a 'Flash Analog-to-Digital Converter' (FADC) to 10 bits with a sampling frequency of 40.08 MHz is the first step. Fine adjustment of the digitisation strobe to the peak of the analog signal is achieved with a chip, that allows a delay-setting in steps of 1 nsec across the 25 nsec LHC clock period. The following processing, which is very specific to the experiment, takes place in a self-designed 'Application Specific Integrated Circuit' (PPrASIC). Three data streams emanate as parallel bit-patterns from the PPrASIC:

- 1. Two streams represent energy deposits on a 0.1\*0.1 space-grid defined in units of azimuthal angle and pseudo-rapidity. These values of energy-deposit are transmitted to the 'Cluster Processor' (CP) to identfy 'small' objects like 'photons', 'isolated electrons', 'tau-leptons' and others.

- 2. One other stream represents energy deposits on a 0.2\*0.2 space-grid. Those data are transmitted to the 'Jet/Energy-Sum Processor' (JEP), where 'larger' objects like 'particle jets' are identified. In addition, energy sum-values are built to be used as e.g. 'missing transverse energy' signature.

Transmission of the data as parallel streams to the separate crate-systems (CP, JEP) is technically almost impossible due to the bulk-cabling involved. Hence, serialisation to high-frequency is implemented on the PPrMCM to maintain pipe-lined transfer in 'real-time'. These high-frequency data are transported on the PPM to the backplane periphery, where the cable connections are located.

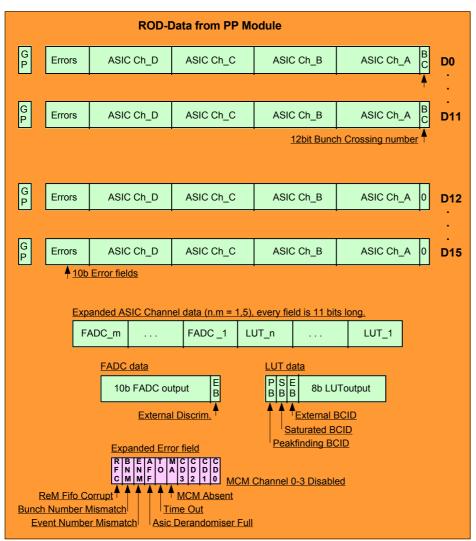

The analog calorimeter trigger input signals are not accessible to the 'Data AQcuisition system' (DAQ) of the experiment. Hence, readout of the digitised values at the Pre-Processor is a mandatory task. Pipe-line memories store values at two points in the pre-processing chain. A dedicated system was developed to retrieve data to DAQ upon positive Level-1 decisions ('L1-Accept'). The system is implemented in a 'Field Programmable Gate Array', called 'Readout Merger FPGA'. It collects the relevant data from the distributed locations on the PPM, formats and provides parallel output to the backplane. An auxiliary module on the same slot, located in the rear of the crate, serialises the data stream for high-speed transmission to a ReadOut Driver (ROD). The method provides enough band-width to transport the data to the ATLAS DAQ system.

The Pre-Processor Module requires also a 'standard' interface to computer infrastructure for setting-up, debugging and control. For this purpose, the module is configured as a 'standard VME slave'. The entire address space of the module is accessible through VME.

## 1.2 Scope.

This document describes the implementation of the Pre-Processor Module. The modules built provide the full functionality as required for ATLAS.

The structure of the document is as follows:

- Section 2 outlines the functional blocks of the module as intended at the time of specification.

- Section 3 describes the corresponding implementation on the level of the 'Printed Circuit

- Board' (PCB) hardware.

- The 'software' view of the module, as seen from the VME and/or the DAQ(ROD)-side, is given in Section 4, where the content of the data space is defined.

- Technical details concerning the design process, the manufacturing and the testing of the modules are described in Section 5 followed by summary in Section 6.

- Tabular information, like connector pinnings, is given in the Appendices.

## 1.3 Related projects.

It should be noted, that the system described here, is embedded in a collaborative effort, which ranges from the calorimetry input across the Pre-Processor to the Level-1 object-finding Processors (CP and JEP) and finally to the decision-making 'Central Trigger Processor' (CTP) in the 'ATLAS Calorimeter Level-1 Trigger System'. The Pre-Processor module itself carries sub-components, where electronic functionality is integrated to a very high degree. Due to their complexity, these components (the PPrMCM and the PPrASIC) were specified and reviewed separately. Hence, their detailed description is given in separate documentation. However, only because of the high degree of integration, a system configuration could be achieved, which constitutes a viable solution in terms of size, reliability and modularity.

Related overview documentation comprises:

- The Technical Design Report on the First Level Trigger (TDR) [Ref. 1].

- The Timing, Trigger and Control system for ATLAS (TTC) [Ref. 2].

## 2. The functional blocks on the Pre-Processor Module.

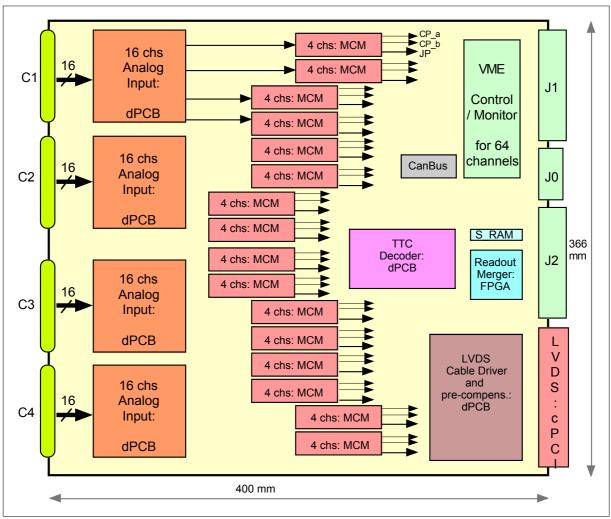

The functional requirements and their allocation to building blocks on the PPM is outlined in this section. The realisation on the 'printed-cricuit boards' (PCBs) is described in the section following. The Pre-Processor module is designed to pre-process 64 analog input signals from the calorimeters. This entails, that the basic hardware-structure of the module is given by the processing chain for those 64 channels.

#### 2.1 The 'real-time' signal path to the Trigger Processors.

The steps of processing for an individual channel are depicted in the figure below. The diagram reveals, that almost all 'algorithmic' functionality is concentrated on the PPrMCM (and the PPrASIC thereon). However, the analog signal handling as well as all control- and data-access is implemented on the PCB level. The following subsections address these issues.

Figure 1: Block diagram of pre-processing for one calorimeter trigger channel.

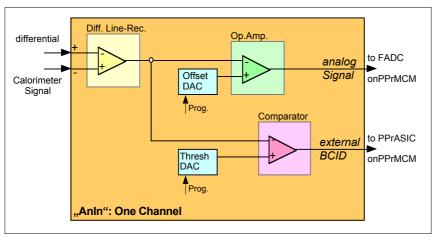

## 2.1.1 The input and conditioning of analog signals.

Every analog signal is taken from the front-panel connector to a differential line-receiver, where a single-ended signal is formed. Most signals are charge-balanced. Bipolar shaping gives a 'fast' half-wave used for triggering purposes, which is balanced by a 'slow' half-wave of opposite polarity but identical area.

All signals from 'Liquid Argon' calorimeters, which deliver about 75% of analog trigger inputs, are of this type. Only the 'Tile' calorimeter delivers unbalanced pulses typical for Photo-Multiplier tubes.

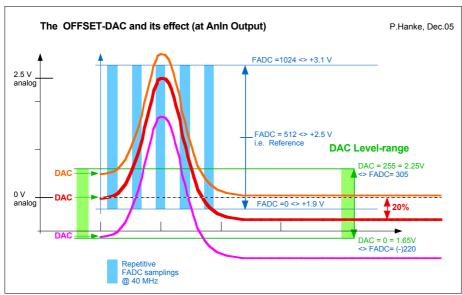

A voltage-level can be applied to any input-signal to map it into the digitisation window of the FADC. A programmable 'Digital-to-Analog Converter (DAC)' produces a DC-level output, which is added onto the signal. One DAC output is allocated to each signal-channel for individual adjustment.

Also, the analog signal is rescaled an Operational Amplifier to match the linear amplitude-range to the FADC-window.

The conditioned analog signal is fanned out to two destinations:

- 1. The analog signal is routed directly to the PPrMCM, where it is digitised in the FADC.

- 2. In addition, the signal is viewed by a comparator, which marks the threshold crossing in time by a the 'rising edge' of its digital output. The threshold of the comparator is adjustable through another programmable DAC for each channel individually. The output signal goes also to the PPrMCM, where the PPrASIC marks the correct LHC clock-cycle. This constitutes one of the three implemented possibilities to perform 'Bunch-Crossing IDentification' (BCID).

The functions of the analog input stage are outlined below.

Figure 2: Block Diagram of 'signal conditioning' and 'external BCID'.

The 'external BCID' comparator raises a digital output-level to logical '1' when the input crosses the programmable threshold in time. The other branch attenuates the signal to match the width of the FADC-window. Furthermore, the signal is 'lifted' to the FADC-input by addition of an appropriate DC-level. The result is shown below.

Figure 3: Mapping an analog calorimeter signal into the FADC.

It should be noted, that the example depicted shows a 'Liquid-Argon' signal, which is charge-balanced. The first part shaped 'narrow' (50 nsec peaking-time) is used for triggering. It is followed by a 'wide' undershoot (400 nsec length) of equal area (balancing integral). Thus, the net charge-flow is nil on this signal-line.

The figure indicates the range of DC-levels that can be applied through the programmable DAC.

Three cases are shown:

- a. the level lies well below the bottom of the FADC-window. Hence, the digitisation applies an effective threshold. This setting suppresses excessive 'noise', if present on analog lines.

- b. the level moves the signal's baseline just above the bottom of the FADC-window. This is a very likely setting at LHC-start, because it allows measurement of a noise-distribution on both sides of the base-line yet leaves also maximal digitisation-range for threshold-setting further downstream.

- c. the DAC is set to its top-end. With such a setting the full swing of a LAr calorimeter signal can be digitised including the 20% undershoot amplitude. There are technical aspects, where this is useful (e.g. the shape of the undershoot tells about electron-absorption in the Liquid Argon).

An essential task in pre-processing is the identification of the proton-proton collision in time, i.e. on the clock-raster defined by the bunch-structure of the LHC. All-together, three methods for BCID are implemented in the design of the PPM. The purely 'digital' methods (A, B) are part of the PPrASIC functionality. For completeness sake, all three methods are briefly described here:

#### A. The FIR-Filter BCID method.

A pipe-line in the PPrASIC stores five consecutive FADC-samples, applies weights by multipliing the samples in the pipe with pre-defined coefficients and sums up the resulting values. Thus, the integral over a calorimeter signal is derived, improving transverse energy-resolution and minimising noise-contributions. A subsequent 'peak-finder' identifies the time-slice with the maximum value and attributes the 'pulse-integral' (energy value) to this LHC clock-cycle. The working range of the method spans from small signals (few GeV equivalent) over the linear signal range (up to ca. 250 GeV) into 'near' saturation. The limit is reached, when several consecutive samples are 'clipped' to the maximum FADC-value.

## **B.** The 'digital BCID for saturated pulses'.

Two consecutive FADC-samples are compared to a 'low' and a 'high' threshold in the PPrASIC making use of the finite 'peaking-time' (50 nsec) of any analog input signal. Thus, detection of a 'leading edge' allows attribution of a 'virtual peak' to a certain LHC clock-cycle, which is the 'bunch crossing' for a saturated signal. The working range starts within the 'linear signal' range (ca. 200 GeV) reaching to 'infinitely' high energies.

#### C. The analog 'external BCID' on the AnIn daughter-board (see above).

The free-running (i.e. clock-independant) comparator indicates a threshold-crossing by its rising digital output. Given the shaper-defined peaking-time, BCID is performed by a properly delayed 'marking' of the correct time-slice in the PPrASIC. The working range starts well above the pre-defined comparator-threshold (to avoid 'glitches') and extends to 'infinity'. Hence, a large overlap with the other two mechanisms gives redundancy, which allows consistency-checking among the BCID-methods.

The signal formation is implemented on a daughterboard (AnIn). Each plug-on PCB holds 16 input channels, thus matching the modularity of the input connectors. This piece of hardware interfaces to remotely located electronics on the detectors. Exchangability of the part on the motherboard is useful allowing fast repair, if some external source has inflicted malfunction.

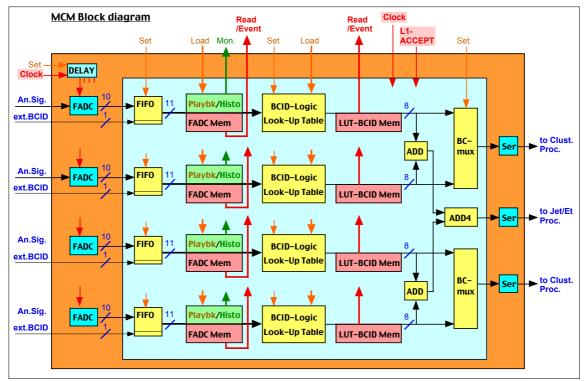

### 2.1.2 The actual pre-processing on a 'Multi-Chip Module'.

The PPrMCM carries all of the important pre-processing elements in the real-time data path. It is also realised as a plug-on unit. The argument for exchangability of this particular unit has been made elsewhere. Only its functional content and its interface to the motherboard is important in this context.

Figure 4: The principal functions located on the Pre-Processor MCM.

Each PPrMCM handles 4 signal-channels. Hence, the PPM allocates mounting space and signal routing for 16 pieces of PPrMCMs. Because of the concentrated functionality, the consumed electrical power on each MCM is not negligible. A heat-exchanger mounted onto each PPrMCM ensures efficient removal of the heat produced.

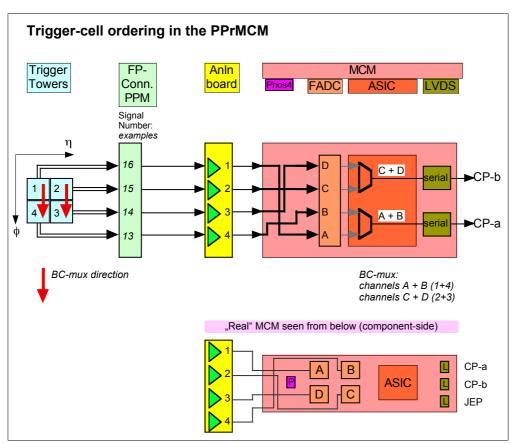

Figure 5: Trigger -Towers and multiplexing of calorimeter data.

Arrangement of signals from trigger towers in the calorimetry is not subject here. However, the main axis of all detectors runs along the pseudo-rapidity  $\eta$ . Architectur of the trigger demands the orthogonal direction, namely azimuth  $\phi$ , to be the main axis. Reordering the tower-signals in the 'Receiver System' results in a 'circular' sequence of towers as shown in the figure below. The Pre-Processor produces 8-bit real-time data on the 0.1\*0.1 granularity for the CP and 10-bit data on the 0.2\*0.2 granularity for the JEP.

The 'Bunch Crossing Identification' forces an empty time-slice preceding and following the identified time-slice, because the seen energy is attributed to the identified slice in the processing pipe-line. Furthermore, the massive cabling, that would be needed for the 0.1-granularity, led to the scheme of multiplexing two towers onto one digital data-line linking the Pre-Processor to the Cluster-Processor. As the principal direction in the trigger is the azimuth, the multiplexing follows this axis as shown above.

#### The 'BC-multiplexing scheme'.

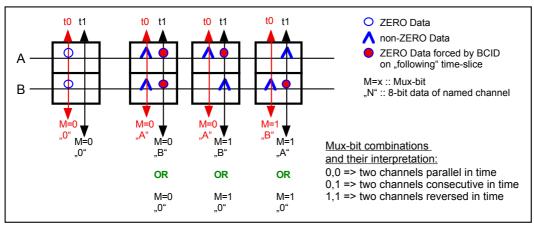

The input signals follow 'linear order' at the MCM-input (channels 1,2,3,4). The trigger architecure requires multiplexed pairs to be pair [A,B] and pair [C,D]. As example, only the pair [A,B] is considered, which is sent serially to the CP labelled 'CP-a'. For one pair, the cases of data sequencing coded into one 'Mux-bit' is visualized below.

Figure 6: The BC-multiplexing scheme.

Subsequent time-slices are labelled 't0' and 't1' respectively. 'M' denotes the Mux-flag-bit. The procedure is the same for the second channel-pair (C,D) on the MCM. Note, that summing 4 channels into a JEP-value is not at all affected by 'BC multiplexing'. The four 'BCIDed' values are summed as they emerge from the BCID-Decision Logic of the PPrASIC.

#### 2.1.3 The serial data in real-time to the Cluster- and Jet/Energy-Processor.

Each of the PPrMCMs delivers three serial output streams at a rate of 480 MBaud/sec. Two of the streams contain data, which represent energy deposits on the 0.1\*0.1 grid. They are input to the 'Cluster Processor'. The third stream contains energy deposits on the 0.2\*0.2 grid, which are sent to the 'Jet / Energy Processor'.

In total, there are 16\*3= 48 signal lines of high frequency routed to the PPM's board periphery. Special 'routing techniques' are applied for such signals. An impedance-matched strip-line together with 'pre-emphasis' of the digital signal at the source is used to fulfill the task.

An additional requirement comes from the architecture of the Level-1 calorimeter trigger system. The allocation of calorimeter signals to electronic modules demands, that certain signals (at the 'azimuthal' boundaries of each module) are duplicated and sent on separate cable links to the processors [see Ref. 1]. Furthermore, the PPM must have the capability to drive a cable link of significant length (appr. 11 m) to the processor-crates.

Figure 7: Pre-Emphasis of LVDS across the PPM and over 11m of 'twin-pair' cables.

The task is attributed to a special driver-component called 'LVDS Cable Driver (LCD)', from which the signals are taken to a backplane connector. The connector is known by the brand-name 'CompactPCI' providing a high connection density combined with good grounding facilities. Its mechanical properties are adequate for a crate-to-crate cable installation.

### 2.2 The VME interconnection and on-board controls.

The Pre-Processor Module is a standard VME 'slave module'. It is interfaced to the VME Bus on the crate backplane providing A32 / D32 access for a computing infrastructure.

VME serves mainly for the purpose of setting-up the modules for ATLAS operation (e.g. setting hardware-registers, downloading FPGA code, etc ...). Another VME application is debugging and/or testing of a module in a laboratory test environment. A laboratory crate does not necessarily have the full readout facilities (RGTM, ROD etc.), yet a module must be accessible for test - including data readout. The physical implementation of VME Bus follows the 'Standard'. The Pre-Processor crate is a 'off-the-shelf' VME-crate of 9U height equipped with a VME64xP backplane.

Design studies, made a long time ago, resulted in a board configuration for the PPM as shown in the figure below. This demonstrates, that the architectural considerations have not changed significantly since the early days of the ATLAS-project.

#### 2.3 The data readout to DAQ.

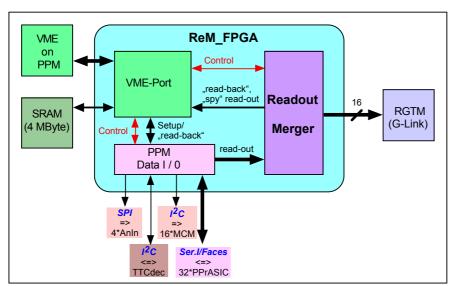

The 'data gate-way' into / out of the PPM is realised in the large, configurable device called ReM\_FPGA. The VME Bus as well as the uni-directional G-Link (to ROD and DAQ) do interface to this central device on the PPModule.

Early work on the 'PipeLineBus' principle resulted in an ASIC-design to accomplish the task of 'merging data from the PPM sources for readout'. Due to the limited number of devices needed (1 per PPM) and due to the flexibility provided, a decision was made to use a 'Field Programmable Gate Array' instead of an ASIC.

The tasks of the ReM\_FPGA comprise the following issues:

- Interface to I<sup>2</sup>C busses for special devices (Phos4, TTCrx) on the PPM.

- Connect-up and serve the 2\*16 'serial interfaces' of the PPrASICs on the 16 MCMs.

- Interface to VME for control and low bandwidth readout.

- Interface the PPM data readout to the serialising RGTM-O (and to ROD and DAQ).

The device is a XiLinx Virtex XCV1000-e. The pin-layout at the package has been defined such, that FPGA-resources can be used optimally by firmware-code.

Figure 8: Estimate of 'Real Estate' on a PPM-board.

## 2.4 The Level-1 protocol via TTC: Clock, L1-Accept ...

The PPM, as a 'pipelined device', is driven by the LHC clock. The readout facilities require signals from the real-time protocol like the 'L1-Accept'. Synchronisation of internal counters, such as the 'Bunch-Crossing' counter or the 'Level-1 Event' counter, is given by periodic RESET signals. Furthermore, a synchronous START signal is required to push data from 'playback' memories into the real-time data path for a stand-alone check of the trigger system.

These signals are provided by the TTC system on optical links. Each of the eight Pre-Processor crates will receive such a link. A 'Timing Control Module' (TCM) receives the optical signal-stream and provides electrical output for point-to-point distribution to 18 module-stations in a crate (16 are required for the Pre-Processor). The distribution is implemented as an auxiliary board plugged onto the crate's backplane along the J0-connectors. The PPM receives the TTC protocol through a TTCrx ASIC, which is located on yet another daughter-board called TTC Decoder (TTCdec). The output comprises the required signals ready for on-board use in the components concerned.

### 2.5 Slow Control.

The infrastructure of a crate (supply-voltages, supply-currents, fan-speed) is controlled via the standardised 'slow-control' system CAN-Bus implemented in the purchased VME crate.

Reliable system operation requires in addition monitoring of certain quantities on the module-level. Examples are the temperatures of PPrMCMs, the operating voltages and supply currents on each PPM board, the on-board produced supply-voltages for special components and more. This is achieved by a CAN-Bus interface, which transmits the module-information to a crate-level controller (implemented on

the TCM). The PPM stations are connected to the TCM via a CAN-Bus realised on the same plug-on backplane as the TTC-distribution.

#### 2.6 The Crate environment.

The architecture of the Pre-Processor system is matched to the calorimeter input as far as possible [**Ref. 3**]. For reasons of trigger latency, proximity of racks/crates is required for housing the following sub-systems:

- 1. Calorimeter Receiver Stations,

- Pre-Processor.

- 3. the subsequent trigger processors (CP, JEP),

- 4. the Central Trigger Processor (CTP).

The proximity avoids unnecessary cable length. The ATLAS detector has two regions (the junctions between barrel and endcap on either side), where the bulk of trigger signals come from. Hence, the cables feed from the sides into a row of electronics racks lined up parallel to the detector. Signals pass first through the 'Calorimeter Receiver Stations', where - among other things - 'transverse energy' weighting is applied for the purpose of triggering.

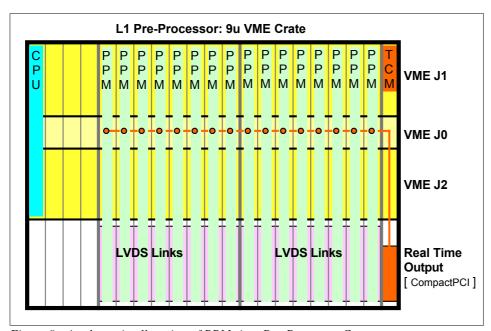

Special attention is paid to the layout of cable routes, because the amount of cables is significant: appr. 4000 analog signals arrive at the trigger electronics for each hemisphere of pseudo-rapidity. The cables are rather massive as they carry 16 signals each on twisted pairs. For this reason, a scheme of 'alternating sides for Input / Output' has been adopted. Cables from the detector enter the 'Receiver Stations' at the rear (backplane-side). Output goes from the front-panel to the front of the respective Pre-Processor Modules, from where the 'LVDS links' leave from the rear (backplane-side) to reach the trigger processors. Coverage of the entire ATLAS calorimetry requires 2\*4= 8 Pre-Processor crates. The layout of one Pre-Processor crate is detailed in the figure below.

Figure 9: A schematic allocation of PPMs in a Pre-Processor Crate.

As an example, a group of 8 PPMs is allocated to the electro-magnetic part and a group of 8 PPMs to the hadronic part of calorimetry. However, a particular allocation of modules is not mandatory, because access to control-parameters for each individual channel is given on the PPM (e.g. loading of BCID coefficients, LUT content etc...). Hence, other schemes of module allocation can be and have been adopted as long as the module-defined correspondence between input connector and LVDS-output is observed [Ref. 4].

**Important Note:** All PPMs in the Pre-Processor system are identical in hardware.

A crate holds additional modules important for the system's operation.

A TCM [Ref. 5] receives TTC signals on an optical link and distributes them electrically on point-to-point links to the PPMs in the crate. In particular, the LHC clock, L1 'Accept' and other essential protocol-signals travel on this path across the experimental set-up. Another function on the TCM is the mastering of the afore mentioned CAN-Bus to/from the modules in the crate. A third role assumed by the TCM is a VME bus-display at its front-panel for visual diagnostics.

A network-connected CPU in the crate acts as local controller of the VME Bus. The tasks comprise the loading of parameters into the PPMs, local monitoring using non-triggered calorimeter signals recorded in ASIC-hardware and monitoring of event-data in 'spy-mode'. The number of stations available in a crate is nearly used up with this arrangement. With a CPU installed in the left-most slot (slot#1), only a three places (slot#2 to slot#4) are left free.

## 3. The Realisation of the Pre-Processor Module.

The system's architecture follows a sequence of modularities based on powers of 'two'. It starts with the detector input broken down into groups of four channels. This 'granularity'along with implementation-studies, made on small building blocks, showed the feasibility of the present, uniform board-layout. A detailed description of the module's periphery is given in the appendices. The connectivity is of particular importance for interfacing to systems 'upstream' and 'downstream'.

# 3.1 The physical implementation of the Pre-Processor Module.

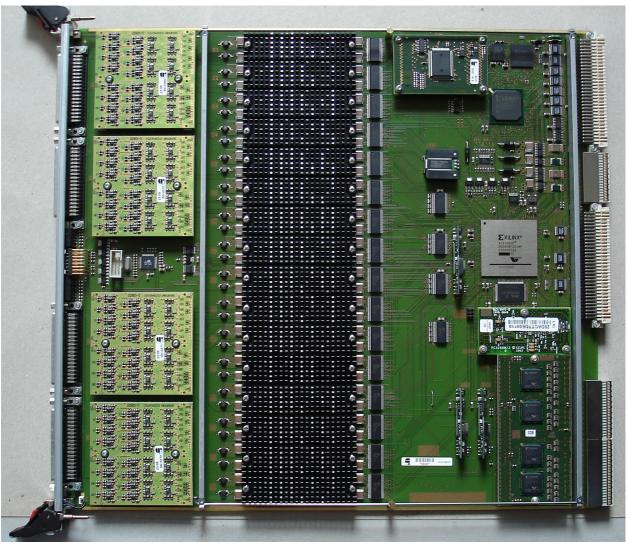

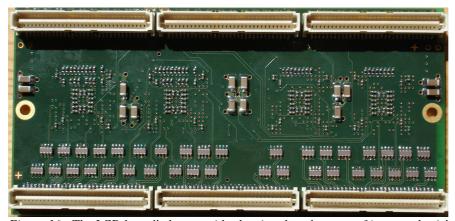

Architectural considerations outlined earlier (see Ref. 1) led to a design of the Pre-Processor module as shown in the figure below [Ref. 6].

Figure 10: The Pre-Processor Module (prod.-version 2.1).

The direction of flow for the real-time signals is from the left (front-panel connectors for analog input) to the bottom-right (backplane) side, where serial data streams (480 MBaud/sec) leave the module.

Easily visible are the many sub-components, which populate the motherboard:

- Four 'Analog Input boards (ANIN)' at the left.

- Sixteen 'Multi-Chip Modules (MCMs)' showing as 'column of heat-sinks' in the center.

- One 'Lvds Cable Driver (LCD)' at bottom-right.

- One 'TTC Decoder (TTCdec)' directly above the LCD.

- One CAN-module at top-right.

- One 'Readout Merger FPGA (ReM\_FPGA)' at center-right (Xilinx).

Not only global heat-removal is important, but also a strong temperature-gradient between the 'bottom' and the 'top' of the PCB is not wanted. A high-flux air-stream from a cooling heat-exchanger is forced by fans from the bottom upwards through the crate. Temperature dependance of e.g. timing or reliability of components is not allowed to vary across the 64 channels on the motherboard.

## 3.2 Dimensions, Mechanics, visual Indicators.

The Pre-Processor module is configured as a PCB with a height of 9 NIM units (366 mm) and a depth of 400 mm. In fact, the depth has been reduced to 399.5 mm, because the strain on handles was too big when the board was inserted in the crate. Otherwise, the design follows the 'VME standard' [Ref. 7] set out for such modules. The number of layers is 8. Five layers are pure 'routing layers'. Three layers are used for full (or partial) power planes: +5.0V; +3.3V; GND (Analog-GND).

The PCB thickness is 2.0 mm required for sufficient rigidity along the board's lateral dimensions. The backplane side is equipped with several connectors each having a fairly high pin-count. Any misalignment at insertion-time has catastrophic effects on the backplane in the crate. A 'macroscopic' addition is the implementation of mechanical stiffening for board-insertion/ extraction: the vertical stiffening rails are connected by two horizontal rods (top and bottom), which are supported midway. These rods add significant longitudinal strength to the board, when insertion forces are applied. Furthermore, the mechanical appliances (front-panel, extraction /insertion levers, 'grounding' etc.) comply with the IEEE standard 1101.10.

Reliability for long term operation also requires robust mechanics on the PCB itself. Vibrations from cooling fans and/or other influences to connection-stability are not allowed to compromise the performance. Hence, all daughterboards are fixed to the motherboard by screw-fixations (see picture of PPM).

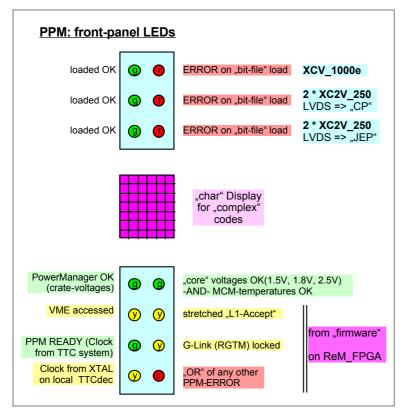

Front-panel space is very limited due to the large number of input signals. Nevertheless, the free space in the center of the panel is allocated to visual indicators (LEDs).

The indicators inform on the status of:

• Firmware-loading (green = ok, red = loading failed):

for the ReM\_FPGA (XCV1000e)

for the LVDS repeaters sending data to the CP

for the LVDS repeaters sending data to the JEP

- the crate-supply voltages (green = ok)

- the on-board generated voltages (green = ok)

- VME data traffic activity (yellow, 100 ms stretched DTACK)

- the arrival of 'L1-Accept' (yellow, 100 ms stretched)

- the TTC system clock (green, 100 ms stretched), i.e. PPM runs in DAQ mode.

- DAQ readout activity, i.e. ReM\_FPGA output via G-Link is active (yellow).

- the local XTAL clock (yellow, 100 ms stretched), i.e. PPM runs in local check-out mode.

- OR of all ERRORs on the PPM (red = PPM not operational).

Figure 11: The status indicators on the PPM front-panel.

The front-panel holds also a matrix-display element, which shows more complex information on e.g. error-states. These states are coded to 'characters', whose meanings point to detailed information. Naturally, a 'conversion table' is required for interpretion. The character-codes will be defined, when experience grows in operating large parts of the PP-system.

It was assumed, that rack-hardware allows connection of analog input cables from above and below at each crate, thus leaving a visible space in the center of the front-panel, where the LEDs are located. The final installation in ATLAS-USA15, unfortunately, brings cables from one direction only (either from top or from bottom) to a crate obscuring free view of the visual indicators.

### 3.3 Grouping of functional blocks, dissipated Power.

The following section describes the stages of signal processing implemented in hardware across the Pre-Processor Module starting from analog inputs to the real-time digital outputs. Data access for control as well as readout for checking purposes is given through VME. Readout data for DAQ are passed on to the RGTM by the ReM\_FPGA upon receipt of a 'L1-Accept'. TTC input for real-time operation and 'slow control' of environmental parameters complete the module's functional content. An estimate of dissipated power together with practical considerations for efficient removal of produced heat ensures the viability of the PPM design.

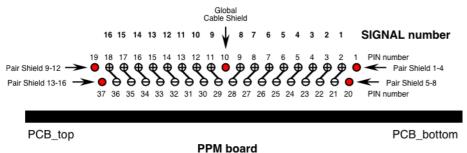

#### **3.3.1** AnIn

The Pre-Processor module receives 64 analog input signals from the calorimetry. The signals are grouped into four cables (16 channels each) with specially configured connectors for minimal cross-talk **[Ref. 8]**. The layout of the connector along with the allocation of calorimeter signals is given in **Appendix\_A**. Each connector has a pair of fixation screws, which ensure proper electrical contact along with safety against accidental disconnection.

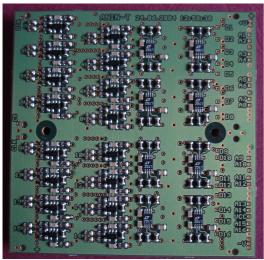

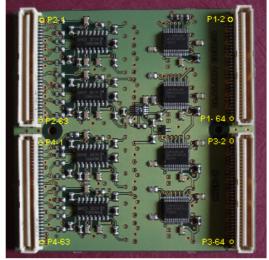

The incoming analog signals are routed directly to the 'AnIn' daughter-board [Ref. 9]. There are four such boards on the PPM matching up to the signal channels on the four input-connectors.

Figure 12: The 'AnIn' daughterboard (left:top; right: bottom with connectors)

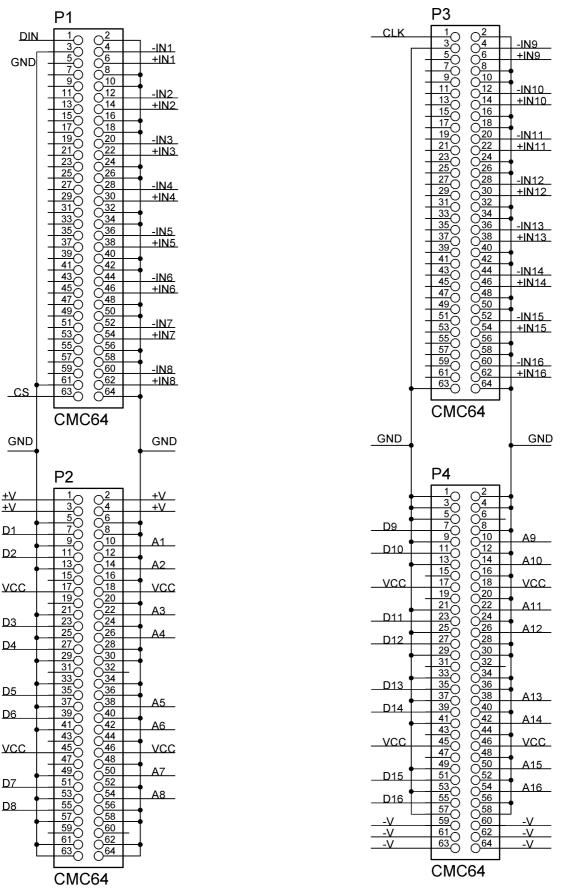

Connectors, known from the CMC standard (Common Mezzanine Card), are used to interface the daughterboard to the PPM. Layout-studies of the 'AnIn' PCB have shown, that the functionality can be implemented on daughterboards of size restricted by the vertical dimension of the motherboard.

Two kinds of outputs are transported directly across the motherboard to the PPrMCMs as input for each channel (trigger cell):

- 1. A uni-polar analog signal conditioned to the input of the digitising FADC.

- 2. A digital signal, whose rising edge represents the point in time when the analog signal crosses a pre-set voltage threshold. The signal is used further downstream for so-called 'external BCID'.

The list of connector-pins interfacing the AnIn-module to the motherboard is given in **Appendix\_B**.

#### 3.3.2 PPrMCM

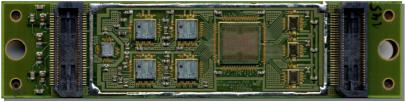

The PPrMCM and its functionality are described in separate documentation [Ref. 10]. The pinning of the two connectors is given in Appendix\_C. The connectors M1 (on the left in the figure below) and M2 (on the right) have 60 pins each with 0.5 mm pitch. This is a very sensitive electro-mechanical device requiring special care. Intrusion of dirt can impede the connection-quality in a severe way leading to a malfunction, which can be difficult to locate.

Figure 13: The 'bonded' components on the PPrMCM (brass-lid removed).

Figure 14: The 'heat-exchanger' on the PPrMCM top-side showing a 'Serial Number'.

## 3.3.3 LCD

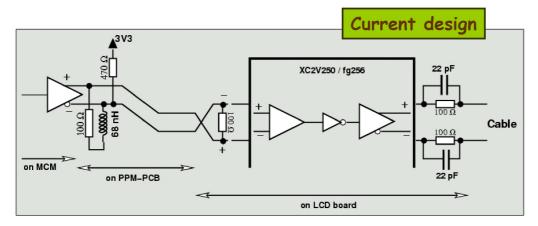

Two separate output streams (to CP and to JEP) are created on every PPrMCM. Each stream carries serial data of high speed (480 Mbit/ sec). Hence, careful routing of these signals via impedance-matched strip-lines has been implemented from the PPrMCM to the LCD daughterboard. The system architecture requires duplication (fanout) of certain data-streams on the Pre-Processor level [see Ref. 1]. Hence,

capability is provided to drive the signals over a 'parallel pair' cable to its destination processor, which can be as far as 15 meters away.

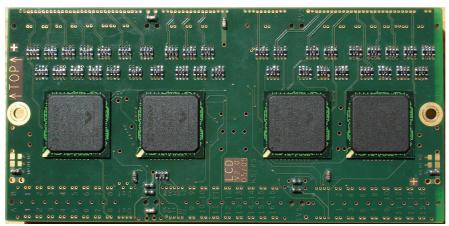

Figure 15: The LCD board's top-side with 4 FPGAs and part of 'pre-emphasis' circuitry.

Figure 16: The LCD board's bottom-side showing the other part of 'pre-emphasis' circuitry.

The duplication of signals is done inside the FPGAs (X2CV\_250), where one input from the PPrMCM is routed to two output drivers. Studies of LVDS transmission [Ref.11] have shown, that it is necessary to 'pre-compensate' losses due to the cable's integration properties. This is achieved by passive components (R, C) placed close to the FPGA outputs. The exact dimensioning of the pre-compensation network (values) depends somewhat on the cable length. It is optimised for cables with a length of 10 to 15 meters.

#### 3.3.4 TTCdec

Signals, distributed through the TTC protocol tree, are received on the PPM from the auxiliary backplane across the J0-connectors in a daughterboard called 'TTCdec' [Ref. 12]. The protocol-stream is decoded and individual signals are distributed to their destinations on the motherboard (PPrMCMs, ReM\_FPGA, ...). Apart from reception and board-level distribution of 'real-time' protocol signals (e.g. 'LHC Clock', 'Level-1 Accept', 'Bunch-Counter Reset', 'Level-1 Event-Counter Reset' etc.), the TTC system is the only means to control synchronous system activities.

Such system-wide applications in the Pre-Processor are:

- 1. Sending a 'global' RESET to the entire system.

- 2. 'Starting' and 'Stopping' data play-back from on-board memories for testing purposes.

- 3. 'Start' and 'Stop' of sending LVDS synchronisation patterns initiated by the 'LVDS\_Sync1' signal on the PPrMCM.

Access to parameter settings on the TTCdec is given through a separate I<sup>2</sup>C bus originating on the ReM\_FPGA, which maps the registers to VME (see chapter 4 for details).

## Reminder on I<sup>2</sup>C adressing:

Observation: The TTCrx chip can lose its I<sup>2</sup>C-address, which is generated from an on-board hardwired I2C\_ID. Only an immediate (within few msec) access after a 'reset' or a 'read/write' operation is always successful, i.e. acknowledged by the TTCrx.

Explanation: A standalone PPM uses the on-board crystal oscillator and not the encoded TTC signal with the embedded clock. The TTCrx has a 'watch-dog' circuit, that monitors whether its internal PLL has locked. But, without external TTC signals to the TTCrx, the PLL will not lock. As a consequence, the 'watch-dog' circuit detects the improper 'lock-state' and initiates an internal 'reset'. The procedure is permanently repeated as long as there is no external TTC signal to the TTCrx present. An 'odd state' of the TTCrx chip is the result, which gives rise to I<sup>2</sup>C access problems. Tests with a TTC clock present never show any kind of I<sup>2</sup>C access problems. i.e. I<sup>2</sup>C cycles are always acknowledged. This is a 'bug' in the TTCrx design, which has to be kept in mind when operating the PPM in a test-rig without TTC input.

Conclusion: If externall TTC is missing,  $I^2C$ -access is only possible by 'cheating the watch-dog', e.g. by 'double' write-access within the watch-dog interval .

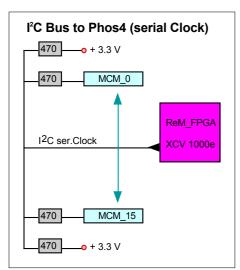

# 3.3.5 The 'special' I<sup>2</sup>C bus to Phos4-chips on the MCMs.

The timer-chip called Phos4 was one of the first 'utility' devices developed at CERN for LHC-experiments in general. Time-adjustment with 1 nsec resolution over a LHC clock-cycle of 25 nsec is indeed a necessity in many parts of experimental apparatus. The Pre-Processor is one of these systems. The exact setting of the digitiser-strobe in time to the peak of an incoming analog signal is essential to obtain optimal energy-resolution. Hence, the Phos4-chip was implemented from the start of design as the 'fine-timing' component.

After the production of Phos4-wafers, tests were carried out to verify the performance of the device. Already here a problem showed up. The feedback of the 'delay-lock loop' can hang-up putting the step-size of Phos4-delays either to minimum or maximum values. The PPrASIC, under development at the time, took over the task to sense Phos4-activity by counting feedback pulses within a given time-interval. If no feedbacks occur, the PPrASIC signals an 'error-state' to the supervising software requiring corrective action.

In addition, the device was missing the usual 'reset' function, which is required for such a component to be used in a complex system. The only way to 'reset' the Phos4 was to cycle the supply-power to put it back into a defined mode of operation. However, the chips were already produced in the required quantity. Therefore, the system had to cope with this feature. There are several possibilities to cycle power on a Pre-Processor Module:

- 'switch off/on' the crate manually (not an option for ATLAS operation).

- 'switch off/on' via the hot-swap controller on the front-panel lever (almost as bad...).

- 'switch off/on' via the CanBus (that is, what CAN is for ...).

- 'switch off/on' via VME and the hot-swap controller (another possibility ...).

When the MCMs were built, testing of the production series revealed another problem, which only showed up rarely. It was not observed in tests of small MCM quantities. The I<sup>2</sup>C serial bus transporting set-up data showed sensitivity to noise-glitches when the rise-time of the clock was 'slow'. The input to the Phos4 re-triggered on such glitches causing loss of the set-up data. It was cured by introduction of a 'pull-up' combined with termination resistors.

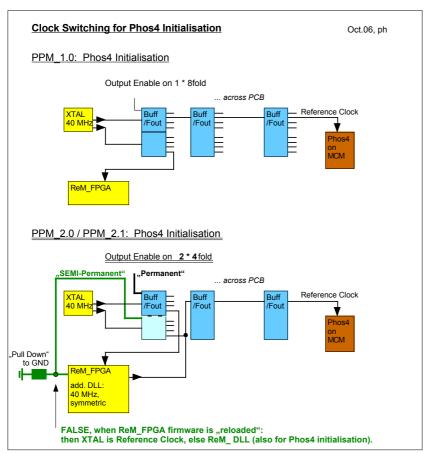

A pre-series of Pre-Processor Modules (PPM\_1.0) was built with confidence, that all trouble had been eliminated. However, on the module-level yet another feature appeared. Again, this could only be observed on a small fraction of channels. Intensive debug work revealed, that the Phos4 requires a 'highly symmetric' reference clock (very nearly 50/50 duty-cycle) to ensure continuous operation of the DLL feedback. The clock provided by an XTAL oscillator (see top half of figure below) is not symmetric enough (45/55) causing Phos4 hang-up on some channels. Hence, the ReM\_FPGA has to be used as 'facility' to provide a substitute XTAL-clock of required symmetry (see bottom half of figure below). The scheme implemented (PPM\_2.0 and PPM\_2,.1) has been tested extensively. The switching of clock-sources (phase-jump), when a firmware reload takes place, does not cause interuption of Phos4 operation.

Figure 17: Clock-distribution for the 'special' 1<sup>2</sup>C bus to Phos4-chips on the MCMs.

Figure 18: Providing clocks on the PPM.

## Note on latching FADC-data (and external BCID-bit).

The range of the Phos4-delays cover the full LHC-clock cycle. Depending on the Phos4-delay set (i.e. position of the FADC-strobe), the encoded data change. If data are latched for synchronous operation in the PPrASIC while changing, 'random data' appear in the processing downstream. To avoid this ambiguity, latching in the PPrASIC must be set according to the following rule (see also PPrASIC User Guide [10]).

- For Phos4-delays [0 nsec to 9 nsec, 22 nsec to 24 nsec], the data must be latched using the NEGATIVE clock-edge.

- For Phos4-delays [10 nsec to 21 nsec], data must be latched using the POSITIVE clock-edge. Note that, this causes the data to appear a whole latency-tick later in the processing pipe-line. Hence, this one

tick-delay must be compensated by removing a delay-step in the PPrASIC delay-FIFO.

#### 3.3.6 VME and Static RAM

The VME interface supports the slave-protocol as outlined in the corresponding specifications [see Ref. 6]. The VME implementation complies with A32 / D32 data-transfer. During development of the PPM, it was decided that wider data-access (D64) was not required.

The module recognises the following address-modifiers issued by a master-CPU in the crate:

- 0x09 Extended nonprivileged data access

- 0x0A Extended nonprivileged program access

- 0x0B Extended nonprivileged block transfer

- 0x0D Extended supervisory data access

- 0x0E Extended supervisory program access

- 0x0F Extended supervisory block transfer

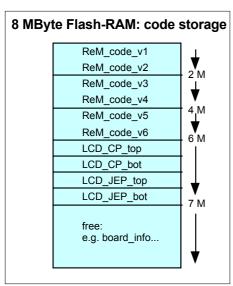

The key-component for the readout interconnection of the PPM is the ReM\_FPGA located near the backplane. It provides Input / Output functionality, which is all implemented in the FPGA code. A VME accessible Flash\_RAM holds the FPGA code for a fast 'loading' locally [Ref. 13].

Figure 19: Storage of firmware binaries in Flash\_RAM.

The generous Flash-RAM space is attributed to firmware versions as shown in the figure above. Since the LCD FPGAs contain only fixed 'routing / fanout' firmware for signal-distribution, only one version is foreseen to be held here. The ReM\_FPGA is quite a different case: up to 6 versions can be stored. Examples could be:

- 1. Speed-optimised 'production version' for DAQ

- 2. 'debug version' for front-end (SPI, I<sup>2</sup>C, writing to Ser. Interfaces)

- 3. 'debug version' for back-end (DAQ readout from Ser. Interfaces)

- 4. 'debug version' for checking 'read-back' of settings

- 5. ...

- **6.** ...

The functionality of the ReM FPGA comprises the following 'hardware' tasks:

- A 'Serial Programming Interface' (SPI) is provided to set DACs on the four AnIn daughterboards. They define analog values for thresholds (external BCID comparator) and analog offsets (baseline shift of analog input-signal).

- The timing elements (Phos4) on the PPrMCMs are set by means of a I<sup>2</sup>C bus. The bus master is implemented as FPGA code.

- Another I<sup>2</sup>C bus master assures communication with the TTCdec daughterboard.

- 'Write' and 'read' access to each PPrASIC is possible through 'serial interfaces'. As there are many (64) channels on a PPM, 'serial interface'-ports are implemented in a number to serve 'doublets' of channels, namely 32.

<u>'Historical' Note:</u> It is explicitly stated, that 32 serial interfaces are provided to serve the 'doublets' of PPrASIC-channels. Only, if severe technical problems would have arisen (e.g. excessive routing density on the main board), the 'fall-back' of daisy-chaining the two channel-doublets on each ASIC would have been considered. As a consequence, all four PPrASIC-channels on a PPrMCM would be served by one serial interface only. This would have reduced the number of serial ports to 16 on the PPM's ReM\_FPGA, but would have demanded a sacrifice on readout band-width.

- The ReM\_FPGA is the communicating partner to VME bus. To facilitate data-transport to VME, a synchronous static RAM (S-RAM) is implemented, where blocks of data can be stored intermediately. The size of the RAM is 1M locations \* 36 bit width, of which 32-bit words are 'seen' by VME. The data arrive as 'pieces' from the different sources on the module and can be accumulated in this 'intermediate' store. Examples are

- ASIC-register contents read back for verification,

- 'rate-meter' results from individual channels,

- 'unbiased' histograms of FADC digitisations from individual channels. ...

The accumulated and arranged results can be transferred as 'block data' via VME to the analysing CPU in the crate.

<u>'Historical' Note:</u> A decision on the type of FPGA had been taken some long time ago for the 'XiLinx Virtex XCV1000e'. The chosen chip-package took into account aspects of PCB manufacturing. It is a 'Ball Grid Array' (BGA) with 1.27 mm pitch. The number of input-output connections (560 pin-balls) is sufficiently big to cover the requirements of the PPM. Verilog code has once been developed for a 'demonstrator ReM\_ASIC'. After the decision for a FPGA, a complete re-writing of the code as 'firmware' was necessary for today's implementation on the PPM.

## 3.3.7 DAQ readout

Data readout in so-called 'physics runs' of the experiment (ATLAS-DAQ) uses a different path with higher band-width. The event-related data ('readout') are separated from monitoring data ('read-back') inside the ReM\_FPGA. The readout data are extracted for all 64 channels, formatted with header and trailer and are propagated through the VME-J2 connector to a 'Rear G-Link Transmission Module' (RGTM). The current version of this module with optical G-Link output (RGTM-O) is specified elsewhere [Ref. 14]. The RGTM-O sends the data over a fiber to a ROD [Ref. 15] for collection and/or compression.

## 3.3.8 Dissipated Power, Cooling.

The consumption of electrical power is far from uniform across the PPM. In fact, it has a strong maximum at the places taken up by PPrMCMs. Placement of these components did at first try to distribute the produced heat over the largest possible cross-section with the cooling air-stream. A 'chevron-like' placement of the PPrMCMs was attempted to achieve this (see Figure 5). However, the realisation in a PCB layout showed constraints, which did not allow this. Hence, a fully 'vertical' arrangement was implemented (see Figure 7).

The estimated power consumption on the board is distributed as follows:

- The measured power for the AnIn daughter-board is around 3000 mW each. The four 'plug-on' units contribute **12.0 Watt** to the power-bill of the PPM.

- The power consumption on each PPrMCM is composed as follows according to the specifications of the various manufacturers:

```

4* AD9042 (FADC) 4 * 600 mW = 2400 mW (on +5V)

1* PHOS4 (Timer) = 200 mW (on +3.3V)

1* PPrASIC = 2300 mW (on +3.3V)

3* DS92LV1021 (ser. LVDS transmitter) = 500 mW (on +3.3V)

```

Hence, the summed values (rounded upwards) for a PPrMCM are 2.5 W on +5V and 3.0 W on +3.3V giving a total of 5.5 Watt. It has been shown on 'demonstrators' that the exchange of produced heat with the fan-forced air-flow is guaranteed by the heat-sink mounted on the PPrMCM. The sixteen PPrMCMs

add up to a maximum of **88.0 Watt** on the module, which is concentrated at the PCB center (see Figure 7).

• The remaining logic (VME interface, TTCdec, LCDs and Rem\_FPGA ...) is estimated to consume no more than **40.0 Watt** together.

Hence, the dissipated power of the PPM will not exceed the limit of **140 Watt**. The value is managable in a standard VME64x crate. The following table compiles measured consumptions (for some items) and estimates (for the other items) and relates them to the supply-voltages of the crate.

| Supply  | SubDevice           | Current  | Power  | Comment                                       |

|---------|---------------------|----------|--------|-----------------------------------------------|

| [Volt]  |                     | [Ampere] | [Watt] |                                               |

| + 5.0   | AnIn (* 4)          | 1.5      |        | measured                                      |

|         | MCM (* 16)          | 7.7      |        | FADC specs                                    |

|         | Ancill. Logic (VME) | 6.0      |        | estimated                                     |

|         | Current-Sum         | 15.2 A   | 76 W   |                                               |

| [- 5.0] | AnIn (* 4)          | 0.92 A   | 4.5 W  | on-board from -12V,<br>measured               |

| + 3.3   | MCM (*16)           | 14.5     |        | ASIC simulation                               |

| [+ 2.5] | FPGA-, LCD- I/O     | 1.0      |        | on-board from +3.3V,<br>estimated from specs  |

| [+ 1.8] | FPGA-, LCD Core     | 1.0      |        | on-board from +3.3 V,<br>estimated from specs |

|         | Current-Sum         | 16.5 A   | 55.5 W |                                               |

|         |                     |          |        | [Total: 136 Watt]                             |

Table 1: Estimated Power Consumption of the PPM

Breaking down the requirements of the PPM to supplied power from the backplane results in:

- 50 W to be supplied on +3.3V (ca. 16 Amp)

- 80 W to be supplied on +5.0V (ca. 16 Amp).

This is within the limits set by VME64xP standard. Each pin on the backplane can safely transfer 2 Amp. There are 10 pins allocated to +3.3 Volt supply and 12 pins are allocated to the +5.0 Volt supply (6\*VCC + additional 6\*VCC on J0: see VME64x-VIPA).

A fully equipped Pre-Processor VME crate holds 16 PPMs and some auxiliary modules (e.g. CPU, TCM). The total power amounts to max. 260 A on +5.0 Volts and max. 260 A on +3.3 Volts. The crates and the corresponding power-supply units purchased have the ability to provide this.

A **verification of power-consumption** and a verification of the cooling capability of a fully equipped crate (16 PPMs, 1 TCM, 1 CPU) has been performed in the KIP-Laboratory. The consumption observed on the crate's current-meter is:

175 Ampere on +3.3 Volt, 150 Ampere on +5.0 Volt.

These values translate into appr. **84 Watt comsumed by each PPM** – well below the 'worst case' estimate. The crate has been operated without problems using fan-cooling with ambient air in the laboratory (no water heat-exchanger). Temperature measurements on MCMs show values well within operational limits (max. 60° C).

# 3.3.9 Control facilities (CAN).

#### Local Control of operating conditions.

Each PPM is 'fused' on-board for each supply-voltage in order to prevent damage to the backplane in case of a fault on the module itself. This is defined policy within the 'Level-1 Calorimeter Trigger' project. The PPM follows these guide-lines. Passive fuses produce a high voltage-drop at the currents consumed. Therefore an 'active' solution is chosen. Power ON/OFF is handled by a 'hot-swap' controller 'TPS2345', which is connected to a switch in the handle of the front-panel, but also connected

to CAN. Furthermore, the controller monitors the 'ramping' of each voltage. Unforeseen conditions lead to 'switching OFF'.

#### NOTE.

There are two reasons for the following remarks on 'hot-swapping':

- A. 'bent pins', specially in the LVDS-area, are not catastrophic, but certainly very bad when a full system-installation of 124 PPMs is expected to operate with highest efficiency.

- B. swapping modules in a crate under power is meant to increase system-availability, but the opposite is achieved when neighbouring modules are damaged in the process.

## Removal and Re-insertion of a module (brief guide-lines).

1. When a faulty module is identified, switch it OFF by pressing the red button in the lower handle of the front-panel. Also the left/right neighbours must be switched OFF.

Reasoning: The moving module in the centre could touch neighbours under power with bad consequences.

2. Insert a new module in the slot and slide it back until gentle resistance can be felt.

NEVER apply thumb-force FIRST to the BOTTOM half of the PPM front-panel!

Always push at the top until ,catching' is felt (area of upper analog connectors - they are solid and well bolted to the PCB). The alignment due to the two, fairly rugged' VME-DIN-connectors (J1, J2) with their casing lifts the board to the correct height, because the PCB has up to 1 mm ,play' in the guide-rails.

Reasoning: Normally, the VME connectors catch first. The ,flimsy' CompactPCI has shorter pins (KIP changed this explicitly). By pushing at the bottom, one could still manage for the CompactPCI pins to touch first. With 2 mm pin-raster and 1mm PCB play, a desaster can occur. The insert/extract action is a safe procedure, if executed correctly.

**3.** When done correctly, the PPM 'sits' in the pin-holes. Now, the two levers can push it fully in. Apply force SIMULTANEOUSLY to top-bottom levers with courage. It is necessary to acquire the 'feeling'.

The 'ATMEGA16' micro-controller on the PPM senses several critical quantities on the module and converts them to digital values. These are:

- the voltage across a temperature-measuring diode on the ReM\_FPGA (XCV1000e),

- the voltages across sixteen temperature-measuring diodes on the 16 MCMs.

In addition, the device drives a 7\*5 matrix display to show more complex codes as 'characters' on the front-panel.

List of coded error-states as of Apr.2009 (see 3.3.5):

- 'V' alternating '1'  $\Rightarrow$  +5.0 V on board deviates  $\geq$  10%

- 'V' alternating '2'  $\Rightarrow$  +3.3 V on board deviates  $\ge$  10%

- 'V' alternating '3'  $\Rightarrow$  +2.5 V core-supply deviates  $\ge 10\%$

- 'V' alternating '4'  $\Rightarrow$  +1.8 V core-supply deviates  $\ge 10\%$

- 'V' alternating '5'  $\Rightarrow$  +1.5 V core-supply deviates  $\ge 10\%$

- 'V' alternating '6' => -5.0 V analog-supply deviates  $\geq 10\%$

- 'T' alternating 'n' ('n'=1, 2, 3 ... 9, A, ... G= dec.16) => Temp. of MCM\_'n' exceeds 80°C.

- => 'alternating' display freezes to 'checkered matrix', when the alarm-condition disappears.

- 'checkered matrix' => Module is powered-up only

=> status displays defined by on-line software:

- 'L' => Module is busy with firmware loading

- 'C' => Module is being configured (parameters are loaded)

- 'I' => Module is initialised, ready for operation

- ... list to be extended

#### Remote Control (CAN).

Conditions for the operation of electronics are continously monitored in the ATLAS experiment. Equipment like rack-cooling, crate power-supplies, fan-units etc. are connected to the Detector Control System (DCS) on the level of electronics racks. The back-bone of this 'slow control' system is the serial CAN-Bus [Ref. 16], which allows measurements on the time-scale of minutes or longer. Rack- and crate-level supervision is 'default' in DCS. The Level-1 Trigger system has extended this supervision to the board-level.

The PPr sub-system has a TCM in VME-slot#21 as CAN-master in every crate. The TCM interfaces the external CAN-Bus (DCS) with the internal CAN in the crate, where the individual modules are identified by their slot-number (geographical address #1 to #20). The TCM uses the crate-number (PP-crate#0 to PP-crate#7) as coded on an auxiliary backplane (see **Appendix F**) for CAN-node identification to the external CAN. The CAN-node ID has to be  $\geq 1$ , because ID=0 is used to address all nodes simultaneously. Hence, the PP-system nodes are

| PP-crate | #0     | #1     | #2     | #3     | #4     | #5     | #6     | #7     |

|----------|--------|--------|--------|--------|--------|--------|--------|--------|

| CAN-node | ID = 1 | ID = 2 | ID = 3 | ID = 4 | ID = 5 | ID = 6 | ID = 7 | ID = 8 |

The PPM-CAN interface in form of a daughterboard (see **Ref. 16**) consists basically of a 'chip-size' controller (Fujitsu MB90F594) running CAN-Bus software ('CanOpen' compatible). It receives some quantities directly in digital form (e.g. MCM temperatures converted to °C). Others are digitised on the CAN-board itself (e.g. supply-voltages). All data are transmitted to the CAN-master over bus-lines on the auxiliary back-plane, which is plugged onto the VME64xP-J0 connectors,

The table below summarises the PPM-CAN interface data by listing the quantities to be monitored or controlled.

| Quantity to 'read' | nom.<br>Val. | Resol.   | dig.<br>Val. | dig.   | Range  | Remark                                  |

|--------------------|--------------|----------|--------------|--------|--------|-----------------------------------------|

|                    | 5.0 V        | 10 mV    | 500          | Resol. | 8 bit  | digitised on CAN-board                  |

| supply +5.0 V      | 3.3 V        | 10 mV    | 330          | 1      | 8 bit  |                                         |

| supply +3.3 V      | 3.3 V        | 10 111 V | 330          | 1      | 8 DIL  | digitised on CAN-board                  |

| -5.0 V from        |              | 10 mV    | 500          | 1      | 8 bit  | shifted into pos. Voltages;             |

| supply-12 V        |              |          |              |        |        | digitised on CAN-board                  |

| on-board +2.5 V    | 2.5 V        | 10 mV    | 250          | 1      | 8 bit  | digitised on CAN-board                  |

| on-board +1.8 V    | 1.8 V        | 10 mV    | 180          | 1      | 8 bit  | digitised on CAN-board                  |

| on-board +1.5 V    | 1.5 V        | 10 mV    | 150          | 1      | 8 bit  | digitised on CAN-board                  |

|                    |              | -        |              |        |        |                                         |

| XCV1000e           | appr. 40     | 1 °C     | 40           | 1      | 8 bit  | Oplimits: ok $< 60$ °C; warn $< 64$ °C; |

| temp.              | °C           |          |              |        |        | switch-off > 68°C;                      |

| MCM temp.          | appr. 50     | 1 °C     | 50           | 1      | 8 bit  | Calibrated to INTeger by ATMEGA;        |

|                    | °C           |          |              |        |        | Limits as on XCV1000e;                  |

|                    |              |          |              |        |        | 16 Values from 16 MCM-Diodes.           |

| Quantity to        | nom.         | Resol.   |              |        |        | Remark                                  |

| 'write'            | Val.         |          |              |        |        |                                         |

| 'RESET'<br>to PPM  | 0            | -        | -            | -      | binary | equiv. to 'Power-On' Reset of PPM       |

| 'Pow. ON/OFF'      | 0            | -        | _            | -      | binary | Power ON/OFF to PPM, if enabled by      |

| to PPM             |              |          |              |        |        | missing jumper on Service-Module        |

| VMEtoCAN           | 0            | -        | -            | -      | binary | reset the CAN MicroContr. from VME      |

| RESET              |              |          |              |        |        |                                         |

| VMEtoCAN           | 0            | -        | -            | -      | binary | VME enables CAN Module to load          |

| Program_Select     |              |          |              |        |        | CAN firmware to the CAN                 |

|                    |              |          |              |        |        | MicroController                         |

Table 2: CAN-Interface on PPM.

# 3.4 Latency across the PPM.

The propagation time of a given analog input signal (counted from the signal's peak) has been measured from the input-connector to the LVDS output of the PPrMCM (part 1 and 2 below). The third part (LCD) has been determined separately. The total latency breaks down as follows given in units of LHC clock-ticks:

2

- 1. From Input connector across AnIn-board to input of PPrMCM:

- 2. Processing on PPrMCM: 13 (to JEP)

- 3. LVDS through LCD to the PPM backplane connector:

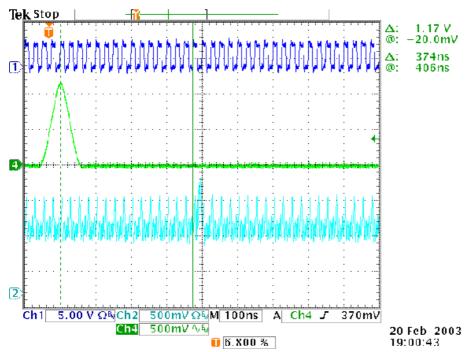

Figure 20: Measured latency (375 nsec) across the AnIn and PPrMCM for JEP-output.

Hence, the total latency contribution of the Pre-Processor Module to the Level-1 pipe-lined system is **16 LHC clock cycles** as compared to 17 estimated in the TDR [see Ref. 1]. The data to the CP are not subject to the 4-cell summing in the ASIC hardware. Hence, the CP data emanate ONE clock-tick earlier, verified by measurement.

The latency measurement has been repeated in 2008 using final production modules. This means, that no more 'estimates' are needed. The measurement covers signal propagation from the front-panel to the backplane connector of the PPM including the LCD daughterboard in the real-time data-path. The results given above have been verified and confirmed.

#### 3.5 The Backplane connectivity.

The implementation of VME Bus follows the VME64x standard. Hence, the upper 6 NIM-Units in the crate are occupied by a VME64xP-VIPA backplane. The allocation of signals specific to the Pre-Processor on 'user-defined' pins of the standardised VME connectors is described later in this section.

Only the remaining lower 3 NIM-Units are available for full-custom installations. The Pre-Processor crate passes the real-time signals (LVDS) through this space for distribution to the subsequent trigger processors. A custom-made backplane fragment holds the 2 mm CompactPCI connectors. There is no signal routing on the backplane fragment, only feed-through of pins extending to the rear of the crate, where a shroud guides the cables plugged in. The pinning of real-time signals is outlined in **Appendix\_D**. Grounding the LVDS-Links is an issue common to the sending (Pre-Processor) and the receiving end (trigger processors). The handling of grounds on the sending side, i.e. on the PPM, is also shown in Appendix\_D. Signal grounds are grouped according to their destination in the subsequent logic. Optional passive components can be inserted to ensure 'cleanliness' of the ground potentials.

The connection to the 'Rear G-Link Transmission Module' for event-readout is implemented on 'user-defined' pins of the VME-connector J2. The allocation of the data- and control-lines is outlined in **Appendix\_E.**

Distribution of TTC protocol-signals from the TCM in slot#21 is realised by point-to-point lines routed on an auxiliary backplane attached to the VME-connector J0. CAN-Bus requires two serial lines across the slots on the backplane. These lines are also realised on this printed-circuit board.

All pins of VME-J0 reach through the auxiliary printed circuit board. Unoccupied pins are used by a small (ca. 4\*4 cm\*²) plug-on board, which carries adapters for 'servicing' the PPM. 'Servicing' means dedicated data I/O for e.g. CPLD re-loading. The pinning of J0 is given in a table of **Appendix\_F**.

## 4. Data transfer to/from the Pre-Processor Module

The Pre-Processor Module can be accessed for full 'read' and 'write ' cycles through the VME bus. VME has all data-sources and all data-destinations mapped to address-space. Hence, everything (also readout data) can be accessed with the speed given by the bus.

A second, equally important, but uni-directional data-path delivers 'readout data', i.e. event-related results from the pre-processing (FADC results, BCID results) to the ATLAS-DAQ. The data are serialised on the auxiliary module (RGTM-O) for transmission on a high-bandwidth link to a ROD and further on to the ATLAS Read-Out System. Both data-paths originate on the ReM\_FPGA of the PPM.

#### 4.1 The ReM FPGA on the PPM

The resources of the ReM\_FPGA are divided into three major parts: the VME-port (VME-ReM Interface), the actual Readout Merger (ReM) and the Data-I/O interfaces to the Pre-Processor hardware.

Figure 21: The functional blocks on the ReM\_FPGA (Virtex XCV1000-e).

The **VME-Port** contains the functionality to write to all data-destinations (configuration registers, 'playback' memories and many others). It is also the 'receiver' of data, which are read back from those locations for verification. In addition, there are other data to be collected through VME, like 'monitoring' memories holding unfiltered trigger input data, 'event-data' memories for spy-analysis etc.. The programming model gives a map of addresses with their data-content.

The **Readout Merger** has to assume several tasks, which can be summarised as 'data routing' and 'data formatting'. The main issues are:

- Control data (read back from configuration registers via Data I/O) are separated off and passed on to VME.

- Monitoring data (read back from accumulating memories), which are only of local interest to the Level-1 trigger (e.g. 'rate-meter' content, 'raw transverse energy' histograms) are made accessible to VME.

- Local (PPr system) usage of event-related data (e.g. detector / trigger cross-calibration) requires the full rate (at the expense of dead-time) to be available via VME. Other applications (e.g. 'spy' analysis) can do with a scaled-down rate of event-data copies. Any local read-out shall not slow-down DAQ.

- <u>Data-acquisition mode for physics as 'top-priority' task</u> requires, that event-related readout data from multiple sources (64 trigger tower channels from 16 PPrASICs collected on the 32 serial interfaces) are merged into a formatted data-record complete with 'header' and 'trailer'

for transmission to a ROD.

The **Data I/O** firmware is an assembly of different bus-masters passing data to and fro under implementation of the correct protocol and data-format.

## 4.1.1 The VME-Port and the 'intermediate' S-RAM store.

The VME bus is directly connected to the ReM\_FPGA. The FPGA, in turn, communicates with a S-RAM. which has 1M locations of 36-bit width (i.e. 4 MByte). The S-RAM control on the ReM\_FPGA uses the memory as 32-bit data fields by truncating VME-addresses accordingly.

The **first** task of the VME-port interface is to exchange data with VME bus across the crate. The module is ready to receive VME 'read / write ' after 'power-up' and 'firmware-load' from the Flash-RAM into the ReM FPGA.

A **second** task of the VME-ReM interface is the supervision of data-flow through the Readout Merger. Set-up data are passed directly over the corresponding Data I/O port to the destinations. After loading the firmware, the 'operation default' puts the ReM into DAQ operating mode, where 'Level-1 accepted' event data are collected. 'Read-back' data are filtered out for local use. Similarly, sub-sets of event-data (spy-mode) are copied.

A **third** task, handled by the VME-port interface, is the data-exchange with the peripheral S-RAM. 'Read-back' data from each ASIC-channel arrive as a 'single word' or 'block' carried along with the 'Level-1 accepted' event-data. It is sensible to pre-collect such data from all channels in the S-RAM. Similarly, a copy of event-data from all 64 channels can be assembled in the S-RAM. VME 'block read' is an efficient way to move these data to a local crate CPU for monitoring and/or local analysis.

Examples of data in the S-RAM are:

- register content, read from subdevices on the PPM (PPrASICs, I<sup>2</sup>C etc.)

- event-data for local monitoring (spy-mode).

- statistical data accumulated in hardware (FADC histograms, 'rate-meter' results).

## 4.1.2 The Readout Merger.

The Readout Merger (ReM) manages the data-transfer from the distributed sources on the PPM. The ReM separates out 'read-back' data from the data collected on the module (see above), it assembles the event-data for DAQ into formatted records and sends these records via the RGTM to a ROD. Furthermore, the ReM has to follow the DAQ-protocol as transmitted by the TTC system. The important signals are:

- The LHC Bunch crossing Clock

- The Level-1 Accept

- The Bunch crossing Counter Reset before each LHC-turn

- The periodic Event Counter (i.e. 'Level-1 Accept' Counter) Reset.

## 4.1.3 The Data Input/ Output ports.

The ports provide the appropriate bus-protocol for shipment of set-up data and reception of read-back as well as event-related data. Three distinct kinds of ports are implemented:

- A 'Serial Programming Interface', which downloads data to DACs without reading-back capability from the hardware devices.

- Two separate I<sup>2</sup>C busses to Phos4s and the TTCdec. The devices can be loaded, but only the latter provides local storage for reading back.

- Thirty-two custom-designed serial interfaces to pairs of PPrASIC channels.

#### 4.2 VME access to the PPM.

The VME bus-protocol is maintained by permanent code residing in a CPLD. Apart from serving 'normal' VME data traffic, the protocol CPLD also holds some registers for operation of the PPM (e.g. Control- and Status Register, FPGA-loading of firmware ....).

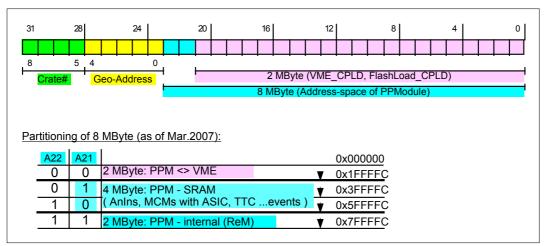

The PPM's space of VME-addresses is shown in the figure below. The four 'top bits' <A31:A28> are used for crate-identification (8 Pre-Processor crates) in the Level-1 trigger system. However, they are only used for addressing a crate/slot via the TTC-system and via the CAN-Bus. They are ignored by

VME, i.e. are set to the fixed value of 0xC or binary '1100', because each crate contains a local CPU as VME bus-master.

Five bits <A27:A23> above the module's internal address-space identify the module in one of the 21 slots of the VME-crate (geographical address).

Figure 22: VME address-space for a Pre-Processor Module.

The PPM requires **8 MegaByte** of address-space, i.e. **0x000000 to 0x7FFFFF**. The two bits at the top <A22: A21> are used for subdivision of the internal module-space. The first 2 MByte (0x000000 to 0x1FFFFF) are allocated to 'common' module-registers in the VME-CPLD. The remaining 6 MByte (0x200000 to 0x7FFFFF) are used for direct access to other on-board registers and/ or memories.

The VME-CPLD passes certain addresses to yet another CPLD, which in turn administrates the 'Flash-Memory' store of firmware-code. It controls firmware-load from the Flash-RAM into the respective devices. Only then, the PPM is ready for operation. The Flash-Memory has its own capacity of 8 MByte. A subdivision here is made for storage of binary code of several firmware-versions ('DAQ', "debug' ... ) for the XCV1000e ReM\_FPGA (6 MByte) as well as firmware for the 'routing and LVDS-driving' X2CV-250 FPGAs on the LCD-daughterboard (2 MByte).

## 4.3 Data model of the PPM.

Testing-software in the laboratory and, more so, DAQ-software requires a full description of the PPM's data-space. The following gives the mapping for control- and readout purposes starting with the PPM as a whole. The module is then be 'broken down' to the sub-module level and, finally, to the channel-level, where the data-space structures are repetitive.

# 4.3.1 General issues.

- All registers are readable over the VME bus, i.e. there are no 'write-only' registers. Status registers are 'read-only' registers; Control registers are 'read-write' registers.

- The 'power-up' condition of all VME registers is 'all zeros', unless stated otherwise.

- A 'byte' is an 8-bit field; a 'word' is a 32-bit field.

- 'Setting' a bit field means setting all of its bits to '1';

- 'Clearing' a bit field means writing '0' into it.

- Bit-setting to '1' is equivalent logical 'true'; '0' is 'false'.

- Each PPM is uniquely identified (e.g. to a local CPU) by its position in a crate. The slot-position is given by coded pins (geographical address: <A27:A23>) implemented in the VME64xP standard backplane.

### 4.3.2 VME addressing.

The VME implementation has been developed for the 'pre-production' PPMs (20 boards of version PPM\_2.0). Those are fully functional modules. The production version PPM\_2.1 has hardware improvements implemented on the PCB-level, which were identified in the final reviews of the design. There are no differences to the pre-production version from the operational point of view.

The following sections describe the VME programming model for the PPM. VME addressing allows byte-wise access on the bus. However, almost all data-locations on the PPM are 4 byte wide (32-bit words). The VME implementation of register addresses is outlined below.

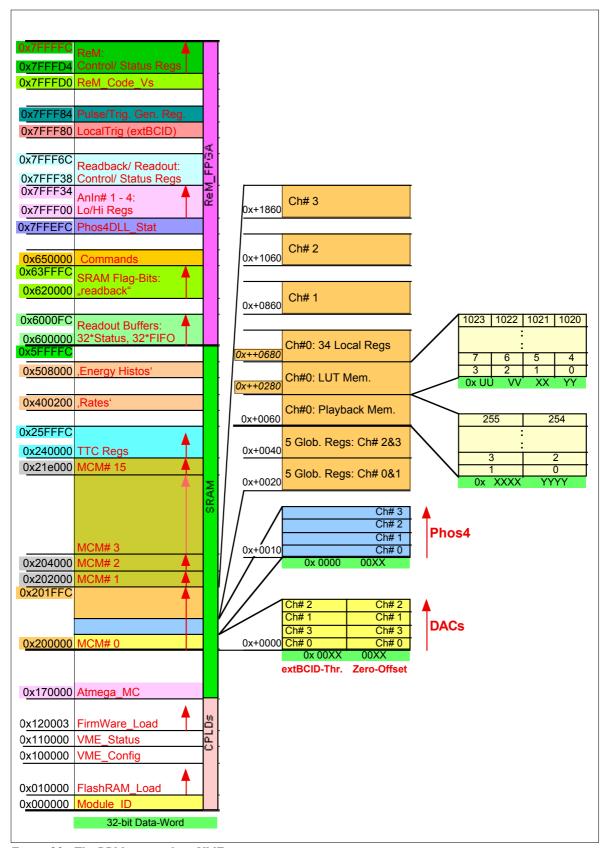

- The addressing starts with an 'Identification Register' at the **base-address = 0x000000**. The on-board store of firmware bit-files (Flash RAM) is administrated through registers at the addresses following. Configuration of the module is achieved and reflected in registers at addresses above **0x100000** ranging to 0x170000, where the ATMEGA microcontroller is accessible.

- The sixteen MCMs occupy each an address-range of 8192 bytes (0x2000) starting at address **0x200000**.

- Operation of the module requires settings in the TTCdecoder module. The TTC parameters are set through registers at addresses above **0x240000**. They are passed via VME through the Data I/O on the ReM\_FPGA. This I<sup>2</sup>C-path is bi-directional, i.e. not only the VME-registers are readable, but also the final data-location on the TTCdec.

- Driven by the TTC trigger protocol (e.g. LHC-Clock, L1-Accept), event-data like FADC samples, LUT-BCID results are extracted from scrolling memories into 'derandomizer buffers'. The data are fetched into the ReM\_FPGA via the 32 serial interfaces to the PPrASICs. The corresponding Readout 'status registers' and 'data-FIFOs' are accessible at addresses **0x600000** to 0x6000FC.

- A range above address **0x620000** holds a map of 'flag-bits' used by the ReM\_FPGA's firmware to administrate the 'read back' from PPrASICS. VME can only read those bits. The 'flag-bits' are the four spare bits on each SRAM word (bit#32-35).

- The operational status of Phos4 chips on MCMs (feedback to Delay-Lock-Loop alive) is held at **0x7FFEFC**.

- A set of eight registers (> 0x7FFF00) is defined for quick-loading of parameters used for the conditioning of analog input signals. Note, that the same values can be accessed on a channel-by-channel basis as laid out in the MCM-related registers.

- A register (at address **0x7FFF80**) marks channels, from whose discriminator a 'Trigger L1-Accept' can be derived and fed into an 'OR' to trigger the module locally.

- Another register (0x7FFF84) allows to generate a set of 'pseudo-protocol' pulses internally for technical purposes.

- VME can read the ReM\_FPGA firmware version at **0x7FFFD0**.

- Registers of the kind 'Control/ Status' common to the PPM as module-entity are allocated to addresses ≥ 0x7FFFD4.

31

Figure 23: The PPM as seen from VME.

The module is supervised by a VME bus-master, the CPU in the crate. Registers in the CPLDs controlling bus-traffic and firmware-loading provide the means to configure the PPM into the desired operational mode. These registers are listed in the table below with their 'absolute' allocation in address-space of VME.

The programming package HDMC (Hardware-Diagnostic-Monitoring-Control) uses addresses for 32-bit words to access module-level registers. Those addresses are also listed in the tables below. Daughterboards on the PPM are 'sub-modules' (sub-classes in HDMC). The corresponding hardware-items are PPrMCMs (as well as PPrASICs thereon) and the TTCdecoder. Their register-addresses are defined as 'byte-address' and used as incremental address upon the sub-modules base-address.

| Register Name      | Size<br>/ byte | Byte<br>ADDRESS | Location  | Register<br>Type | Word32<br>ADDRESS | Register<br>Definition | Description                                             | Acc.  |

|--------------------|----------------|-----------------|-----------|------------------|-------------------|------------------------|---------------------------------------------------------|-------|

|                    | J              |                 |           | J1               | (HDMC)            |                        |                                                         |       |

| CPLD Registers     |                | abs. Address    |           |                  |                   |                        |                                                         |       |

| Module_ID          | 4              | 0x000000        | VME_CPLD  | ModReg32         | 0x000000          | PPM.Base               | Birth-certificate of Module                             | R     |

| VME_Config         | 4              | 0x100000        | VME_CPLD  | ModReg32         | 0x040000          | PPM.VMEConf            | VME Configuration                                       | R/W   |

| VME_Status         | 4              | 0x110000        | VME_CPLD  | ModReg32         | 0x044000          | PPM.VMEStat            | VME Status                                              | R/W   |

| FlashRAM_Addr      | 4              | 0x010000        | FLSH_CPLD | ModReg32         | 0x004000          | PPM.FRAddr             | FlashRAM address                                        | R/W   |

| FlashRAM_Data      | 1              | 0x020003        | FLSH_CPLD | ModReg32         | 0x008000          | PPM.FRDat              | FlashRAM Data                                           | R/W   |

| FlashRAM_Reset     | 1              | 0x030003        | FLSH_CPLD | ModReg32         | 0x00C000          | PPM.FRRes              | FlashRAM Reset                                          | R/W   |