# TTC-VMEbus INTERFACE TTCvi - MkII

Module Identification: EP 680-1128-050-C

RD12 Project

Ph. Farthouat, P. Gällnö CERN EP - ATE

| -       |               |

|---------|---------------|

| Rev 0   | Aug. 1995     |

| Rev 0.1 | 20 Sept. 1995 |

| Rev 1.0 | 25 Oct. 1995  |

| Rev 1.1 | 27 Nov. 1995  |

| Rev 1.2 | 19 Jun. 1996  |

| Rev 1.3 | 18 Jul 1996   |

| Rev 1.4 | April 1997    |

| Rev 1.5 | Nov. 1997     |

| Rev 1.6 | May 2000      |

|         |               |

| Introduction                                     | . 1  |

|--------------------------------------------------|------|

| New features in TTCvi MkII                       |      |

| Clock Inputs                                     |      |

| Trigger Inputs                                   |      |

| Test Trigger Random Generation                   |      |

| Calibration Trigger Generation                   |      |

| Orbit Input                                      |      |

| Inhibit<3.0> Signals                             |      |

| Generation of B Channel cycles                   |      |

| Short- and long-format asynchronous cycles       |      |

| Pre-loaded synchronous or asynchronous cycles    |      |

| Event Number/Orbit Count and Trigger Type cycle  |      |

| TTCvi Registers and VME Address Map              | 8    |

| Address Modifiers.                               |      |

| Short-format asynchronous cycles                 |      |

| Long-format asynchronous cycles                  |      |

| CSR1. Input selection and timing.                |      |

| CSR2. FIFO's status.                             |      |

| Software module reset generation                 |      |

| Software L1A generation                          |      |

| Software Event/Orbit Counter reset generation    |      |

| Inhibit<0>                                       |      |

| Inhibit<1>                                       |      |

| Inhibit<2>                                       |      |

| Inhibit<3>                                       |      |

| B-Go<0>                                          |      |

| B-Go<1>                                          |      |

| B-Go<1>                                          |      |

| B-Go<2>                                          |      |

| Event/Orbit Counter                              |      |

| TRIGWORD Register                                |      |

| B Channel Data for B-Go<0>                       |      |

| B Channel Data for B-Go<1>                       |      |

| B Channel Data for B-Go<2>                       |      |

| B Channel Data for B-Go<3>                       |      |

| Configuration - Identification EEPROM Mapping    |      |

| VME Address Map Summary                          | . 17 |

| 1 0                                              |      |

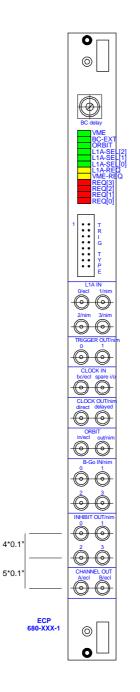

| TTCvi Front Panel<br>Front Panel Coaxial signals |      |

| Trigger Type Connector Pin-Out                   |      |

|                                                  |      |

| Front Panel Indicators                           |      |

| Front Panel Lay-out                              |      |

| Module Power Requirements                        |      |

|                                                  |      |

| Daughter Board Lay-out                           |      |

| Mother Board Lay-out                             |      |

| Adjusting Module Base Address                    | . 24 |

| Modifying Module Identification/Revision EEPROM  |      |

| Adjusting the clock delay                        |      |

| Use of the spare NIM front panel input/output    |      |

| Test Headers                                     |      |

| TESTPAD 1                                        |      |

| TESTPAD 2                                        |      |

| TESTPAD 3                                        |      |

| TESTPAD 4                                        |      |

| TESTPAD 5                                        |      |

| Appendix                                         |      |

| Programming modification note:                   | . 30 |

# **TTC-VMEbus INTERFACE**

### (TTCvi)

This note describes the revised version of the RD12 TTC-VMEbus interface (TTCvi - MkII) module, which interfaces the TTC system to the Central Trigger Processor (Global Trigger) and to the control processors or development workstations which generate commands and data to be transmitted to the front-end electronics controllers. The note is updated at intervals.

## Introduction

The TTCvi module is a key component of the RD12 TTC system described in **http://www.cern.ch/TTC/intro.html**. It delivers the A Channel and B Channel signals to the TTC transmitters for multiplexing, encoding, optical conversion and distribution to the TTCrx ASICs associated with the frontend electronics controllers. To minimise the possibility of configuration errors, the characteristics of the module and the signal routing which it controls are fully programmable from the VMEbus.

The TTC **A Channel** is used to transmit the Level-1 Accept (L1A) signal. The TTCvi incorporates a programmable L1A source selector and an internal trigger emulator for test purposes.

The TTC **B** Channel is used to transmit framed and formatted commands and data. These can be either:

- Short-format synchronous or asynchronous broadcast command/data cycles. If synchronous, the timing of these cycles relative to the LHC orbit is controlled precisely. They are used for the broadcasting of the bunch counter reset signals which control the phases of the TTCrx bunch counters, and for the transmission of other fast synchronous broadcast controls and test commands or data. These commands are deskewed in the TTCrx ASICs to compensate for individual differences in fibre propagation delay, electronics and detector delays and particle times-of-flight.

- Long-format asynchronous individually-addressed or broadcast command/data cycles. The timing of these cycles with respect to the LHC orbit is indeterminate and they are not individually deskewed in TTCrx ASICs. They are used for the transmission of parameters, test data, calibration data and non time-critical commands, such as channel masks, to the front-end electronics.

# New features in TTCvi MkII

Based on feedback from TTC users the design of the TTCvi module has been revised and the following improvements and modifications have been introduced:

- 1. It is now possible to select the internal counting of *either* the event triggers *or* the LHC orbit pulses. A bit in the Control Register-1 controls the selection.

- 2. The internal event/orbit-counter may be reset by a VMEbus generated function.

- 3. The address, sub-address, size bit and int/ext bit of the event/orbitcount/trig-type B-channel transfers are now fully programmable from the VMEbus.

- 4. The event/orbit-count/trig-type B-channel transfers may be disabled.

- 5. A feature to allow for the generation of a delayed calibration TRIGGER triggered by an external pulse on one of the B-Go inputs. The delay is programmable in the same way as the INHIBIT delay.

- 6. The BC division factor for the internal orbit pulse generation has been corrected. This factor was before 3565 and is now 3564.

- 7. Two indicator LED's has been added to show the activity on the A and B channels.

A summary of required changes to the driver software is found in the Appendix .

### **Clock Inputs**

The TTCvi module is normally driven by a 40.08 MHz clock signal which it receives from the TTC system, and which is phase-locked to the LHC clock (or to a local clock generator when that signal is not available). In order to allow compensation for different cable lengths between the TTCvi and the TTC encoder, the phase of the input clock can be adjusted by means of a rotary switch on the TTCvi. The delay value can be read through the TTCvi status register CSR1. This adjustment is made on installation of the module such that the A and B Channel data output signals from the TTCvi are delivered to the TTC encoder within the appropriate phase window. Once set up, it should not be altered unless the cable lengths between the TTCvi and the TTC encoder or clock source are changed.

If the external TTC clock source is removed from the front panel input of the TTCvi an internal 40.00 MHz clock is automatically selected in order to keep all the module internal logic working. A front panel indicator (**BC-EXT**) show which clock is running. The external clock input is marked **CLOCK IN bc/ecl** on the front panel and is  $50\Omega$  AC coupled and expecting ECL levels.

### **Trigger Inputs**

Although in normal running the trigger input to the module is the L1A signal provided by the Central Trigger Processor, the TTCvi allows three other trigger sources to be selected for test or calibration purposes without modifying the cabling. These sources are synchronised with the 40.08 MHz clock in the TTCvi.

The latency introduced by the module on the L1A coming from the CTP is minimised. In particular no resynchronisation of this signal with the clock is done.

Four front panel external inputs (including the one for the standard L1A input) are provided (L1A IN<0..3>), with programmable selection of the one in use. In addition, it is possible to generate a trigger by a VME access to a key address and an internal random trigger generator is provided for test purposes. An internal generator provides a L1A signal; the number of L1A per unit of time follows a Poisson distribution with a mean rate programmable from about 1 Hz to 100 kHz. The selected trigger is made available as two front panel NIM outputs (TRIGGER OUT<0..1>) for monitoring purposes. The trigger output pulse duration is 25 ns. An internal 24-bit event counter (which can be read and written through VME) counts the number of triggers sent.

The trigger source is selected by setting bits in the control register CSR1. The selection is shown on the front panel indicators **L1A-SEL(0..2**).

# **Test Trigger Random Generation**

The internal random signal generator has a period of 2.15  $10^9$  allowing L1A sequences to be generated for test purposes. A 16-bit "rate" register is used to define the average rate of trigger accepts generated. The average rate can be selected in the following values: 1 Hz, 100 Hz, 1 kHz, 5kHz, 10 kHz, 25 kHz, 50 kHz and 100 kHz. The rate is selected by setting a value in CSR1. Internal logic further limits the effective L1A rate by forcing a minimum dead time of 2 clock cycles between trigger accepts and by limiting to 16 the number of L1A sent within any interval of 16 µs.

# **Calibration Trigger Generation**

A calibration trigger pulse can be generated after a programmable delay. In order to start this calibration sequence the B-Go<2> front panel input is used and the CSR1, B-Go<2> mode and delay registers must be set up properly. The first position of the B-Go FIFO<2> should contain the calibration parameter and the FIFO<2> re-transmit function should be enabled if a repetitive operation is desired. In this mode the Inhibit<2> output reflects the B-Go<2> input.

# **Orbit Input**

The orbit signal is a pulse train of period 88.924  $\mu$ s, which is received from the TTCmi and distributed to the TTCvi and other components for the generation of signals which require to be synchronised to the LHC orbit. Adjustment of the phase of the orbit signal permits a global control of the timing of the entire TTC system relative to the LHC bunch structure. The LHC orbit pulses are negative-going, of width 1  $\mu$ s. They are received as a 50 $\Omega$  AC coupled ECL signal on the front panel connector marked **ORBIT in/ecl**.

To allow tests to be performed when the LHC orbit signal is not available, the TTCvi incorporates an internal pseudo orbit signal source obtained by dividing the 40.08 MHz clock by 3564. Selection between the front panel input of the LHC orbit signal and the internal source is made by setting a bit in the CSR1 register and the selected signal is made available as a front panel NIM output marked **ORBIT out/nim**. The presence of the external orbit signal may also be monitored on the front panel indicator **ORBIT**.

The orbit pulses may be optionally counted in the 24-bit event counter by setting the most significant bit in the CSR1 register. The orbit count may be sent to the TTCrx on each event.

## Inhibit<3..0> Signals

Four independently programmable timing signals, called Inhibit<3..0>, are generated within the TTCvi module for use in sending synchronous commands at controllable times relative to the LHC orbit.

At each Orbit signal all four inhibit timing generators are started. The orbit to inhibit delay is set by a 0 - 100  $\mu$ s programmable timer (12-bits) and the inhibit duration by a 0 - 6.4  $\mu$ s timer (8-bits). The timers are controlled by the selected clock, which means that the timing may be adjusted in steps of approximately 25 ns. Transmission of the associated synchronous command commences at the end of the Inhibit signal duration.

Each Inhibit signal is assigned a different priority level, such that Inhibit<0> has higher priority than Inhibit<1>, etc. When an Inhibit signal becomes active, the transmission of any command associated with a lower priority Inhibit is allowed to complete. Further such commands are held off until the higher priority one has been sent. Since the Inhibit signals are always programmed to have a duration exceeding that required for the transmission of even a long-format cycle (about 1.05  $\mu$ s), the higher priority signal is always transmitted at a determinate time relative to the LHC orbit.

The highest priority Inhibit <0> is used to trigger the transmission, during the LHC extractor gap, of a broadcast command containing the bunch counter reset. This signal, after deskewing in the individual receiver ASICs, is used to control the phase of the TTCrx bunch counters. The three other Inhibit signals are available for the generation of other synchronous commands including those required for triggering test pulse generators. All four Inhibit signals are made available as front panel NIM level outputs for monitoring purposes.(**INHIBIT OUT/nim<0..3>**)

Through appropriate pre-programming, one can ensure that synchronous commands at all priority levels are always sent at well defined times.

For asynchronous cycles, the highest priority is given to the broadcast of L1A number and trigger type, then VME mapped cycles and then B-Go<0> to B-Go<3>.

The Inhibit<2> output will, in calibration mode, reflect the B-Go<2> input after synchronisation to the BC clock.

### **Generation of B Channel cycles**

The TTCvi permits synchronous and asynchronous short- and long-format B Channel command/data cycles to be generated in a number of different ways:

#### Short- and long-format asynchronous cycles

Asynchronous cycles may be initiated by writing the required data (a single byte for short-format or two 16-bit words for long-format) to specified TTCvi VME addresses. Normally short-format cycles are used for broadcast commands or data while long-format cycles are used for individually addressed commands or data. However, a broadcast of 16 bits of data can be made with long-format cycles if TTCrx address 0 is chosen. The timing of these cycles is not synchronised with the LHC orbit.

#### Pre-loaded synchronous or asynchronous cycles

Four VME-addressable FIFO's are provided which may be pre-loaded with commands and data to be transmitted by B Channel cycles. For each of the four channels, the actual transmission of the pre-loaded information is initiated by a signal called B-Go<3..0> which can be generated either by a VME write to a key address or by an external signal applied to one of four front panel inputs. It is also possible to start the cycle transmission as soon as the FIFO is not empty. This last mode will facilitate the use of several TTCvi's in a single crate by reducing the VME access time: one can fill the FIFO in DMA mode (VME block transfers) and start the transmission as soon as the FIFO is not empty. The register CSR2 is used to monitor the status of the FIFO's. Sequences of B Channel cycles can be generated by loading the FIFO's with several parameters. In addition, a mode allows to load the FIFO once and to transmit always the same cycle(s) by resetting the read pointer of the FIFO as soon as it is empty. This is used for instance to transmit repetitive commands such as Bunch Counter Reset. The VME access to the FIFO is D32 only and supports block transfer mode.

A VME-addressable B-Go mode register associated with each of the four channels allows the selection of synchronous or asynchronous mode of either VME or front panel initiated B-Go cycles.

If synchronous mode is selected, the B-channel cycle is generated at the end of the Inhibit<i> signal. The cycle can be programmed to be either single or repetitive. In single mode, only one cycle is generated if a B-Go<i> has occurred before Inhibit<i>. In repetitive mode, the cycle is generated at the end of each Inhibit<i> signal (i.e. once per LHC orbit) and does not require

a B-Go<i> to occur. The bunch counter reset command, for example, is sent with this repetitive mode.

If asynchronous mode is selected, the B Channel cycle is generated only once each time the B-Go<i> signal occurs.

#### Event Number/Orbit Count and Trigger Type cycle

After each L1A is transmitted, the contents of the 24-bit event/orbit counter in the TTCvi is broadcast together with an 8-bit trigger type parameter, which is received from the Central Trigger Processor via a front panel connection. This broadcast, which is intended for check purposes, is made asynchronously and takes about 4.4  $\mu$ s if the B Channel is free. The following sub-addresses of the long B-Channel cycle are used:

- 0 Trigger type on the 8 data bits.

- 1 Event/Orbit Count <23..16> on the 8 data bits.

- 2 Event/Orbit Count <15..8> on the 8 data bits.

- 3 Event/Orbit Count <7..0> on the 8 data bits.

Internally, the event/orbit count and the trigger type are stored in FIFO's to avoid any losses due to the random time of arrival of L1A. The status of these FIFO's are available in the CSR1 register. The TTC address of this transfer is set by loading the *TRIGWORD Register*. If, however, the *size* bit is set to a '0' (= short frame transfers) this type of transfer is disabled.

## **TTCvi Registers and VME Address Map**

#### **Address Modifiers**

The TTCvi module is A24, A16 / D32, D16 and responds to the following Address Modifiers:

| Standard: | 39, 3A, 3D, 3E |                                     |

|-----------|----------------|-------------------------------------|

| Short:    | 29, 2D         |                                     |

| Block:    | 0F, 0B, 3B, 3F |                                     |

| Extended: | 09, 0A, 0D, 0E | (in order to respond to some CPU's) |

Four rotary switches are used to set the base address (A23 to A8).

#### Short-format asynchronous cycles

• **\$C4**: B Channel short-format asynchronous broadcast access.

| D7 to D0   |

|------------|

| 8b COMMAND |

#### Long-format asynchronous cycles

•  $C_2/C_0$ : B Channel long-format individually-addressed (or broadcast with TTCrx = 0) access.

E=0 accesses TTCrx internal registers. E=1 is for access to external subaddresses in the associated front-end electronics.

| D15 | D14 to D1      | D0 |

|-----|----------------|----|

| 1   | 14b TTCrx ADDR | Е  |

Address \$C2

| D15 to D8  | D7 to D0 |

|------------|----------|

| 8b SUBADDR | 8b DATA  |

Transmission starts after the second address (\$C2) has been loaded from VME if one uses D16 transfer. It is not necessary to reload the first address in order to access additional sub-addresses associated with the same TTCrx.

### CSR1. Input selection and timing.

• **\$80**: Clock, Trigger and Orbit signal selection. Read and Write word access.

| bit | R/W | Function                    | Comments                                |

|-----|-----|-----------------------------|-----------------------------------------|

| 15  | R/W | Event/Orbit Count Selection | '0' = Event Count, '1' = Orbit Count    |

| 14  | R/W | Random Trigger Rate MSB     | '7' = 100k, '6' = 50k, '5' = 25k        |

| 13  | R/W | Random Trigger Rate         | 4' = 10k, $3' = 5k$ , $2' = 1k$         |

| 12  | R/W | Random Trigger Rate LSB     | '1' = 100Hz, '0' = 1Hz                  |

| 11  | R   | BC delay MSB                | Read BC delay switch value              |

| 10  | R   | BC delay                    | 2 ns/step                               |

| 09  | R   | BC delay                    | (NB bits <1108> must inverted to        |

| 08  | R   | BC delay LSB                | reflect correct switch setting)         |

| 07  | R   | VME transfer pending        | if "1" a VME request is still pending   |

| 06  | W   | L1A FIFO reset              | if set to "1"                           |

| 05  | R   | L1A FIFO empty              | if "1"                                  |

| 04  | R   | L1A FIFO full               | if "1"                                  |

| 03  | R/W | Orbit signal select         | external ORBIT if set to "0"            |

| 02  | R/W | L1A trigger select MSB      | Random if 5, Calibr. if 6, Disable if 7 |

| 01  | R/W | L1A trigger select          | L1A<3> if 3, VME function if 4          |

| 00  | R/W | L1A trigger select LSB      | L1A<0> if 0, L1A<1> if 1, L1A<2> if 2   |

#### CSR2. FIFO's status.

• **\$82**: FIFO's flags and use Read and Write word access.

| bit | R/W | Function               | Comments                 |

|-----|-----|------------------------|--------------------------|

| 15  | W   | Reset B-Go FIFO 3      | if set to "1"            |

| 14  | W   | Reset B-Go FIFO 2      | if set to "1"            |

| 13  | W   | Reset B-Go FIFO 1      | if set to "1"            |

| 12  | W   | Reset B-Go FIFO 0      | if set to "1"            |

| 11  | R/W | Retransmit B-Go FIFO 3 | if set to "0" when EMPTY |

| 10  | R/W | Retransmit B-Go FIFO 2 | if set to "0" when EMPTY |

| 09  | R/W | Retransmit B-Go FIFO 1 | if set to "0" when EMPTY |

| 08  | R/W | Retransmit B-Go FIFO 0 | if set to "0" when EMPTY |

| 07  | R   | B-Go FIFO 3 FULL       | if "1"                   |

| 06  | R   | B-Go FIFO 3 EMPTY      | if "1"                   |

| 05  | R   | B-Go FIFO 2 FULL       | if "1"                   |

| 04  | R   | B-Go FIFO 2 EMPTY      | if "1"                   |

| 03  | R   | B-Go FIFO 1 FULL       | if "1"                   |

| 02  | R   | B-Go FIFO 1 EMPTY      | if "1"                   |

| 01  | R   | B-Go FIFO 0 FULL       | if "1"                   |

| 00  | R   | B-Go FIFO 0 EMPTY      | if "1"                   |

#### Software module reset generation

• **\$84**: a write word access to this address generates module reset. (data less function)

#### Software L1A generation

• **\$86**: a write word access to this address generates a L1A test trigger if bits <2..0> = \$4 in CSR1. (data less function)

#### Software Event/Orbit Counter reset generation

• **\$8C**: a write word access to this address generates an Event/Orbit Counter reset. (data less function)

#### Inhibit<0>

• **\$92**: Inhibit<0> delay in number of clock cycles Read and Write word access.

| D11 to D0 |  |

|-----------|--|

| Delay     |  |

• **\$94**: Inhibit<0> duration in number of clock cycles Read and Write word access.

| D7 to D0 |

|----------|

| Duration |

|          |

If Duration is equal to zero, there is no Inhibit<0> signal.

#### Inhibit<1>

• **\$9A**: Inhibit<1> delay in number of clock cycles Read and Write word access.

|       | D11 to D0 |  |

|-------|-----------|--|

| Delay |           |  |

|       |           |  |

• **\$9C**: Inhibit<1> duration in number of clock cycles Read and Write word access.

| D7 to D0 |  |

|----------|--|

| Duration |  |

If Duration is equal to zero, there is no Inhibit<1> signal.

#### Inhibit<2>

• **\$A2**: Inhibit<2> delay in number of clock cycles Read and Write word access.

| D11 to D0 |  |  |  |  |

|-----------|--|--|--|--|

| Delay     |  |  |  |  |

• **\$A4**: Inhibit<2> duration in number of clock cycles Read and Write word access.

| D7 to D0 |  |

|----------|--|

| Duration |  |

If Duration is equal to zero, there is no Inhibit<2> signal.

#### Inhibit<3>

• **\$AA**: Inhibit<3> delay in number of clock cycles Read and Write word access.

| D11 to D0 |  |  |  |  |  |

|-----------|--|--|--|--|--|

| Delay     |  |  |  |  |  |

• **\$AC**: Inhibit<3> duration in number of clock cycles Read and Write word access.

| D7 to D0 |  |

|----------|--|

| Duration |  |

If Duration is equal to zero, there is no Inhibit<3> signal.

#### B-Go<0>

• **\$90**: mode selection for B-Go<0> Read and Write word access.

| D4     | D3   |     | D2              | D1          | D0              |

|--------|------|-----|-----------------|-------------|-----------------|

| '0'    | FIFO |     | Single          | Sync        | Enable          |

|        |      |     |                 |             |                 |

| Enable | 0    | Fre | ont panel inpu  | t enable    |                 |

|        | 1    | Fre | ont panel inpu  | t disable   |                 |

| Sync   | 0    | Sy  | nchronous cy    | cle         |                 |

|        | 1    | As  | ynchronous c    | ycle        |                 |

| Single | 0    | Sir | ngle mode       |             |                 |

|        | 1    | Re  | petitive mode   |             |                 |

| FIFO   | 0    | Sta | art cycle as so | on as FIFO< | 0> is not empty |

|        | 1    | Do  | n't look at FII | FO status   |                 |

| '0'    | 0    | Мı  | ust always be   | set to '0'  |                 |

• **\$96**: a Write word access to this address generates a B-Go<0> signal (if Enable is equal to 1).

### **B-Go<1>**

• **\$98**: mode selection for B-Go<1> Read and Write word access.

| D4  | D3   | D2     | D1   | D0      |

|-----|------|--------|------|---------|

| '0' | FIFO | Single | Sync | Enable  |

| 0   | 1110 | Single | Byne | Lindole |

| Enable | 0 | Front panel input enable                    |

|--------|---|---------------------------------------------|

|        | 1 | Front panel input disable                   |

| Sync   | 0 | Synchronous cycle                           |

|        | 1 | Asynchronous cycle                          |

| Single | 0 | Single mode                                 |

|        | 1 | Repetitive mode                             |

| FIFO   | 0 | Start cycle as soon as FIFO<1> is not empty |

|        | 1 | Don't look at FIFO status                   |

| '0'    | 0 | Must always be set to '0'                   |

• **\$9E**: a Write word access to this address generates a B-Go<1> signal (if Enable is equal to 1).

#### B-Go<2>

• **\$A0**: mode selection for B-Go<2> Read and Write word access.

| D4          | D3  |     | D2              | D1          | D0              |

|-------------|-----|-----|-----------------|-------------|-----------------|

| Calibration | FIF | С   | Single          | Sync        | Enable          |

|             |     |     |                 |             |                 |

| Enable      | 0   | Fre | ont panel inpu  | t enable    |                 |

|             | 1   | Fre | ont panel inpu  | t disable   |                 |

| Sync        | 0   | Sy  | nchronous cy    | cle         |                 |

|             | 1   | As  | ynchronous c    | ycle        |                 |

| Single      | 0   | Sir | igle mode       |             |                 |

|             | 1   | Re  | petitive mode   |             |                 |

| FIFO        | 0   | Sta | rt cycle as so  | on as FIFO< | 2> is not empty |

|             | 1   | Do  | n't look at FII | FO status   |                 |

| Calibration | 0   | Ba  | sic operation   | mode        |                 |

|             | 1   | Ca  | libration mod   | e           |                 |

• **\$A6**: a Write word access to this address generates a B-Go<2> signal (if Enable is equal to 1).

#### B-Go<3>

• **\$A8**: mode selection for B-Go<3> Read and Write word access.

| D4     | D3   |     | D2             | D1          | D0              |

|--------|------|-----|----------------|-------------|-----------------|

| '0'    | FIFO | )   | Single         | Sync        | Enable          |

|        |      |     |                |             |                 |

| Enable | 0    | Fre | ont panel inpu | ıt enable   |                 |

|        | 1    | Fre | ont panel inpu | ıt disable  |                 |

| Sync   | 0    | Syı | nchronous cy   | cle         |                 |

|        | 1    | As  | ynchronous c   | ycle        |                 |

| Single | 0    | Sin | gle mode       |             |                 |

|        | 1    | Re  | petitive mode  | 2           |                 |

| FIFO   | 0    | Sta | rt cycle as so | on as FIFO< | 3> is not empty |

|        | 1    | Do  | n't look at FI | FO status   |                 |

| '0'    | 0    | Мı  | ıst always be  | set to '0'  |                 |

• **\$AE**: a Write word access to this address generates a B-Go<3> signal (if Enable is equal to 1).

#### **Event/Orbit Counter**

• **\$88** / **\$8A**: Event/Orbit Counter. Read and Write word access.

|--|

| D7 to D0          |  |

|-------------------|--|

| L1A# bit 23 to 16 |  |

| Address \$8A     |  |

|------------------|--|

| D15 to D0        |  |

| L1A# bit 15 to 0 |  |

#### **TRIGWORD Register**

• **\$C8** / **\$CA**: TRIGWORD Address/Sub-address Register. Read and Write word access.

Address \$C8 (Address bits)

| 4  | 3  | 2            | 1                           | 0                                   |

|----|----|--------------|-----------------------------|-------------------------------------|

| ad | ad | ad           | ad                          | ad                                  |

| 4  | 3  | 2            | 1                           | 0                                   |

| 11 | 12 | 13           | 14                          | 15                                  |

|    | 4  | ad ad<br>4 3 | ad ad ad   4 3 2   11 12 13 | ad ad ad ad   4 3 2 1   11 12 13 14 |

Address \$CA (Size, int/ext and sub-address bits)

|               |     | 1 1 47 4 |     | φ Οι Ι | (~120, |     |     |     |     | 0100 | /   |     |     |     |

|---------------|-----|----------|-----|--------|--------|-----|-----|-----|-----|------|-----|-----|-----|-----|

| VME bit no    | 13  | 12       | 11  | 10     | 9      | 8   | 7   | 6   | 5   | 4    | 3   | 2   | 1   | 0   |

| usage         | n/u | n/u      | n/u | n/u    | size   | Î/e | sad | sad | sad | sad  | sad | sad | n/u | n/u |

| Sub-addr. bit |     |          |     |        | -      | -   | 7   | 6   | 5   | 4    | 3   | 2   | 1   | 0   |

| serial bit    |     |          |     |        | 1      | 16  | 18  | 19  | 20  | 21   | 22  | 23  | 24  | 25  |

N.B. Bits [13..10] and [1..0] are not programmable and will read '0'. Setting size bit to '0' (short frames) will inhibit the Event/Orbit Counter/Trig-type transfers following a trigger.

#### **B** Channel Data for B-Go<0>

• **\$B0**: B Channel data associated to B-Go<0>. VME Write LONGWORD access.

If a long-format TTC cycle is used, 32 bits are necessary with the following mapping:

|     | Address \$B0   |     |            |          |

|-----|----------------|-----|------------|----------|

| D31 | D30 to D17     | D16 | D15 to D8  | D7 to D0 |

| 1   | 14b TTCrx ADDR | Е   | 8b SUBADDR | 8b DATA  |

If a short-format cycle is used, 9 bits are necessary with the following mapping:

Address \$B0

| D31 | D30 to D23 | D22 to D0 |  |  |  |  |  |

|-----|------------|-----------|--|--|--|--|--|

| 0   | 8b COMMAND | Х         |  |  |  |  |  |

These registers are FIFO's (256 depth), which may be pre-loaded with mixed format sequences of B Channel cycles.

#### **B** Channel Data for B-Go<1>

• **\$B4**: B Channel data associated to B-Go<1>. VME Write LONGWORD access.

If a long-format TTC cycle is used, 32 bits are necessary with the following mapping:

|     | Address \$B4   |     |            |          |

|-----|----------------|-----|------------|----------|

| D31 | D30 to D17     | D16 | D15 to D8  | D7 to D0 |

| 1   | 14b TTCrx ADDR | E   | 8b SUBADDR | 8b DATA  |

If a short-format cycle is used, 9 bits are necessary with the following mapping:

Address \$B4

| D31 | D30 to D23 | D22 to D0 |

|-----|------------|-----------|

| 0   | 8b COMMAND | Х         |

These registers are FIFO's (256 depth), which may be pre-loaded with mixed format sequences of B Channel cycles.

#### **B** Channel Data for B-Go<2>

• **\$B8**: B Channel data associated to B-Go<2>. VME Write LONGWORD access.

If a long-format TTC cycle is used, 32 bits are necessary with the following mapping:

|     | Address \$B8   |     |            |          |

|-----|----------------|-----|------------|----------|

| D31 | D30 to D17     | D16 | D15 to D8  | D7 to D0 |

| 1   | 14b TTCrx ADDR | E   | 8b SUBADDR | 8b DATA  |

If a short-format cycle is used, 9 bits are necessary with the following mapping:

Address \$B8

| 11001000 | <b>420</b> |           |

|----------|------------|-----------|

| D31      | D30 to D23 | D22 to D0 |

| 0        | 8b COMMAND | Х         |

These registers are FIFO's (256 depth), which may be pre-loaded with mixed format sequences of B Channel cycles.

#### **B** Channel Data for B-Go<3>

• **\$BC**: B Channel data associated to B-Go<3>. VME Write LONGWORD access.

If a long-format TTC cycle is used, 32 bits are necessary with the following mapping:

|     | Address \$BC   |     |            |          |

|-----|----------------|-----|------------|----------|

| D31 | D30 to D17     | D16 | D15 to D8  | D7 to D0 |

| 1   | 14b TTCrx ADDR | Е   | 8b SUBADDR | 8b DATA  |

If a short-format cycle is used, 9 bits are necessary with the following mapping:

Address \$BC

| D31 | D30 to D23 | D22 to D0 |

|-----|------------|-----------|

| 0   | 8b COMMAND | Х         |

These registers are FIFO's (256 depth), which may be pre-loaded with mixed format sequences of B Channel cycles.

### **Configuration - Identification EEPROM Mapping**

• **\$00**: Read Only 16 bit words, from address \$26 to \$4E. Write access if strap ST500 is fitted. Successive write cycles should be >5ms apart to allow for EEPROM write access time.

| VM     | E Address Of | fsets of 32 bit | words  |                        |        |

|--------|--------------|-----------------|--------|------------------------|--------|

| MSBYTE |              |                 | LSBYTE |                        |        |

| 31 24  | 23 16        | 15 8            | 7 0    |                        |        |

| 20     | 21           | 22              | 23     |                        |        |

| 24     | 25           | 26              | 27     | Manufacturer ID (CERN) | MSBYTE |

| 28     | 29           | 2A              | 2B     | Manufacturer ID (CERN) |        |

| 2C     | 2D           | 2E              | 2F     | Manufacturer ID (CERN) | LSBYTE |

| 30     | 31           | 32              | 33     | Board ID / Serial No.  | MSBYTE |

| 34     | 35           | 36              | 37     | Board ID / Serial No.  |        |

| 38     | 39           | 3A              | 3B     | Board ID / Serial No.  |        |

| 3C     | 3D           | 3E              | 3F     | Board ID / Serial No.  |        |

| 40     | 41           | 42              | 43     | Board Revision No.     | MSBYTE |

| 44     | 45           | 46              | 47     | Board Revision No.     |        |

| 48     | 49           | 4A              | 4B     | Board Revision No.     |        |

| 4C     | 4D           | 4E              | 4F     | Board Revision No.     | LSBYTE |

The Manufacturer's Board Identification is on request supplied by IEEE (See ANSI/VITA 1-1994 VMEbus Specs. Appendix C)

### VME Address Map Summary

| Addr.    | Register                | R/W   | Access         | Remarks                           |

|----------|-------------------------|-------|----------------|-----------------------------------|

| Offset   | TRICWORD LOW            | DAV   | <b>X</b> 7 1 4 | TTO ask a three stars a first and |

| CA       | TRIGWORD LSW            | R/W   | W 14           | TTC sub-address/size/int-ext      |

| C8       | TRIGWORD MSW            | R/W   | W 14           | TTC address                       |

| C6<br>C4 | Short VME evolu         | W     | W/ O           |                                   |

|          | Short VMEcycle          |       | W 8            | DATA<70>                          |

| C2       | Long VMEcycle LSW       | W     | LW/W           |                                   |

| C0       | Long VMEcycle MSW       | W     | LW/W           |                                   |

| BE       | B-Go<3> Param. LSW      | W     | LW/W           | B-Go FIFO <3>                     |

| BC       | B-Go<3> Param. MSW      | W     | LW/W           | B-Go FIFO <3>                     |

| BA       | B-Go<2> Param. LSW      | W     | LW/W           | B-Go FIFO <2>                     |

| B8       | B-Go<2> Param. MSW      | W     | LW/W           | B-Go FIFO <2>                     |

| B6       | B-Go<1> Param. LSW      | W     | LW/W           | B-Go FIFO <1>                     |

| B4       | B-Go<1> Param. MSW      | W     | LW/W           | B-Go FIFO <1>                     |

| B2       | B-Go<0> Param. LSW      | W     | LW/W           | B-Go FIFO <0>                     |

| B0       | B-Go<0> Param. MSW      | W     | LW/W           | B-Go FIFO <0>                     |

| AE       | B-Go<3> SW-Go           | W     | W              | data-less function                |

| AC       | Inh<3> Duration         | R/W   | W 8            | DATA<70>                          |

| AA       | Inh<3> Delay            | R/W   | W 12           | DATA<110>                         |

| A8       | B-Go<3> Mode            | R/W   | W 4            | DATA<30> see bit map              |

| A6       | B-Go<2> SW-Go           | W     | W -            | data-less function                |

| A4       | Inh<2> Duration         | R/W   | W 8            | DATA<70>                          |

| A2       | Inh<2> Delay            | R/W   | W 12           | DATA<110>                         |

| A0       | B-Go<2> Mode            | R/W   | W 4            | DATA<30> see bit map              |

| 9E       | B-Go<1>SW-Go            | W     | W -            | data-less function                |

| 9C       | Inh<1> Duration         | R/W   | W 8            | DATA<70>                          |

| 9A       | Inh<1> Delay            | R/W   | W 12           | DATA<110>                         |

| 98       | B-Go<1> Mode            | R/W   | W 4            | DATA<30> see bit map              |

| 96       | B-Go<0> SW-Go           | W     | W -            | data-less function                |

| 94       | Inh<0> Duration         | R/W   | W 8            | DATA<70>                          |

| 92       | Inh<0> Delay            | R/W   | W 12           | DATA<110>                         |

| 90       | B-Go<0> Mode            | R/W   | W 4            | DATA<30> see bit map              |

| 8E       |                         |       |                |                                   |

| 8C       | Event/Orbit-Count Reset |       |                |                                   |

| 8A       | Event/Orbit-Count LSW   | R/W   | W 16           |                                   |

| 88       | Event/Orbit-Count MSW   | R/W   | W 8            |                                   |

| 86       | SW-L1A                  | W     | W -            | data-less function                |

| 84       | SW-RST                  | W     | W -            | data-less function                |

| 82       | CSR2                    | R/W   | W 16           | see bit map                       |

| 80       | CSR1                    | R/W   | W 16           | see bit map                       |

| 00       | Configuration EEPROM    | R/(W) | W 8            | LSBytes in every Long Word.       |

|          | 6 ·····                 |       |                | See specs.                        |

# **TTCvi Front Panel**

### Front Panel Coaxial signals

The following signals are available on the front panel:

| Name                  | Description                     | Standard        |

|-----------------------|---------------------------------|-----------------|

| L1A IN 0/ecl          | L1A input from CTP              | ECL active low  |

| L1A IN 1/nim          | User L1A Input                  | NIM             |

| L1A IN 2/nim          | User L1A Input                  | NIM             |

| L1A IN 3/nim          | User L1A Input                  | NIM             |

| TRIGGER OUT/nim 0     | Selected L1A Output             | NIM             |

| TRIGGER OUT/nim 1     | Selected L1A Output             | NIM             |

| CLOCK IN bc/ecl       | Input clock / Bunch Crossings   | ECL             |

| spare i/o             | Configurable spare i/o          | NIM             |

| CLOCK OUT/nim direct  | Selected Clock Output           | NIM             |

| CLOCK OUT/nim delayed | Delayed Selected Clock Output   | NIM             |

| ORBIT in/ecl          | Orbit Input                     | ECL             |

| ORBIT out/nim         | Selected Orbit Output           | NIM             |

| B-Go IN/nim 0         | B-Go 0 Input                    | NIM             |

| B-Go IN/nim 1         | B-Go 1 Input                    | NIM             |

| B-Go IN/nim 2         | B-Go 2 Input                    | NIM             |

| B-Go IN/nim 3         | B-Go 3 Input                    | NIM             |

| INHIBIT OUT/nim 0     | Inhibit 0 Output                | NIM             |

| INHIBIT OUT/nim 1     | Inhibit 1 Output                | NIM             |

| INHIBIT OUT/nim 2     | Inhibit 2 Output / (B-Go 2 out) | NIM             |

| INHIBIT OUT/nim 3     | Inhibit 3 Output                | NIM             |

| CHANNEL OUT A/ecl     | A-Channel Output                | ECL active high |

| CHANNEL OUT B/ecl     | B-Channel Output                | ECL active high |

### **Trigger Type Connector Pin-Out**

This male connector has 2 x 8 pins mounted with the pin 1 at the top left corner. A mating female plug would be 3M/3452-6600 (SCEM 09.55.03.316.4). The signal levels are of differential ECL type, where the odd pins are true high and even pins true low. Each signal pair is terminated with a  $120 \Omega$  resistor.

| SIGNAL        | PIN | PIN | SIGNAL        |

|---------------|-----|-----|---------------|

| D<0> positive | 1   | 2   | D<0> negative |

| D<1> positive | 3   | 4   | D<1> negative |

| D<2> positive | 5   | 6   | D<2> negative |

| D<3> positive | 7   | 8   | D<3> negative |

| D<4> positive | 9   | 10  | D<4> negative |

| D<5> positive | 11  | 12  | D<5> negative |

| D<6> positive | 13  | 14  | D<6> negative |

| D<7> positive | 15  | 16  | D<7> negative |

#### **Front Panel Indicators**

| LED        | Colour | Show Function                                    |

|------------|--------|--------------------------------------------------|

| VME        | green  | Successful VME access                            |

| BC-EXT     | green  | External clock connected and running             |

| ORBIT      | green  | External Orbit input selected                    |

| L1A-SEL(2) | green  | L1A trigger source selection, as follows:        |

| L1A-SEL(1) | green  | L1A<0> if 0, L1A<1> if 1, L1A<2> if 2,           |

| L1A-SEL(0) | green  | L1A<3> if 3, VME function if 4, Random if 5      |

| L1A-REQ    | yellow | request to send Event Count & Trigger Type       |

| VME-REQ    | yellow | request to send long or short asynchronous cycle |

| REQ(3)     | red    | request to send B-Go<3> associated cycle         |

| REQ(2)     | red    | request to send B-Go<2> associated cycle         |

| REQ(1)     | red    | request to send B-Go<1> associated cycle         |

| REQ(0)     | red    | request to send B-Go<0> associated cycle         |

| A-CH       | yellow | A channel activity                               |

| B-CH       | yellow | B channel activity                               |

#### **Front Panel Lay-out**

# **Module Power Requirements**

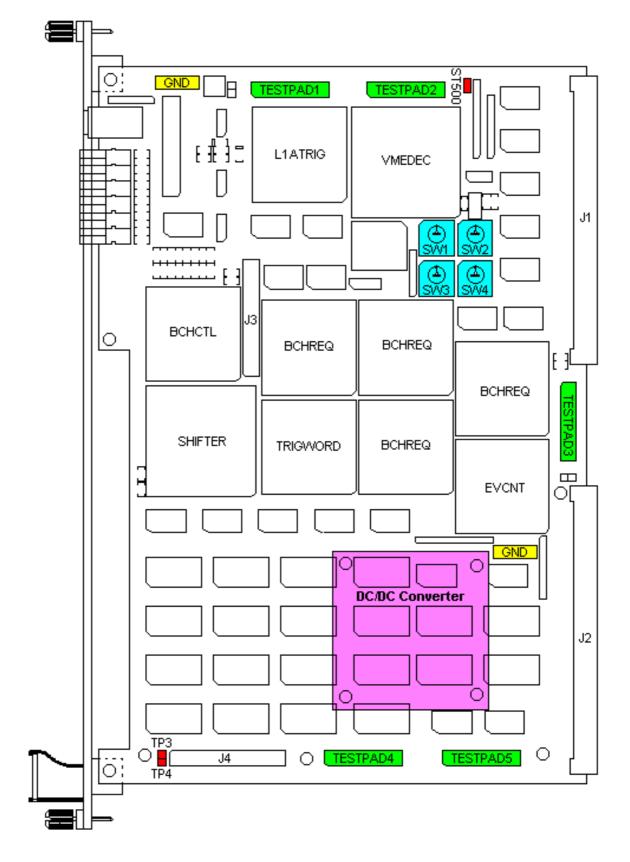

This module requires only a +5 V supply, with a consumption of about 5 A. An on-board DC-DC converter supplies the necessary -5 V for the NIM and ECL logic.

# **Module Board Lay-out and Configuration**

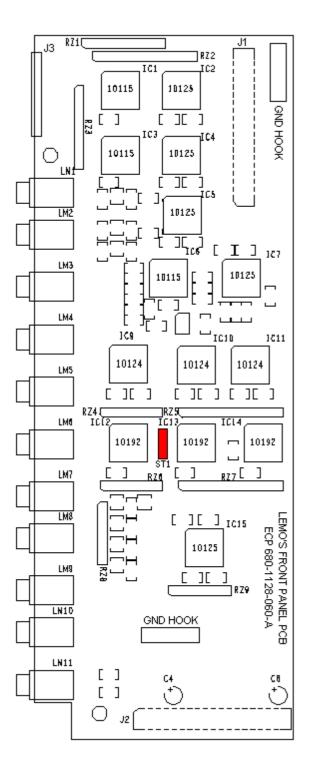

### **Daughter Board Lay-out**

#### Mother Board Lay-out

#### **Adjusting Module Base Address**

This is done by setting the hexadecimal switches SW[1..4]:

| SW1: | VME Address bits <2320> |

|------|-------------------------|

| SW2: | VME Address bits <1916> |

| SW3: | VME Address bits <1512> |

| SW4: | VME Address bits <1108> |

#### Modifying Module Identification/Revision EEPROM

In principle this is done once before shipping the module to the user. If however a modification is needed the following procedure should be respected:

- 1. Insert a mini-jumper across the strap ST500 on the mother board.

- 2. Write16 bit words, from address \$26 to \$4E where the byte D<7..0> should contain the desired information. See table on page 17

- 3. Consecutive write cycles to this EEPROM should be spaced > 5 ms apart, in order to respect the memory write access time.

- 4. Read back data and check.

- 5. Remove the mini-jumper.

#### Adjusting the clock delay

The phase between the 40.08 MHz clock (**CLOCK IN bc/ecl**) and the outgoing A and B Channel Out, (with the exception; if the A channel is derived from the **L1A<0>** input), may be adjusted with the front panel **BC DELAY** switch. Each of the 15 positions (> 0) of the switch corresponds to an additional delay of 2 ns. The switch setting may be read by the VME from CSR1. (N.B. invert CSR1 data bits <8..11> for correct reading!)

# The A and B Channel interconnecting patch cables must always be of the <u>same</u> length.

#### **TUNING PROCEDURE 1:**

(When using Encoder Units in the TTCmi, Mini-Crates or High-Power Transmitter Crate)

- 1. Connect the TTCvi **A/ecl CHANNEL OUT** output to the corresponding Transmitter Encoder input by using a Y-adaptor.

- 2. Connect the **CLOCK IN bc/ecl** input to the clock source (TTCcf output for the TTCmi, Clock Generator output for Minicrates or High-Power Transmitter Crates). Check that the TTCvi **BC\_EXT** indicator is lit.

- Set the TTCvi trigger mode (= 5) to random at the highest rate (100 kHz) and disable the event/orbit/trigger-type transfers. This should light up the A-Ch yellow TTCvi indicator and the A/ecl CHANNEL OUT output should now carry 25 ns long trigger pulses.

- 4. With an oscilloscope look at the Channel-A input of the Transmitter Encoder Module in respect to the 40.08 MHz square wave timing reference signal at the auxiliary Sync output of the Encoder Module.

- 5. Adjust the TTCvi BC delay switch such that the transition edges of the Channel-A pulses occur 4 ns  $\pm$ 4 ns after the rising or falling transitions of the Sync signal.

#### **TUNING PROCEDURE 2:**

(When using a TTCvx Module)

- 1. Connect the TTCvi A/ecl CHANNEL OUT output to the TTCvx A/ecl CHANNEL IN input via a Y-adapter.

- 2. Connect, via a Y-adapter, one of the **TTCvx CLOCK OUT/ecl** outputs to the TTCvi **CLOCK IN bc/ecl** input. Check that the BC\_EXT indicator is lit on the TTCvi. The TTCvx internal clock may be used.

- Set the TTCvi trigger mode (= 5) to random at the highest rate (100 kHz) and disable the event/orbit/trigger-type transfers. This should light up the TTCvi A-Ch yellow indicator and the A/ecl CHANNEL OUT output should now carry 25 ns long trigger pulses.

- 4. With an oscilloscope look at the TTCvx Channel-A input in respect to the clock output.

- 5. Adjust the TTCvi BC delay switch such that the rising edges of the Channel-A pulses occur within 4 ns before to 2 ns after the rising edges of the clock signal.

- 6. Setting the delay switch in position 2 and using 1 ns long interconnecting cables for the clock and the A and B channels corresponds to the above mentioned timing criteria.

### TUNING PROCEDURE WHEN USING AN EXTERNAL LIA TRIGGER SURCE: (This applies to both procedures mentioned above)

- 1. Follow the points in the relevant procedure above and <u>leave</u> the TTCvi BC delay switch in the adjusted position.

- 2. Set trigger mode (= 0) to select external low latency triggers.

- 3. Connect the TTCvi L1A IN 0/ecl input to an external trigger source. (active low signal)

- 4. Adjust the duration of the external trigger pulse to be  $20 \pm 3$  ns.

- 5. Adjust, by using an <u>external</u> delay unit, the relative position of the external trigger pulse to correspond to the timing criteria in the above procedures 1 or 2.

#### Use of the spare NIM front panel input/output

It is possible to use this spare *LEMO* socket to either getting external access to a TTCvi internal signal or having an external signal for internal control or monitoring purposes.

#### **INPUT:**

- 1. Put a mini-jumper in the lower position of strap ST1 on the daughter board.

- 2. On the mother board: connect a wire from the test point TP4 to the destination signal point.

#### **OUTPUT**:

- 1. Put a mini-jumper in the upper position of strap ST1 on the daughter board.

- 2. On the mother board: connect a wire from the test point TP3 to desired source signal.

# **Test Headers**

There are five Test Headers (TESTPAD[1..5] mounted on the TTCvi mother board to be used for test and debugging purposes. The test headers fit the Hewlett Packard 100 k $\Omega$  Termination Adapter (part no. 01650-90920). A suitable Logic State Analyser is the HP 16500 series, for which a number of acquisition set-ups already exist.

### **TESTPAD 1**

L1A, Event Number FIFO related signals.

| SIGNAL-NAME          | PIN | POD |

|----------------------|-----|-----|

| NC                   | 1   |     |

| NC                   | 2   |     |

| BCD2                 | 3   | CLK |

| BCD2                 | 4   | D15 |

| from tp2 (spare pin) | 5   | D14 |

| from tp1 (spare pin) | 6   | D13 |

| RDFIFO<3>            | 7   | D12 |

| RDFIFO<2>            | 8   | D11 |

| RDFIFO<1>            | 9   | D10 |

| RDFIFO<0>            | 10  | D09 |

| FIFO_L1A_EMPTY_L     | 11  | D08 |

| FIFO_EMPTY_L2        | 12  | D07 |

| FIFO_EMPTY_L1        | 13  | D06 |

| FIFO_EMPTY_L0        | 14  | D05 |

| WR_FIFO_L            | 15  | D04 |

| L1A_GRANT_L          | 16  | D03 |

| L1A_REQ_L            | 17  | D02 |

| L1A_OUT_L            | 18  | D01 |

| ORBIT_L              | 19  | D00 |

| GND                  | 20  | GND |

27

#### **TESTPAD 2**

VME associated signals.

| SIGNAL-NAME     | PIN | POD |

|-----------------|-----|-----|

| NC              | 1   |     |

| NC              | 2   |     |

| BCD2            | 3   | CLK |

| BCD2            | 4   | D15 |

| STATEVAR_C      | 5   | D14 |

| STATEVAR_B      | 6   | D13 |

| STATEVAR_A      | 7   | D12 |

| WR_FIFO_L0      | 8   | D11 |

| VME_GRANT_L     | 9   | D10 |

| VME_PEND_L      | 10  | D09 |

| VME_LONGL_CLK_H | 11  | D08 |

| VME_LONGH_CLK_H | 12  | D07 |

| DTACK_L         | 13  | D06 |

| WRITE_L         | 14  | D05 |

| LONGWORD_L      | 15  | D04 |

| LOADR_L         | 16  | D03 |

| HIADR_L         | 17  | D02 |

| AS_L            | 18  | D01 |

| DS0_L           | 19  | D00 |

| GND             | 20  | GND |

### **TESTPAD 3**

B-Go<0>, Inhibit<0>, B-channel related signals.

| SIGNAL-NAME          | PIN | POD |

|----------------------|-----|-----|

| NC                   | 1   |     |

| NC                   | 2   |     |

| BCD3                 | 3   | CLK |

| BCD3                 | 4   | D15 |

| from tp5 (spare pin) | 5   | D14 |

| from tp6 (spare pin) | 6   | D13 |

| B_GO_L<0>            | 7   | D12 |

| GRANT_L<0>           | 8   | D11 |

| BGO_REQ_L<1>         | 9   | D10 |

| BGO_REQ_L<0>         | 10  | D09 |

| INHIBIT_L<0>         | 11  | D08 |

| RESTRANSM_L<0>       | 12  | D07 |

| RD_FIFO_L<0>         | 13  | D06 |

| FIFO_EMPTY_L<0>      | 14  | D05 |

| SHIFT_L              | 15  | D04 |

| LOAD_L               | 16  | D03 |

| B_CHANNEL            | 17  | D02 |

| VME_LONG_OE_L        | 18  | D01 |

| L1A_GRANT_L          | 19  | D00 |

| GND                  | 20  | GND |

#### **TESTPAD 4**

| SIGNAL-NAME   | PIN | POD |

|---------------|-----|-----|

| NC            | 1   |     |

| NC            | 2   |     |

| NC            | 3   | CLK |

| B_CH DATA<16> | 4   | D15 |

| B_CH DATA<17> | 5   | D14 |

| B_CH DATA<18> | 6   | D13 |

| B_CH DATA<19> | 7   | D12 |

| B_CH DATA<20> | 8   | D11 |

| B_CH DATA<21> | 9   | D10 |

| B_CH DATA<22> | 10  | D09 |

| B_CH DATA<23> | 11  | D08 |

| B_CH DATA<24> | 12  | D07 |

| B_CH DATA<25> | 13  | D06 |

| B_CH DATA<26> | 14  | D05 |

| B_CH DATA<27> | 15  | D04 |

| B_CH DATA<28> | 16  | D03 |

| B_CH DATA<29> | 17  | D02 |

| B_CH DATA<30> | 18  | D01 |

| B_CH DATA<31> | 19  | D00 |

| GND           | 20  | GND |

B-Channel Parallel Data Bus bits <31..16>

### **TESTPAD 5**

B-Channel Parallel Data Bus bits <15..0>

| SIGNAL-NAME   | PIN | POD |

|---------------|-----|-----|

| NC            | 1   |     |

| NC            | 2   |     |

| NC            | 3   | CLK |

| B_CH DATA<0>  | 4   | D15 |

| B_CH DATA<1>  | 5   | D14 |

| B_CH DATA<2>  | 6   | D13 |

| B_CH DATA<3>  | 7   | D12 |

| B_CH DATA<4>  | 8   | D11 |

| B_CH DATA<5>  | 9   | D10 |

| B_CH DATA<6>  | 10  | D09 |

| B_CH DATA<7>  | 11  | D08 |

| B_CH DATA<8>  | 12  | D07 |

| B_CH DATA<9>  | 13  | D06 |

| B_CH DATA<10> | 14  | D05 |

| B_CH DATA<11> | 15  | D04 |

| B_CH DATA<12> | 16  | D03 |

| B_CH DATA<13> | 17  | D02 |

| B_CH DATA<14> | 18  | D01 |

| B_CH DATA<15> | 19  | D00 |

| GND           | 20  | GND |

# Appendix

#### **Programming modification note:**

The TTCvi MkII is close to fully software backward compatible with the existing TTCvi, i.e.

- 1. A spare bit in the CSR-1 (bit 15) is now used for event or orbit count selection.

- 2. A VME address (base address + offset=8C) is added for the event/orbit counter reset function.

- 3. The B-Go<3:0> Mode Registers have now 5 bits (previously 4) for setting the calibration mode. B-Go 3,1,0, bits 5 must be set to '0'.

- 4. The address, sub-address, size and int/ext bits of the event/orbit-counts and trig-type transfers are contained in two 16 bit VME registers at the base address + offset = C8/CA.