ANSI/VITA 1-1994

Approved as an American National Standard by

# American National Standard for VME64

Secretariat VMEbus International Trade Association

Approved April 10, 1995 American National Standards Institute, Inc.

American National Standard for VME64

Secretariat VMEbus International Trade Association

Approved April 10, 1995 American National Standards Institute, Inc.

#### Abstract

The VME64 specification establishes a framework for 8-, 16-, 32, and 64-bit parallel-bus computer architectures that can implement single and multiprocessor systems. It is based on the VMEbus specification released by the VMEbus Manufacturers Group (now VITA) in August of 1982. This bus includes the initial four basic subbuses: (1) data transfer bus, (2) priority interrupt bus, (3) arbitration bus, and (4) utility bus. Other architectures with other subbuses are possible within this VME framework.

The data transfer bus will support 8-, 16-, 32-, and 64-bit data transfers in multiplexed and non multiplexed form. The transfer protocols are asynchronous with varying degrees of handshaking dependent on the speeds required. The priority interrupt subsystem provides real-time interrupt services to the system. The allocation of bus mastership is performed by the arbitration subsystem which allows the implementation of several prioritization algorithms. The utility bus provides the system with power plus power-up and power-down synchronization. The mechanical specifications of boards, backplanes, subracks, and enclosures are based on IEC 297 and IEEE 1101.1 specifications, also known as the Eurocard form factor. Additional standards exist that can be used as sub-busses to this architecture for data transfers transactions, peripheral interfaces and intra-crate communications among compatible modules.

# American National Standard

Approval of an American National Standard requires verification by ANSI that the requirements for due process, consensus, and other criteria for approval have been met by the standards developer.

Consensus is established when, in the judgment of the ANSI Board of Standards Review, substantial agreement has been reached by directly and materially affected interests. Substantial agreement means much more than a simple majority, but not necessarily unanimity. Consensus requires that all views and objections be considered, and that a concerted effort be made toward their resolution.

The use of American National Standards is completely voluntary; their existence does not in any respect preclude anyone, whether they have approved the standards or not, from manufacturing, marketing, purchasing, or using products, processes, or procedures not conforming to the standards.

The American National Standards Institute does not develop standards and will in no circumstances give an interpretation of any American National Standard. Moreover, no person shall have the right or authority to issue an interpretation of an American National Standard in the name of the American National Standard Institute. Requests for interpretations should be addressed to the secretariat or sponsor whose name appears on the title page of this standard.

CAUTION NOTICE: This American National Standard may be revised or withdrawn at any time. The procedures of the American National Standards Institute require that action be taken periodically to reaffirm, revise, or withdraw this standard. Purchasers of American National Standards may receive current information on all standards by calling or writing the American National Standards Institute.

Published by

VMEbus International Trade Association 7825 E. Gelding Drive, Suite 104, Scottsdale, AZ 85260

Certain portions of this document are derived from portions of IEEE Std 1014-1987 IEEE Standard for a Versatile Backplane Bus: VMEbus, Copyright © 1987 by the Institute of Electrical and Electronics Engineers, Inc. and are adapted and reprinted with the permission of the IEEE. The IEEE disclaims any responsibility or liability resulting from the placement and use in this publication.

Copyright © 1995 by VMEbus International Trade Association All rights reserved.

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without prior written permission of the publisher.

NOTE: The user's attention is called to the possibility that compliance with this standard may require use of one or more inventions covered by patent rights.

By publication of this standard, no position is taken with respect to the validity of such claims or of any patent rights in connection therewith. The patent holders have, however, filed a statement of willingness to grant a license under these rights on reasonable and non-discriminatory terms and conditions to applicants desiring to obtain such a license for use of this standard. Details may be obtained from the publisher.

Printed in the United States of America - R1.13 ISBN 1-885731-02-7

### TABLE OF CONTENTS

| Abstract                                        |                                                                                    | X           |

|-------------------------------------------------|------------------------------------------------------------------------------------|-------------|

| Foreword                                        |                                                                                    | xi          |

| VMEbus Speci                                    | ification Geneology                                                                | xiii        |

| Introduction to<br>1.1 VMEbus S<br>1.2 VMEbus I | o the VMEbus Specification<br>Specification Objectives<br>nterface System Elements | 1<br>1<br>1 |

|                                                 | c Definitions<br>Terms Used to Describe the VMEbus Mechanical Structure            |             |

|                                                 |                                                                                    |             |

|                                                 | Terms Used to Describe the VMEbus Functional Structure                             |             |

|                                                 | Types of Cycles on the VMEbus<br>c VMEbus Structure                                |             |

|                                                 | Specification Diagrams                                                             |             |

| 1.4 Specificat                                  | ion Terminology                                                                    | 9           |

| 1.4.1 Sign                                      | al Line States                                                                     | 10          |

| 1.4.2 Use                                       | of the Asterisk (*)                                                                | 10          |

|                                                 | vord Numbering                                                                     |             |

|                                                 | pecification                                                                       |             |

|                                                 | rlocked Bus Signals                                                                |             |

| 1.5.2 Broa<br>1.6 System Ex                     | adcast Bus Signal<br>xamples and Explanations                                      | 12<br>12    |

| -                                               |                                                                                    |             |

| Data Transfer                                   | Bus                                                                                | 13          |

| 2.1.1 Enha                                      | ancements                                                                          | 13          |

| 2.2 Data-Trans                                  | sfer-Bus Lines                                                                     | 14          |

|                                                 | essing Lines                                                                       |             |

| 2.2.2 Addr                                      | ess Modifier Lines                                                                 | 20          |

|                                                 | Lines                                                                              |             |

| 2.2.4 Data                                      | Transfer Bus Control Lines                                                         | 26          |

| 2.2.4.1                                         | AS*                                                                                | 26          |

| 2.2.4.2                                         | DS0* and DS1*                                                                      | 26          |

| 2.2.4.3                                         | DTACK*                                                                             | 26          |

| 2.2.4.3                                         | .1 Rescinding DTACK*                                                               | 27          |

| 2.2.4.4                                         | BERR*                                                                              | 27          |

| 2.2.4.5                                         | WRITE*                                                                             | 27          |

| 2.2.4.6<br>2.3 DTB Modu                         | RETRY*<br>les Basic Description                                                    | 27<br>28    |

| 2.3.1 Master                                                       | 28  |

|--------------------------------------------------------------------|-----|

| 2.3.2 Slave                                                        | 32  |

| 2.3.3 Bus Timer                                                    | 34  |

| 2.3.4 Location Monitor                                             | 36  |

| 2.3.5 Addressing Phases and Modes                                  | 37  |

| 2.3.6 Basic Data Transfer Capabilities                             |     |

| 2.3.7 Block Transfer Capabilities                                  |     |

| 2.3.8 Read-Modify-Write Capability                                 |     |

| 2.3.9 Unaligned Transfer Capability                                |     |

| 2.3.10 Address-Only Capability                                     |     |

| 2.3.11 Lock Capability                                             |     |

| 2.3.12 Configuration ROM / Control And Status Register Capability  |     |

| 2.3.13 Retry Capability                                            |     |

| 2.3.14 Interaction Between DTB Functional Modules                  |     |

| 2.4 Typical Operation.                                             |     |

| 2.4.1 Typical Data-Transfer Cycles                                 |     |

| 2.4.2 Address Pipelining                                           |     |

| 2.5 Data-Transfer-Bus Acquisition                                  | 68  |

| 2.6 DTB Timing Rules and Observations                              | 70  |

|                                                                    | 101 |

| Chapter 3<br>Data Transfer Bus Arbitration                         |     |

| 3.1 Bus Arbitration Philosophy                                     |     |

| 3.1.1 Types Of Arbitration                                         |     |

| 3.2 Arbitration Bus Lines                                          |     |

| 3.2.1 Bus Request And Bus Grant Lines                              | 125 |

| 3.2.2 Bus Busy Line (BBSY*)                                        |     |

| 3.2.3 Bus Clear Line (BCLR*)                                       |     |

| 3.3 Functional Modules.                                            | 126 |

| 3.3.1 Arbiter                                                      | 126 |

| 3.3.3 Data Transfer Bus Master                                     | 133 |

| 3.3.3.1 Release Of The DTB                                         | 133 |

| 3.3.3.2 Acquisition Of The DTB                                     | 134 |

| 3.3.3.3 Other Information                                          | 134 |

| 3.4 Typical Operation                                              | 135 |

| 3.4.1 Arbitration Of Two Different Levels Of Bus Request           | 135 |

| 3.4.2 Arbitration Of Two Bus Requests On The Same Bus Request Line |     |

| 3.5 Race Conditions Between Master Requests and Arbiter Grants     | 144 |

| Chapter 4                                                          | 145 |

| Chapter 4<br>Priority Interrupt Bus                                |     |

| 4.1 Introduction                                                   |     |

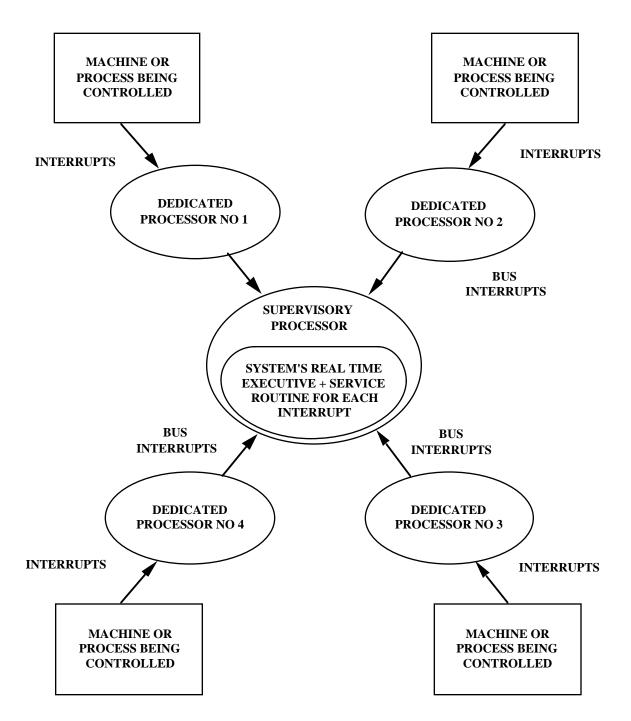

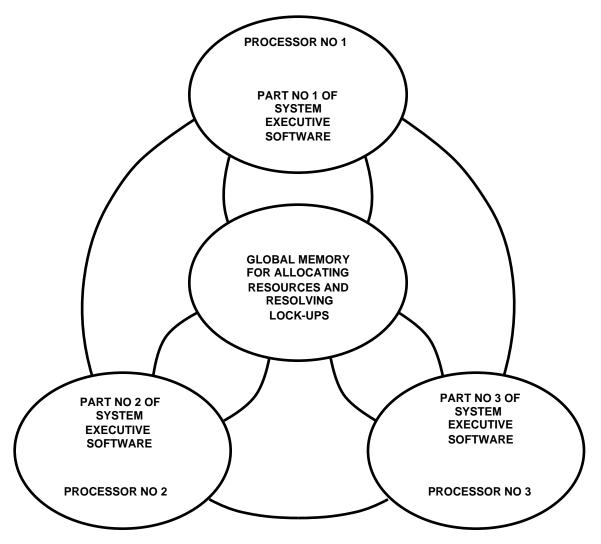

| 4.1.1 Single Handler Systems                                       | 145 |

| 4.1.2 Distributed Systems                                          |     |

| 4.2 Priority Interrupt Bus Lines                                   |     |

| 4.2.1 Interrupt Request Lines                                      | 149 |

| 4.2.2 Interrupt Acknowledge Line                                   | 149 |

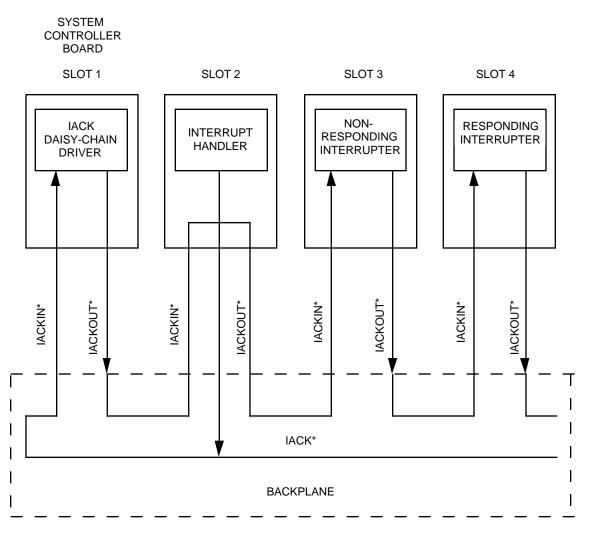

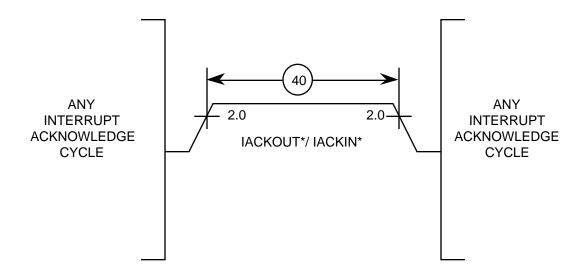

| 4.2.3 Interrupt Acknowledge Daisy-Chain - IACKIN*/IACKOUT*         | 149 |

| 4.3 Priority Interrupt Bus Modules - Basic Description             |     |

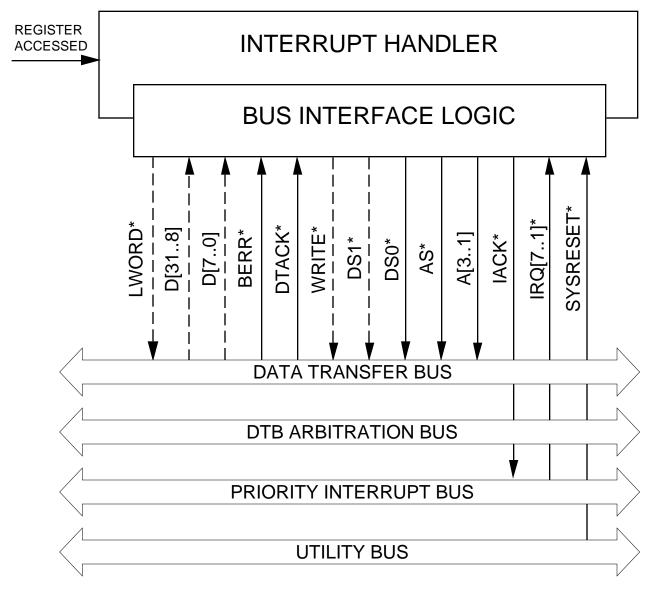

| 4.3.1 Interrupt Handler                                            | 151 |

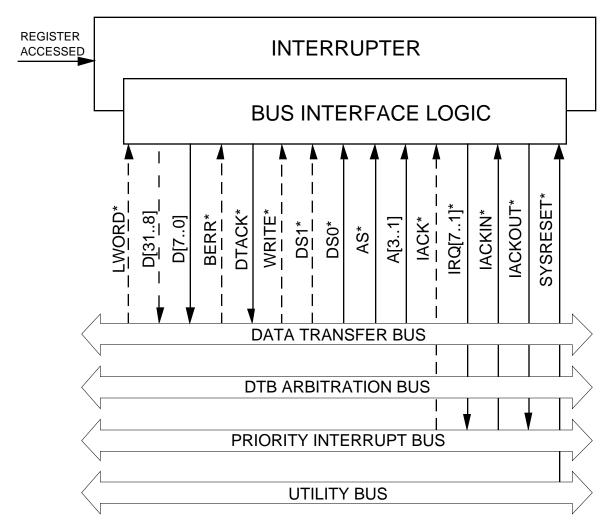

| 4.3.2 Interrupter                                                                         | .153 |

|-------------------------------------------------------------------------------------------|------|

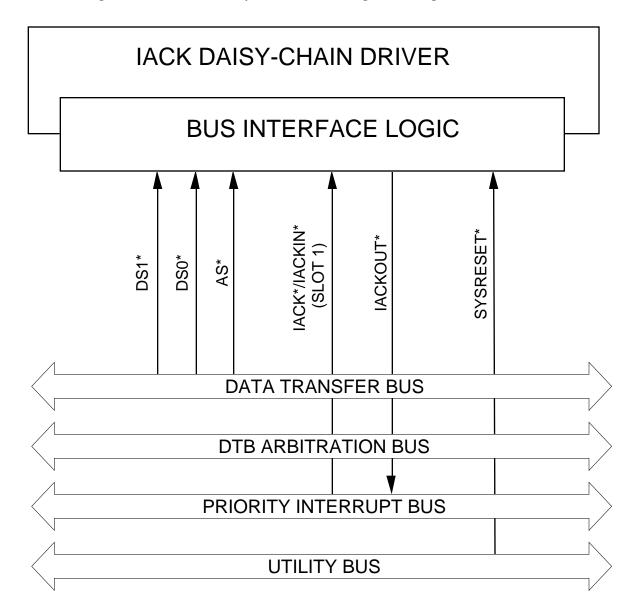

| 4.3.3 IACK Daisy-Chain Driver                                                             | .157 |

| 4.3.4 Interrupt Request Handling Capabilities                                             | .158 |

| 4.3.5 Interrupt Request Generation Capabilities                                           | .158 |

| 4.3.6 Status/Id Transfer Capabilities                                                     | .159 |

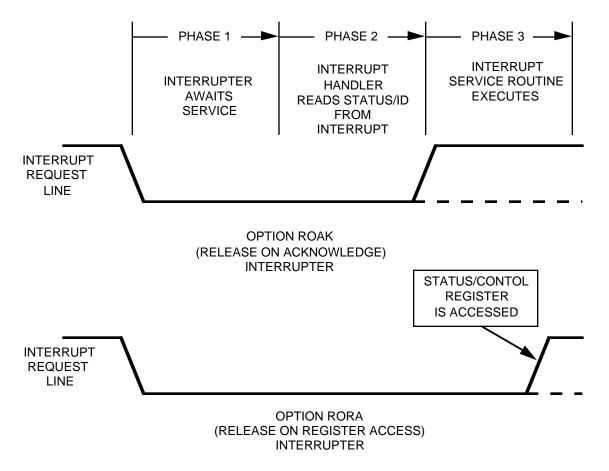

| 4.3.7 Interrupt Request Release Capabilities                                              | .160 |

| 4.3.8 Interaction Between Priority Interrupt Bus Modules                                  | .162 |

| 4.4 Typical Operation                                                                     |      |

| 4.4.1 Single Handler Interrupt Operation                                                  |      |

| 4.4.2 Distributed Interrupt Operation                                                     |      |

| 4.4.2.1 Distributed Interrupt Systems With Seven Interrupt Handlers                       | .166 |

| 4.4.2.2 Distributed Interrupt Systems With Two To Six Interrupt                           | 100  |

| Handlers                                                                                  |      |

| 4.4.3 Example: Typical Single Handler Interrupt System Operation                          | .169 |

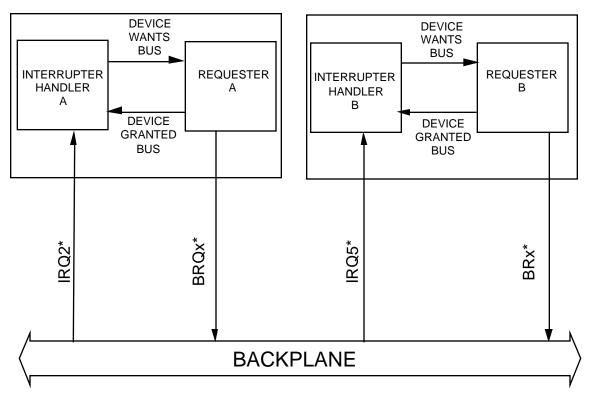

| 4.4.4 Example: Prioritization of Two Interrupts In A Distributed Interrupt System         | 172  |

| 4.5 Race Conditions                                                                       | .174 |

| 4.6 Priority Interrupt Bus Timing Rules and Observations                                  | .175 |

| Chapter 5                                                                                 | 100  |

| Chapter 5<br>Utility Bus                                                                  |      |

| 5.1 Introduction                                                                          | .199 |

| 5.2 Utility Bus Signal Lines                                                              | .199 |

| 5.3 Utility Bus Modules                                                                   |      |

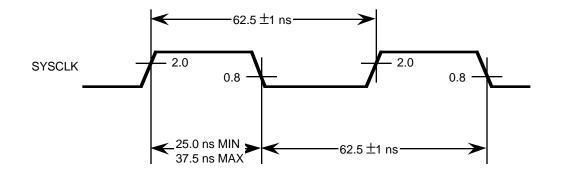

| 5.3.1 System Clock Driver                                                                 |      |

| 5.3.2 The Serial Bus Lines                                                                |      |

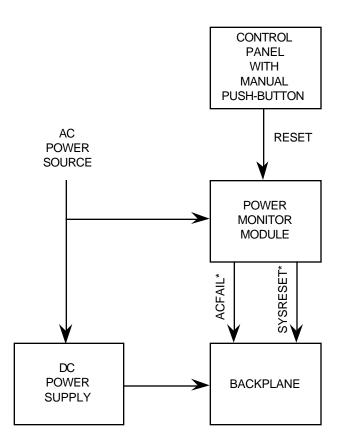

| <ul><li>5.3.3 Power Monitor.</li><li>5.4 System Initialization and Diagnostics.</li></ul> |      |

| 5.5 Power and Ground pins                                                                 | .207 |

| 5.6 Reserved Line                                                                         |      |

| 5.7 Auto Slot Id<br>5.8 Auto System Controller                                            |      |

| 5.8 Auto System Controller                                                                | .215 |

| Chapter 6                                                                                 | .217 |

| Electrical Specifications                                                                 |      |

| <ul><li>6.1 Introduction</li><li>6.2 Power Distribution</li></ul>                         | .217 |

| 6.2.1 DC Voltage Specifications                                                           |      |

| 6.2.2 Pin and Socket Connector Electrical Ratings                                         |      |

| 6.3 Electrical Signal Characteristics                                                     |      |

| 6.4 Bus Driving and Receiving Requirements                                                |      |

| 6.4.1 Bus Driver Definitions                                                              | .220 |

| 6.4.2 Driving And Loading RULEs For All VMEbus Lines                                      | .221 |

| 6.4.2.1 Driving And Loading RULEs For High Current Three-State Lines                      | .222 |

| 6.4.2.2 Driving And Loading RULEs For Standard Three-State Lines                          | .222 |

| 6.4.2.3 Driving And Loading RULEs For High Current Totem-Pole Lines                       | .223 |

| 6.4.2.4 Driving And Loading RULEs For Standard Totem-Pole Lines                           | .224 |

| 6.4.2.5 Driving And Loading RULEs For Open-Collector Lines                                | .225 |

| 6.5 Backplane Signal Line Interconnections                                                | .226 |

| 6.5.1 Termination Networks                                                                | .226 |

| 6.5.2 Characteristic Impedance                                                            | .228 |

| <ul><li>6.5.3 Additional Information</li><li>6.6 User Defined Signals</li></ul> |     |

|---------------------------------------------------------------------------------|-----|

| 6.7 Signal Line Drivers and Terminations                                        | 230 |

|                                                                                 |     |

| Chapter 7                                                                       |     |

| Mechanical Specifications                                                       |     |

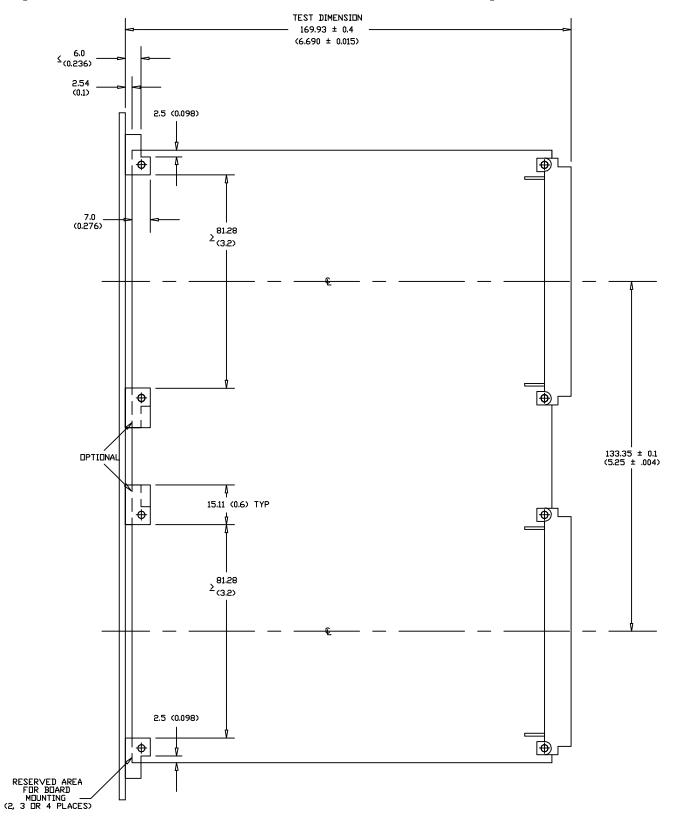

| <ul><li>7.1 Introduction</li><li>7.2 VMEbus Boards</li></ul>                    |     |

| 7.2 VillEbus Boards                                                             |     |

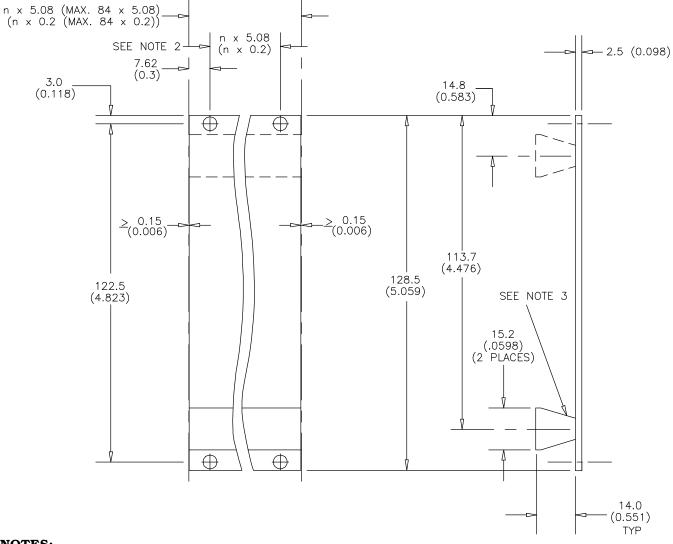

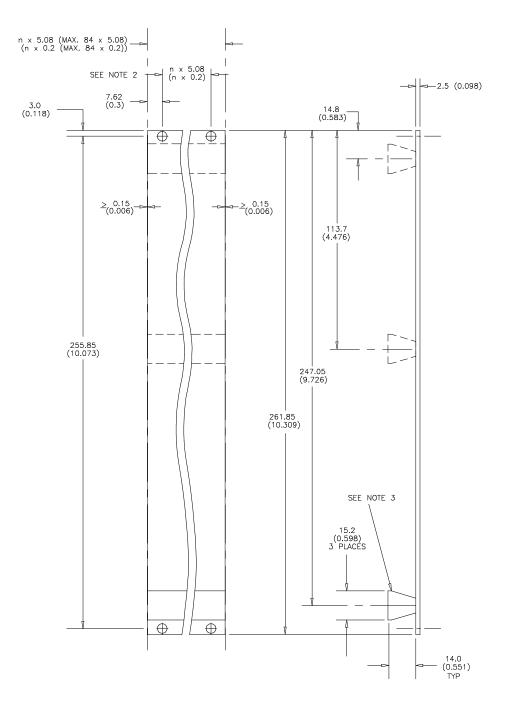

| 7.2.2 Double Height Boards                                                      |     |

| 7.2.3 Board Connectors                                                          |     |

| 7.2.4 Board Assemblies                                                          |     |

| 7.2.5 Board Widths                                                              |     |

| 7.2.6 VMEbus Board Warpage, Lead Length and Component Height                    |     |

| 7.3 Front Panels                                                                |     |

| 7.3.1 Handles                                                                   |     |

| 7.3.2 Front Panel Mounting                                                      | 240 |

| 7.3.3 Front Panel Dimensions                                                    |     |

| 7.3.4 Filler Panels                                                             |     |

| 7.3.5 Board Ejectors/Injectors                                                  | 242 |

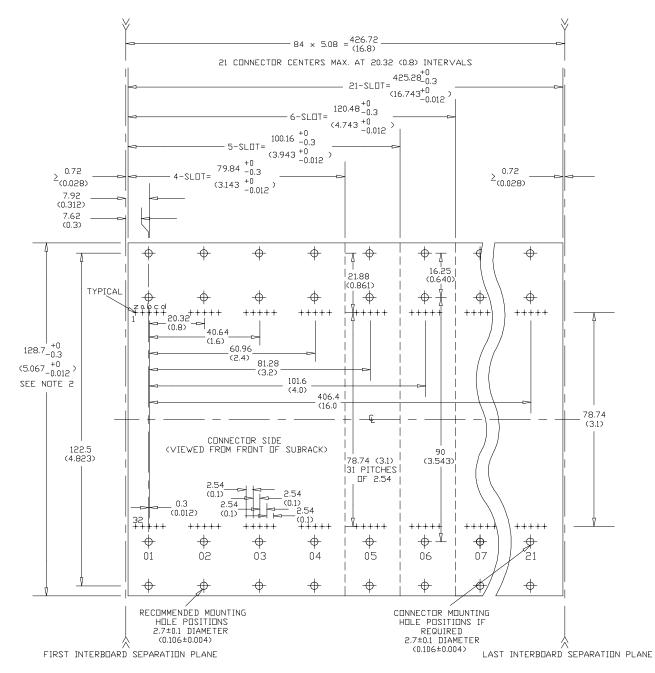

| 7.4 Backplanes                                                                  | 242 |

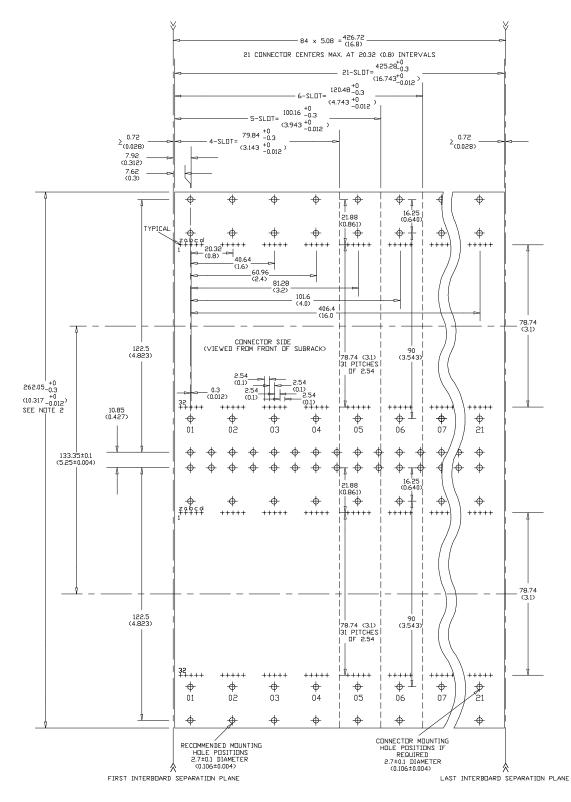

| 7.4.1 Backplane Dimensional Requirements                                        | 243 |

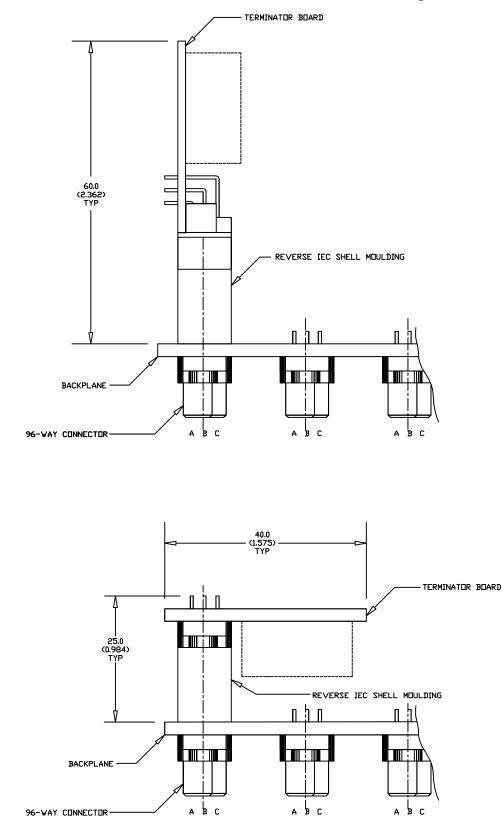

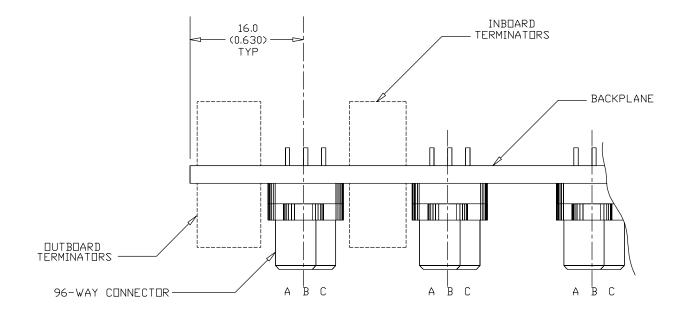

| 7.4.2 Signal Line Termination Networks                                          | 244 |

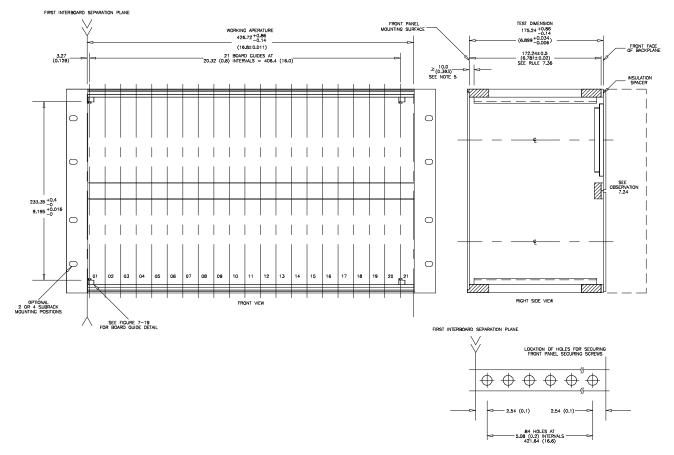

| 7.5 Assembly of VMEbus Subracks                                                 |     |

| 7.5.1 Subracks And Slot Widths                                                  |     |

| 7.5.2 Subrack Dimensions                                                        |     |

| 7.6 Conduction Cooled VMEbus Systems                                            |     |

| 7.7 VMEbus Backplane Connectors and VMEbus Board Connectors                     |     |

| 7.7.1 Pin Assignments For The J1/P1 Connector                                   |     |

| 7.7.2 Pin Assignments For The J2/P2 Connector                                   |     |

| Appendix A                                                                      |     |

| Glossary of VMEbus Terms                                                        |     |

| ·                                                                               |     |

| Appendix B                                                                      |     |

| VMEBus Connector/Pin Description                                                |     |

| Appendix C                                                                      |     |

| Manufacturer's Board Identification                                             |     |

|                                                                                 |     |

| Appendix D<br>Rule Index                                                        |     |

|                                                                                 |     |

## List of Figures

|               |                                                                            | _   |

|---------------|----------------------------------------------------------------------------|-----|

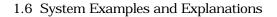

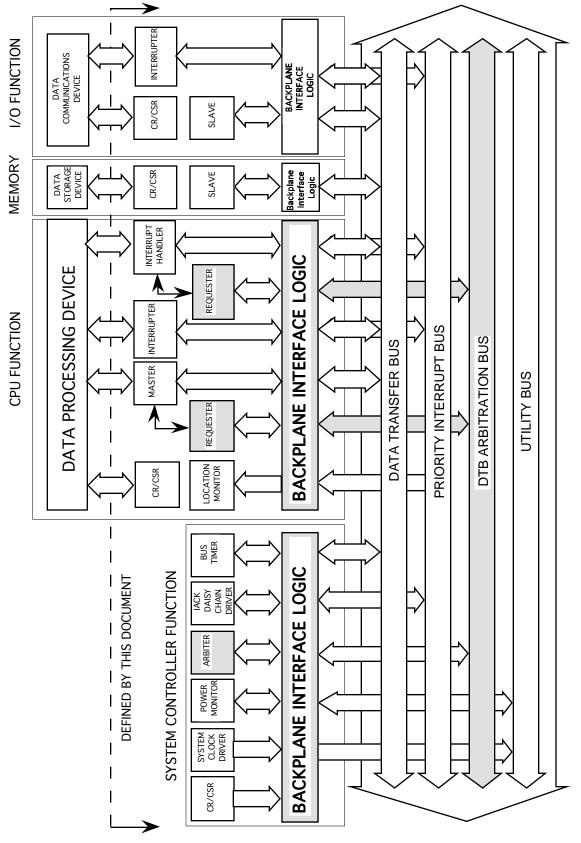

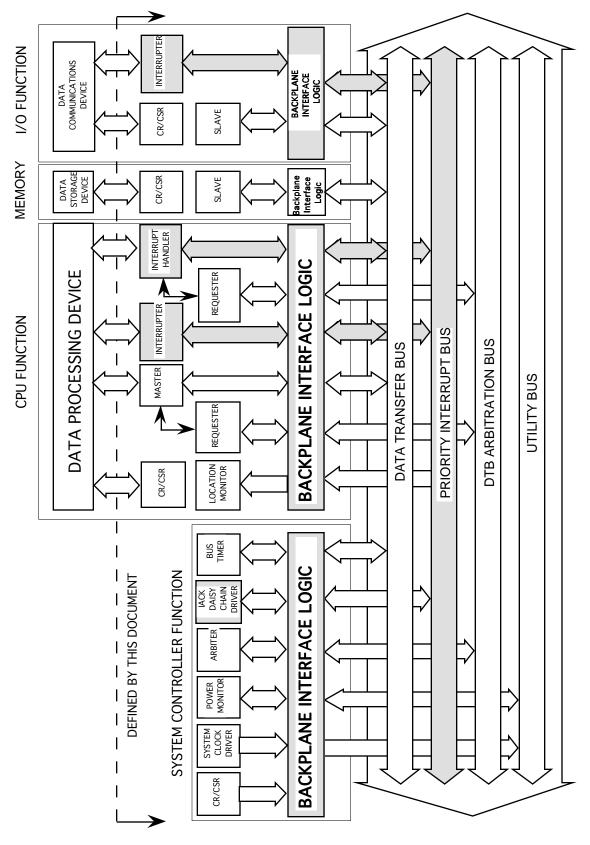

| Figure 1 - 1  | System Elements Defined By This Document                                   | 3   |

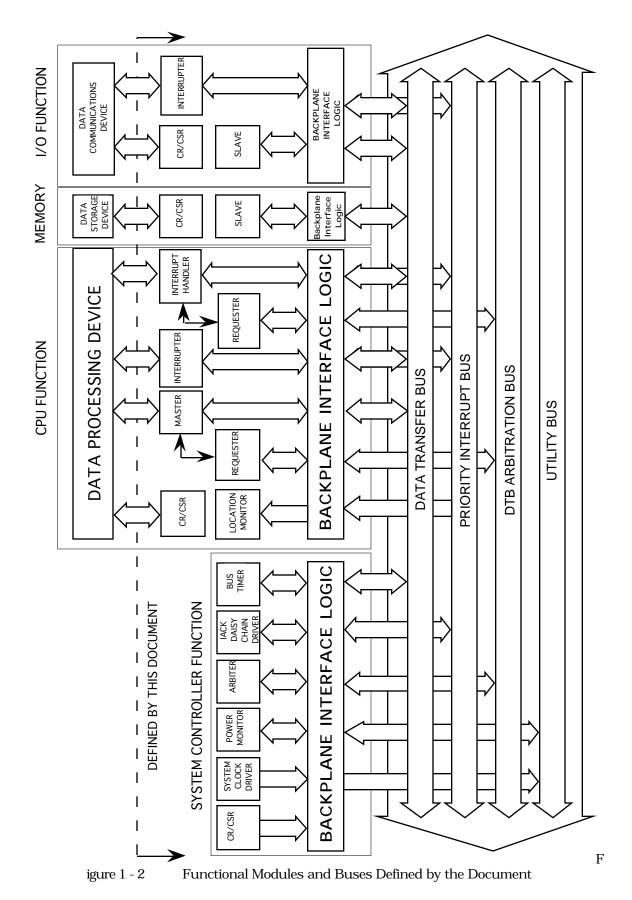

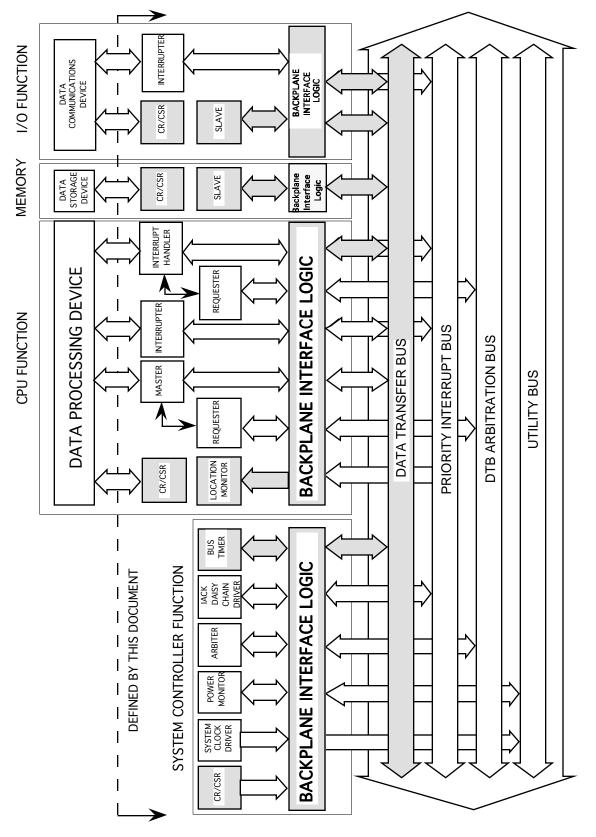

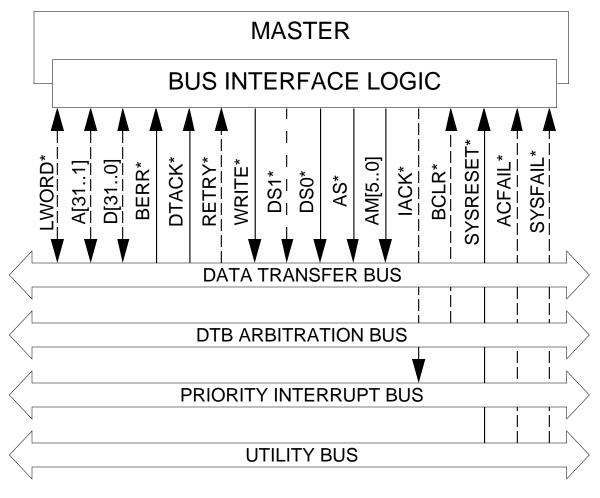

| Figure 1 - 2  | Functional Modules and Buses Defined by the Document                       | 8   |

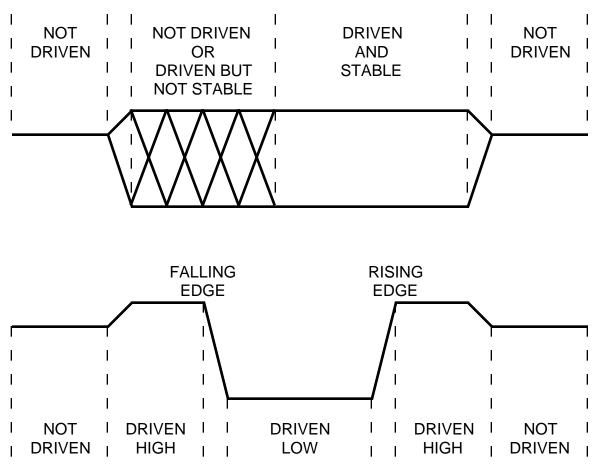

| Figure 1 - 3  | Signal Timing Notation                                                     |     |

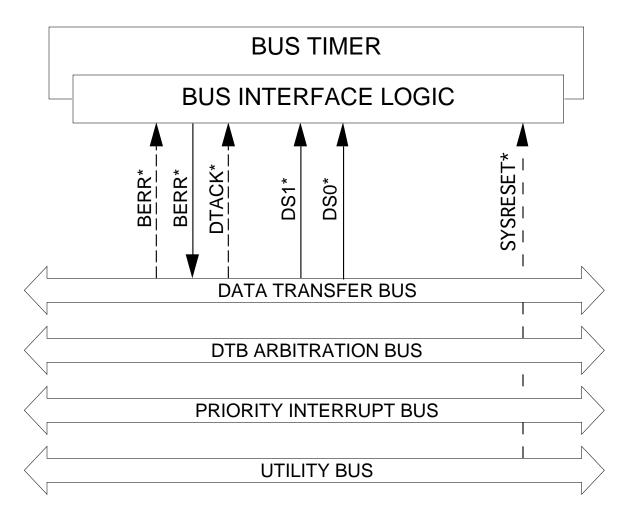

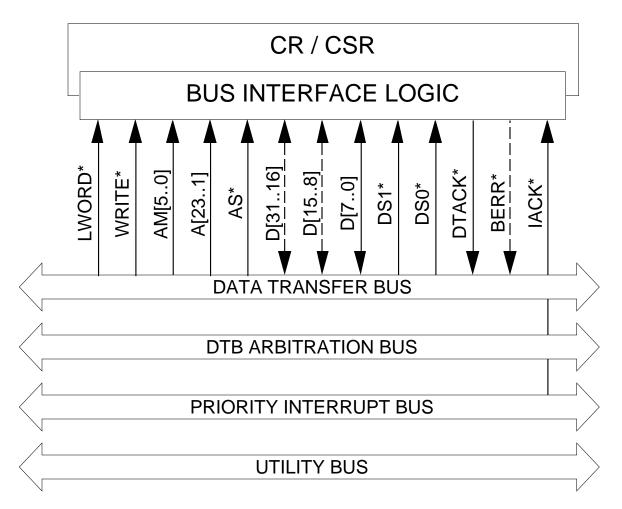

| Figure 2 - 1  | Data Transfer Bus Functional Block Diagram                                 |     |

| Figure 2 - 2  | Block Diagram                                                              |     |

| Figure 2 - 3  | Block Diagram                                                              |     |

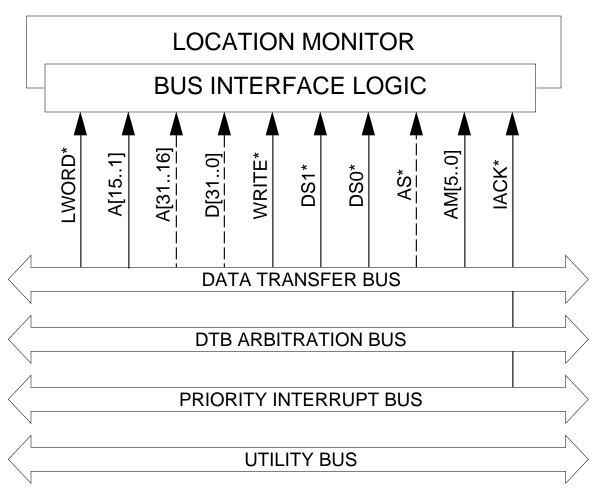

| Figure 2 - 4  | Block Diagram                                                              | 35  |

| Figure 2 - 5  | Block Diagram.                                                             |     |

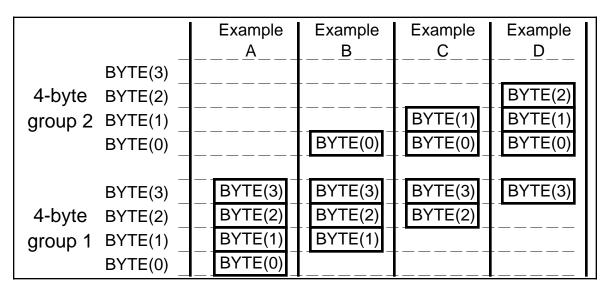

|               | Four Ways That 32 Bits Of Data Might Be Stored In Memory                   |     |

| Figure 2 - 6  |                                                                            |     |

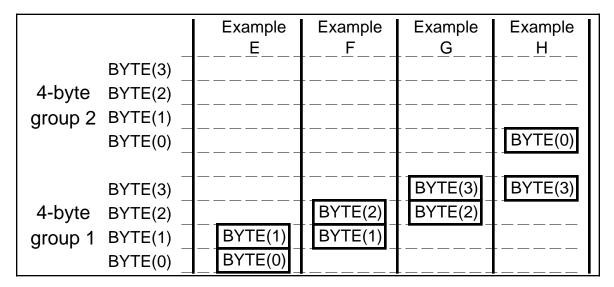

| Figure 2 - 7  | Four Ways That 16 Bits of Data Might Be Stored in Memory                   | .40 |

| Figure 2 - 34 | Block Diagram<br>An Example of a Non-multiplexed Address, Single-Byte Read |     |

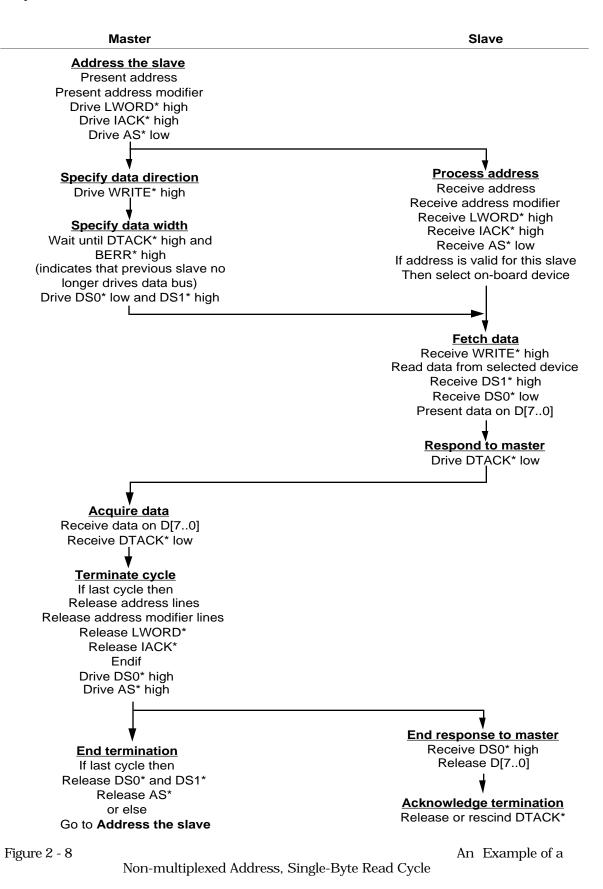

| Figure 2 - 8  | An Example of a Non-multiplexed Address, Single-Byte Read                  | 0.1 |

|               | Cycle                                                                      |     |

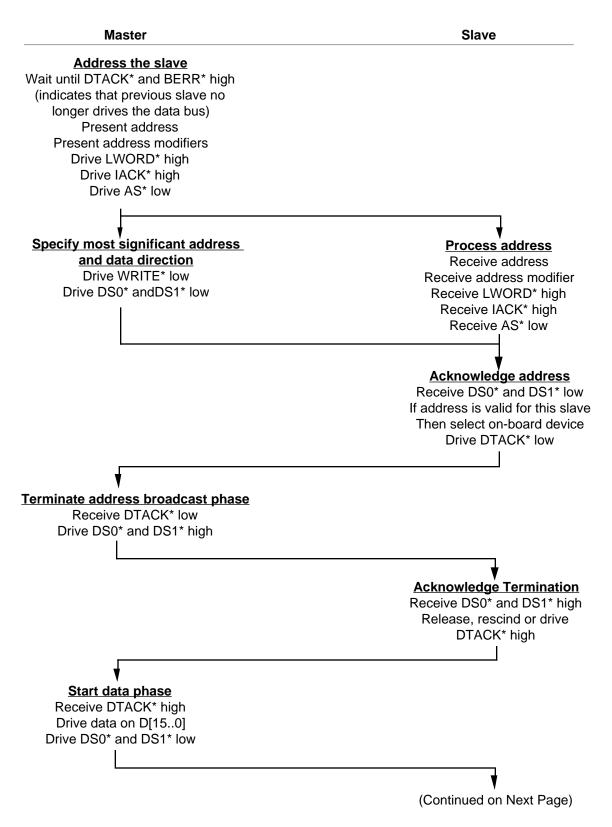

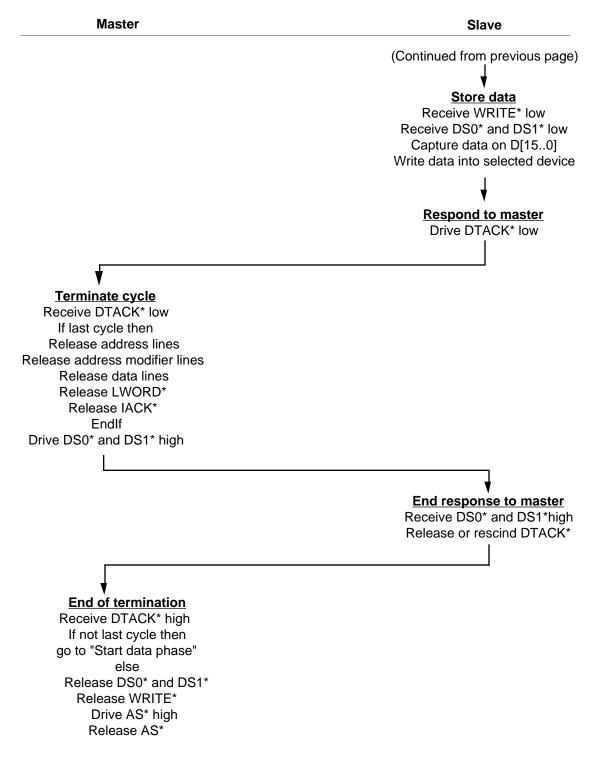

| Figure 2 - 9  | An Example Of A Multiplexed Address Double-Byte Write Cycle                |     |

| Figure 2 - 10 | An Example Of A Non-multiplexed Address Quad-Byte Write Cycle              |     |

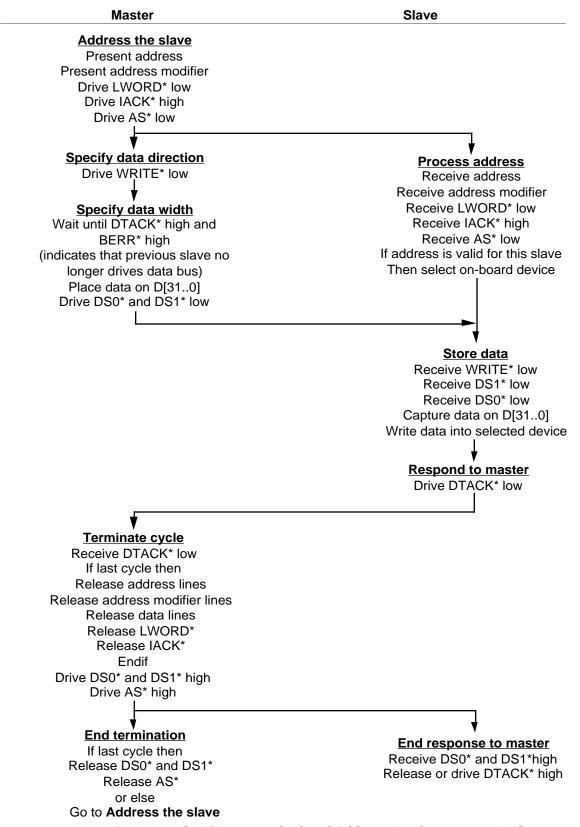

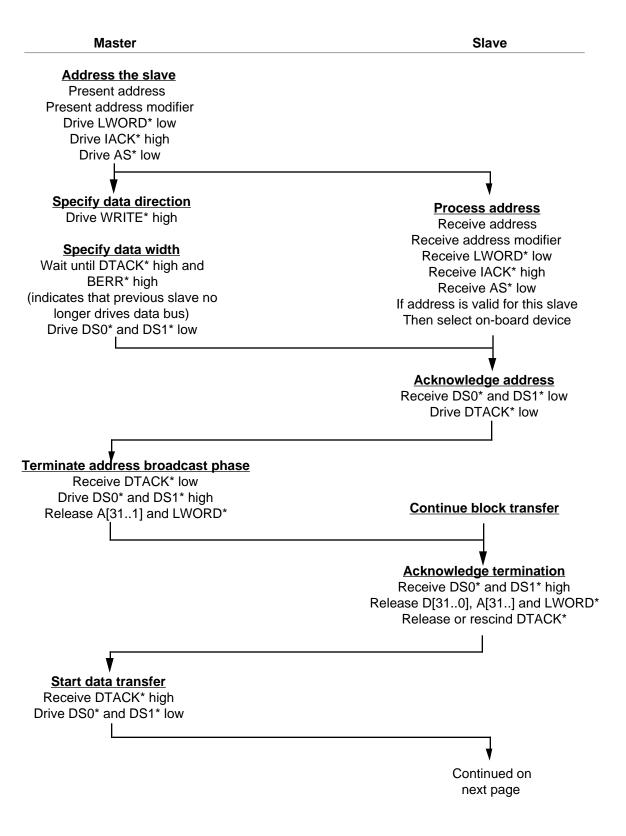

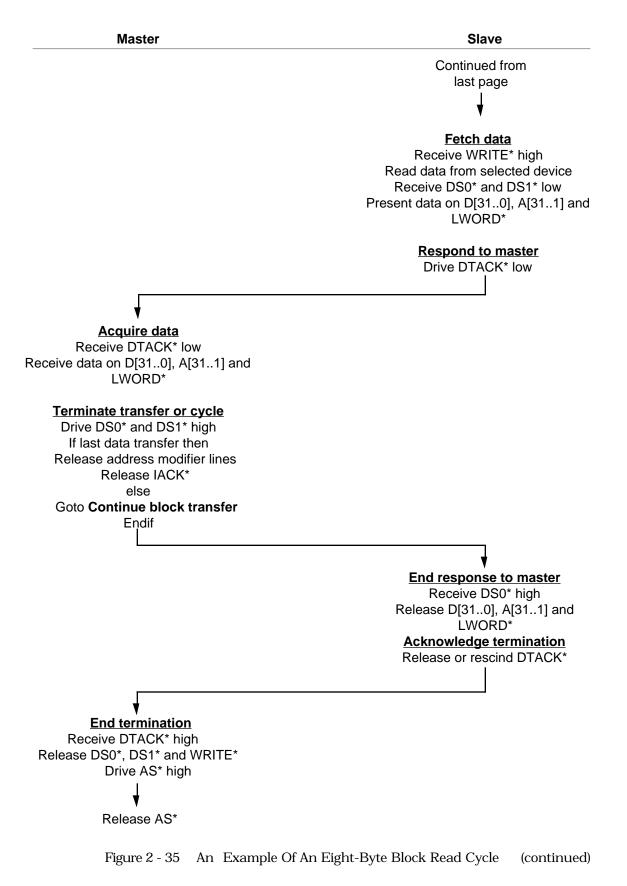

| Figure 2 - 35 | An Example Of An Eight-Byte Block Read Cycle                               | 65  |

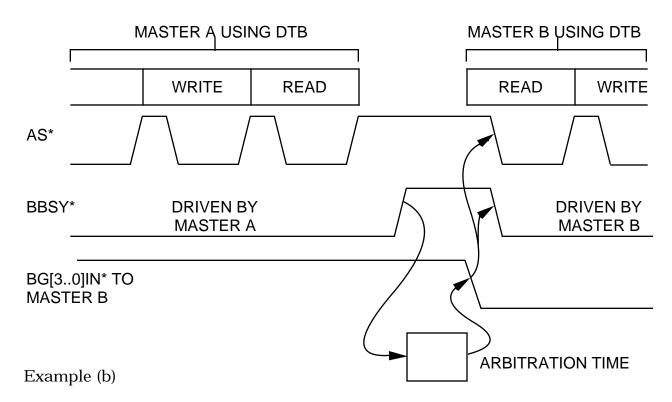

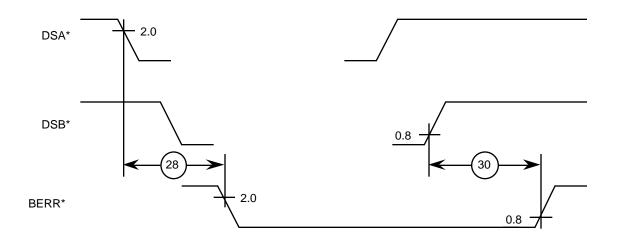

| Figure 2 - 11 | Data Transfer Bus Master Exchange Sequence                                 | 69  |

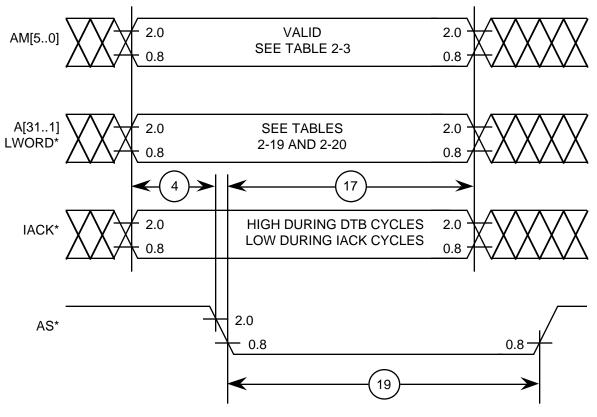

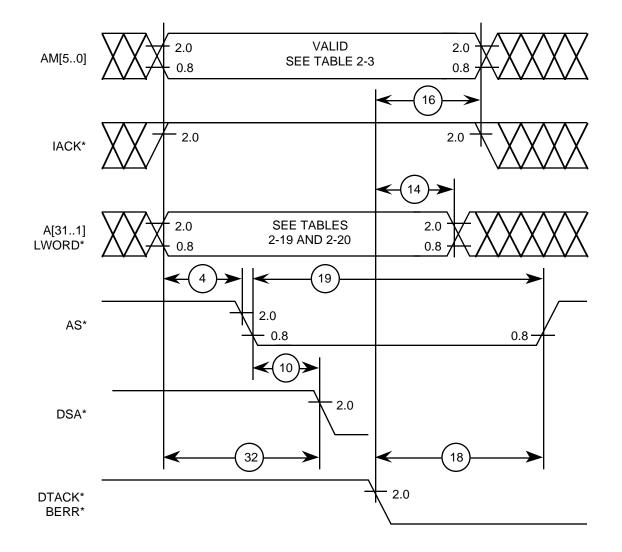

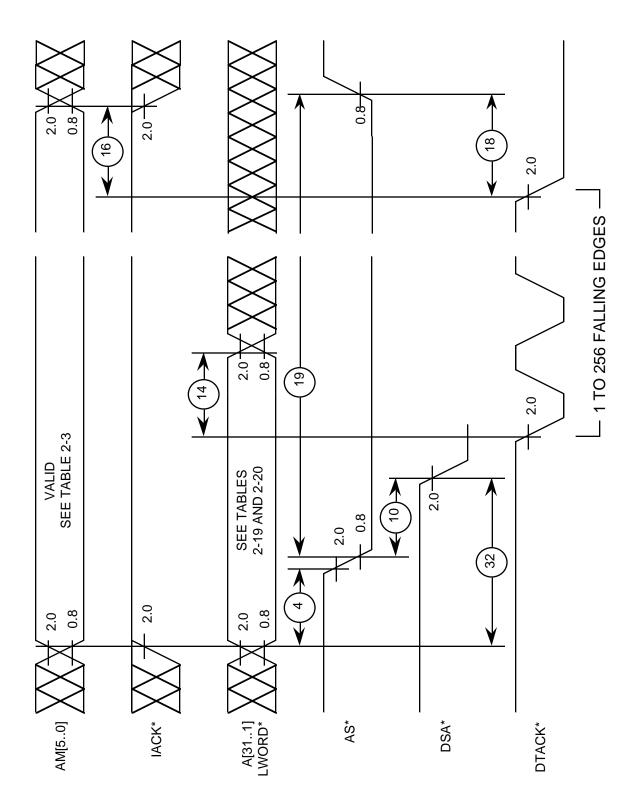

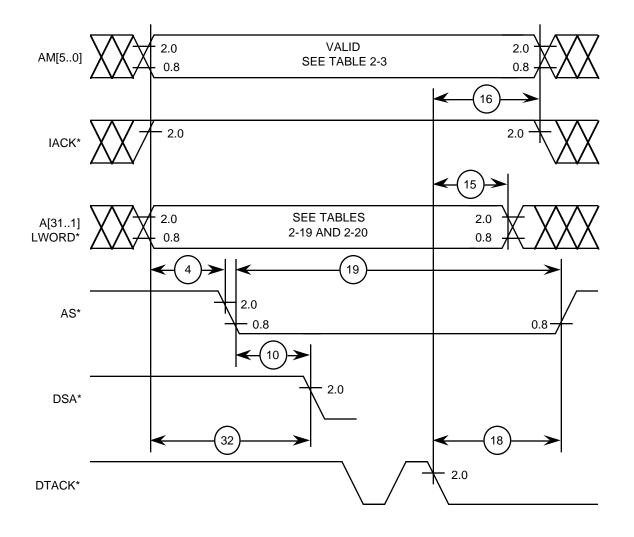

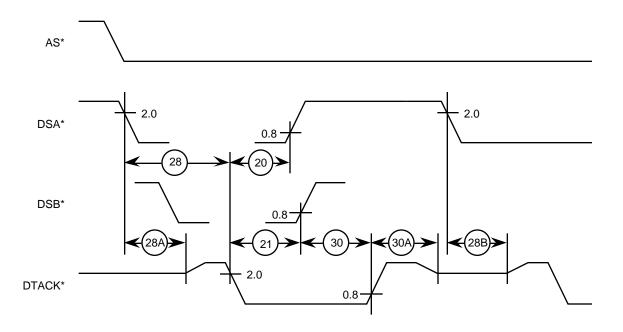

| Figure 2 - 12 | Address Broadcast Timing - All Cycles                                      | 95  |

| Figure 2 - 13 | A16, A24, A32 Master, Responding Slave, And Location Monitor               | .96 |

| Figure 2 - 14 | Master, Slave, and Location Monitor - A16, A24 and A32 Address             |     |

| 0             | Broadcast Timing                                                           | 97  |

| Figure 2 - 15 | Master, Slave, And Location Monitor A16, A24, And A32 Address              |     |

| 0             | Broadcast Timing                                                           | 98  |

| Figure 2 - 27 | Master, Slave And Location Monitor - A64 , A40, And ADOH                   |     |

|               | Address Broadcast Timing                                                   | 99  |

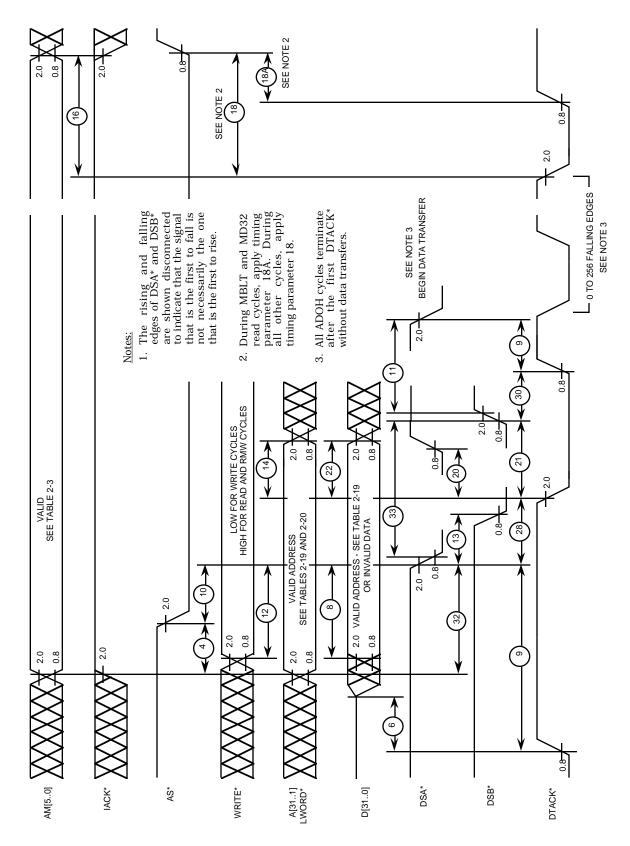

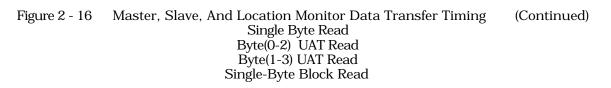

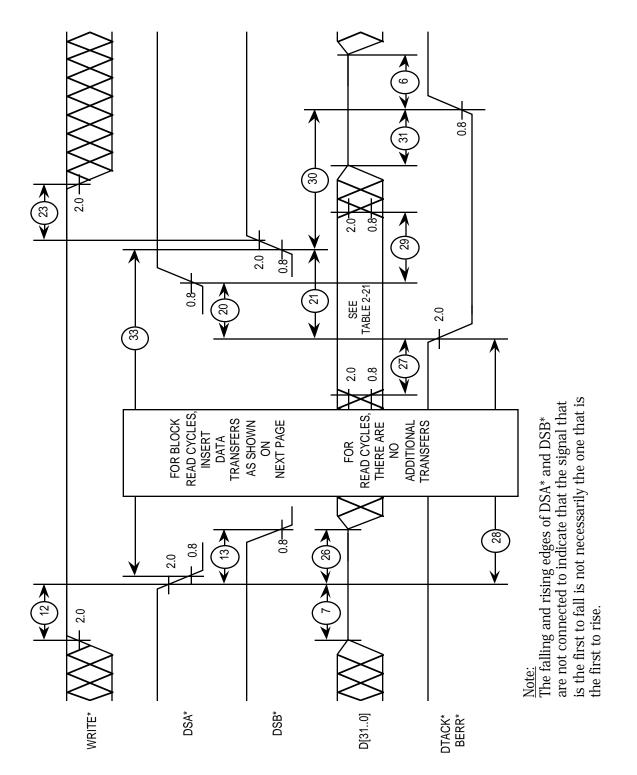

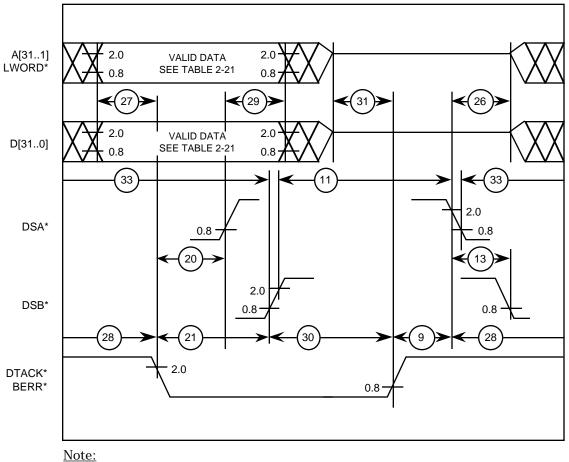

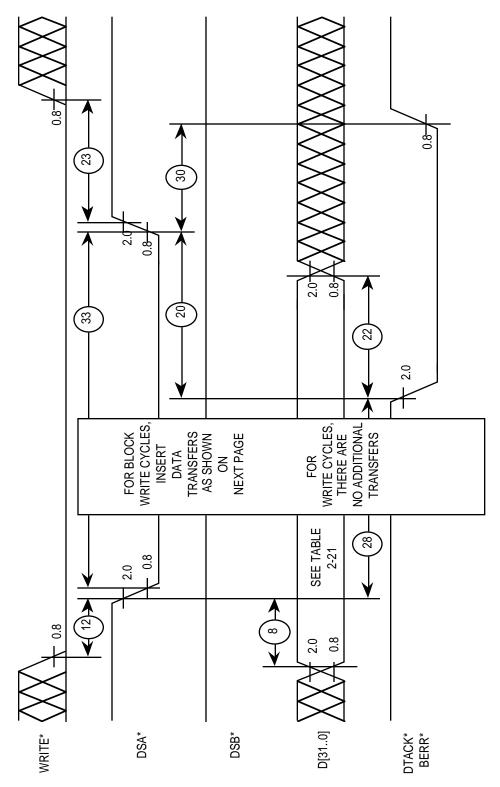

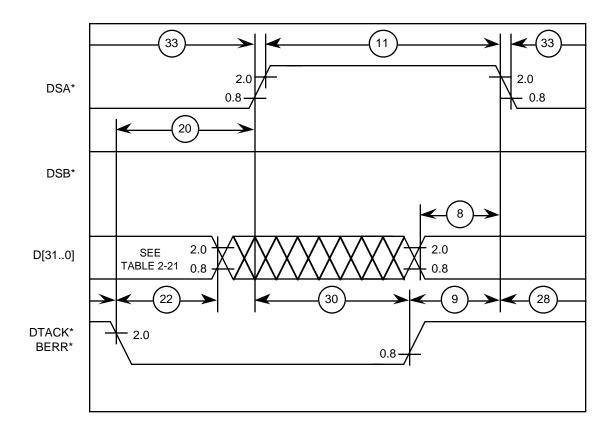

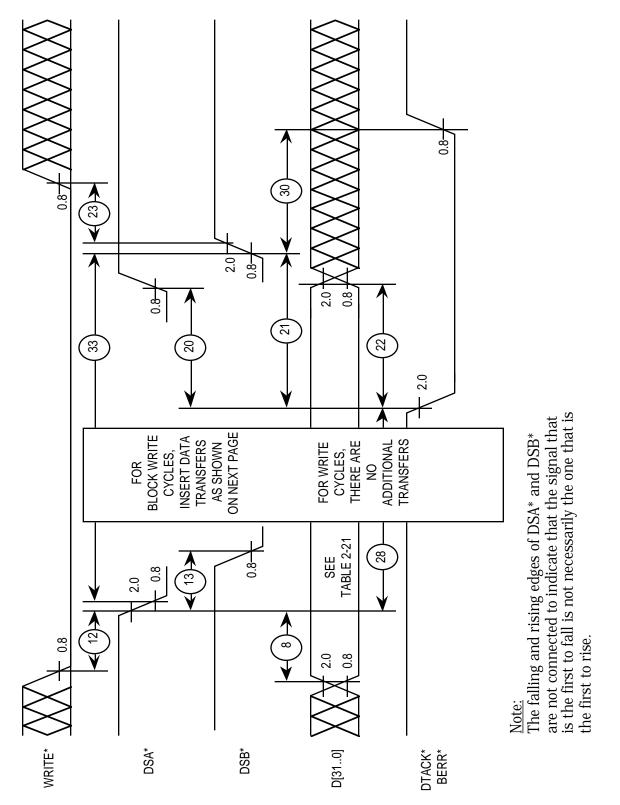

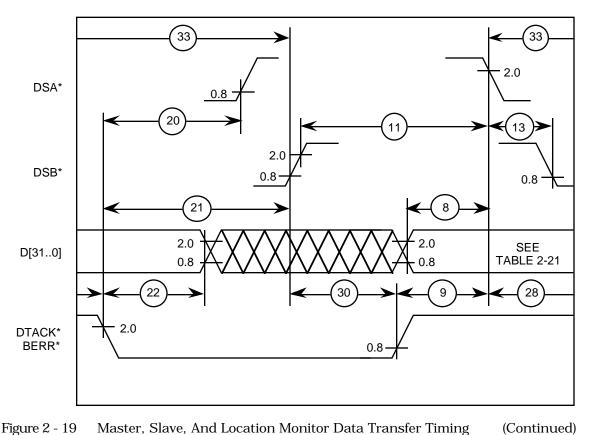

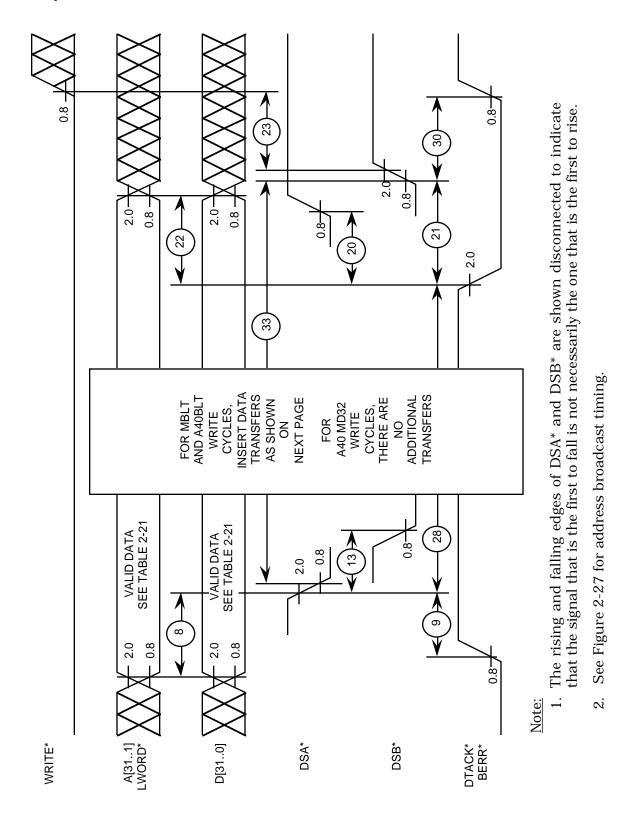

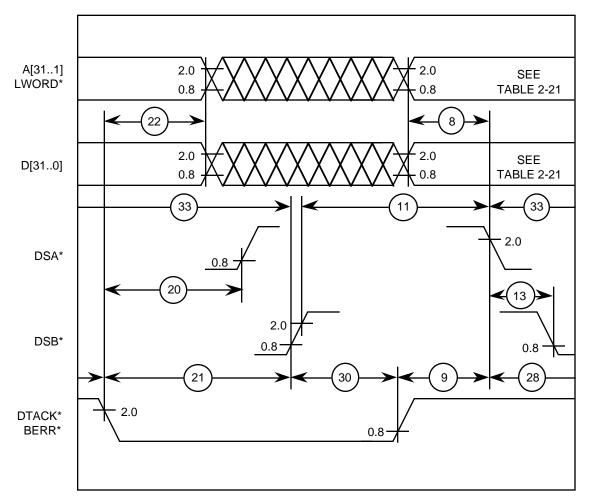

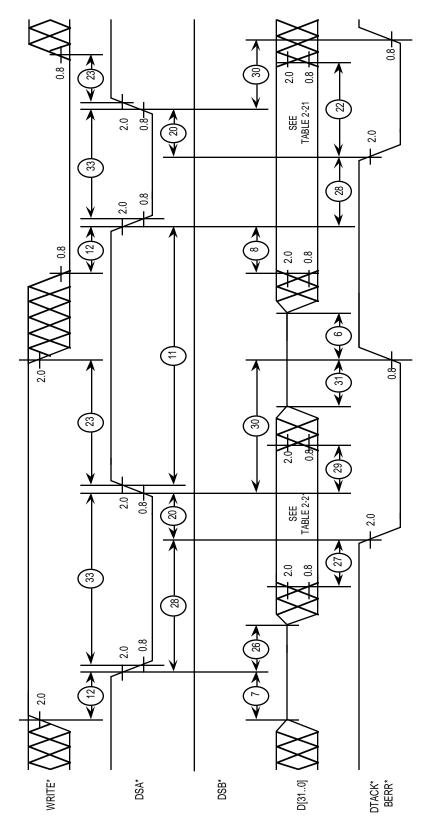

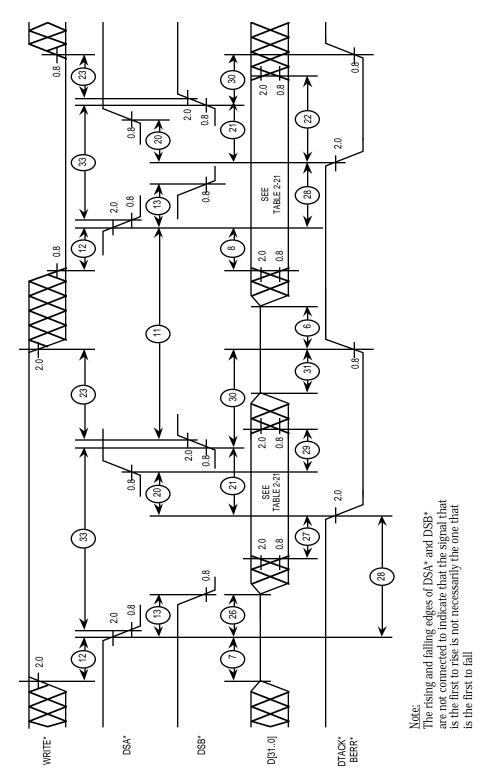

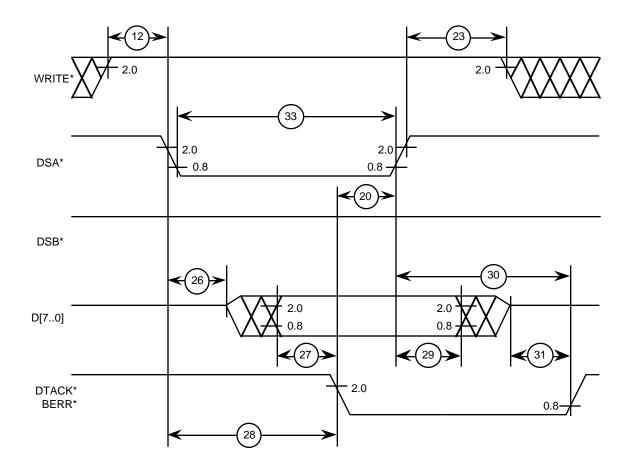

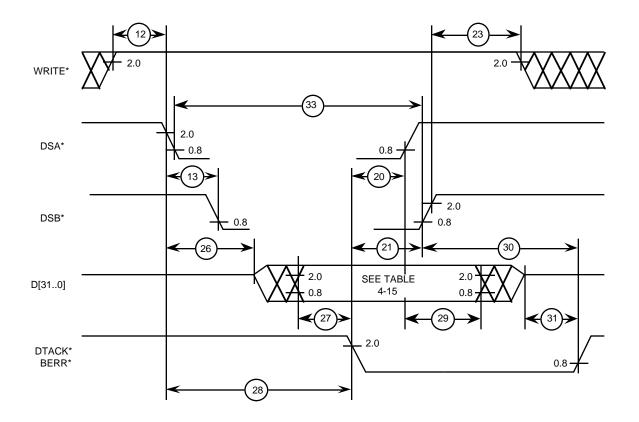

| Figure 2 - 16 | Master, Slave, And Location Monitor Data Transfer Timing                   | 100 |

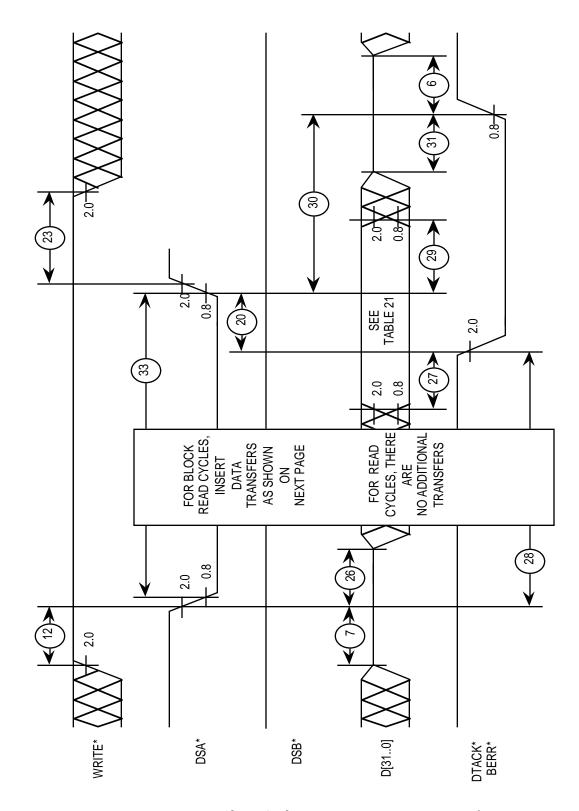

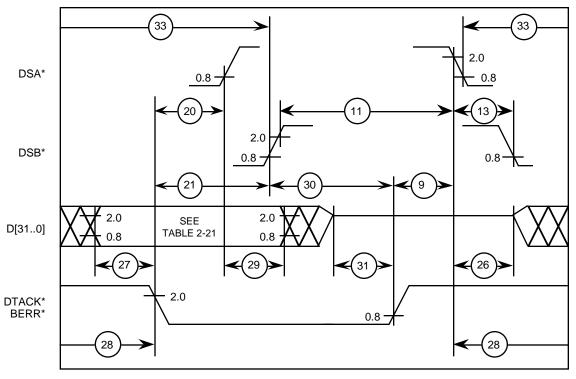

| Figure 2 - 17 | Master, Slave, And Location Monitor Data Transfer Timing                   |     |

|               | Master, Slave And Location Monitor Data Transfer Timing                    |     |

| Figure 2 - 28 |                                                                            |     |

| Figure 2 - 18 | Master, Slave, And Location Monitor Data Transfer Timing                   |     |

| Figure 2 - 19 | Master, Slave, And Location Monitor Data Transfer Timing                   |     |

| Figure 2 - 29 | Master, Slave And Location Monitor Data Transfer Timing                    | 110 |

| Figure 2 - 20 | Master, Slave, And Location Monitor Data Transfer Timing                   | 110 |

|               | Single-Byte RMW Cycles                                                     |     |

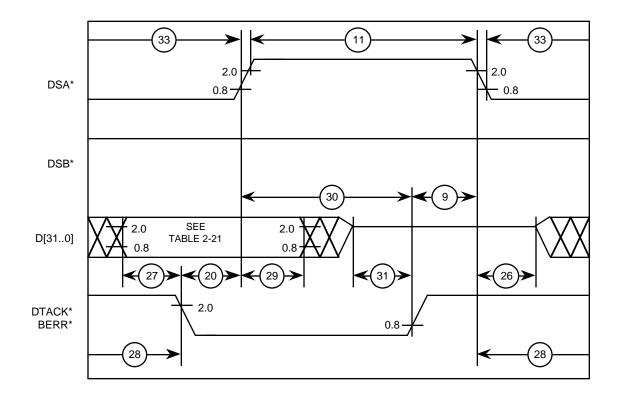

| Figure 2 - 21 | Master, Slave, and Location Monitor Data Transfer Timing                   | 113 |

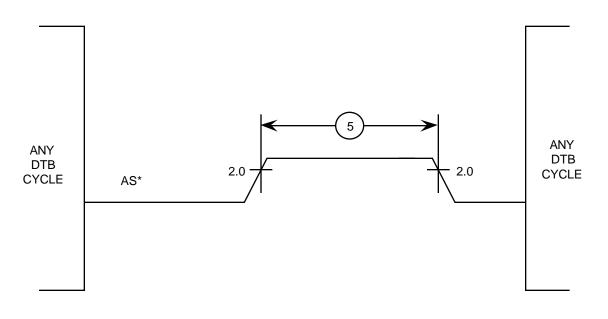

| Figure 2 - 22 | Address Strobe Inter-Cycle Timing                                          | 114 |

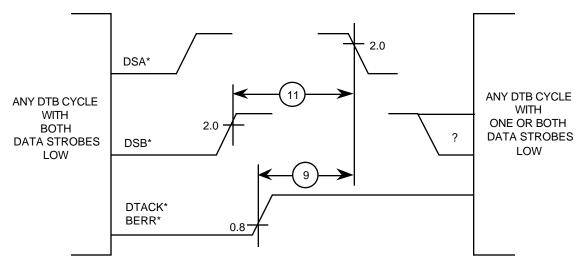

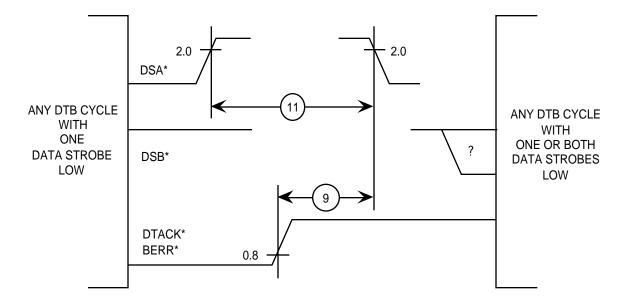

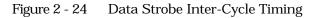

| Figure 2 - 23 | Data Strobe Inter-Cycle Timing                                             | 114 |

| Figure 2 - 24 | Data Strobe Inter-Cycle Timing                                             | 115 |

| Figure 2 - 25 | Master, Slave, And Bus Timer Data Transfer Timing                          | 115 |

| Figure 2 - 26 | Master DTB Control Transfer Timing                                         |     |

| Figure 2 - 30 | Master And Slave Data Transfer Timing                                      | 117 |

| Figure 2 - 31 | Master And Slave Data Transfer Timing                                      | 118 |

| Figure 2 - 32 | A40, MD32 Read-Modify-Write                                                |     |

| Figure 2 - 33 | Rescinding DTACK Timing                                                    |     |

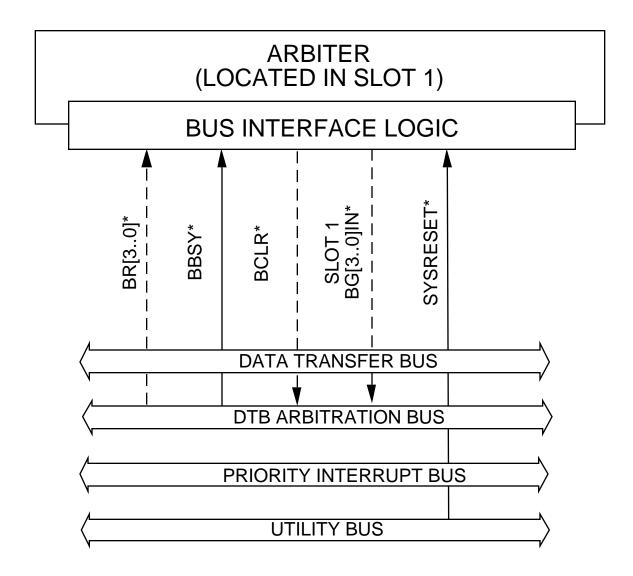

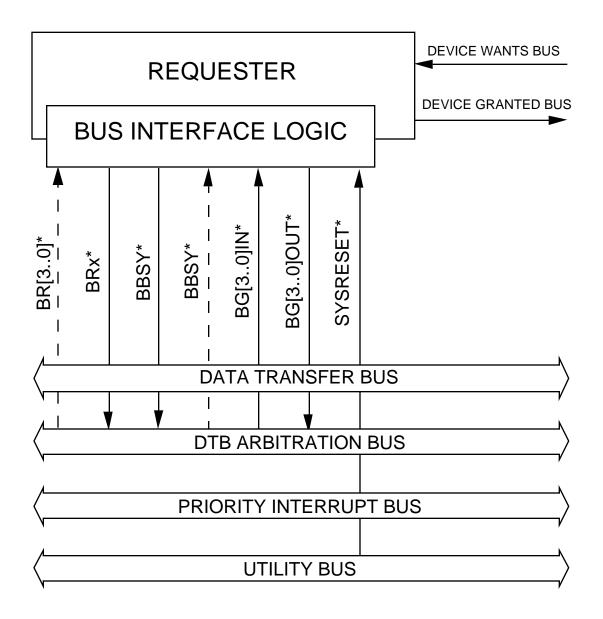

| Figure 3 - 1  | Arbitration Functional Block Diagram                                       |     |

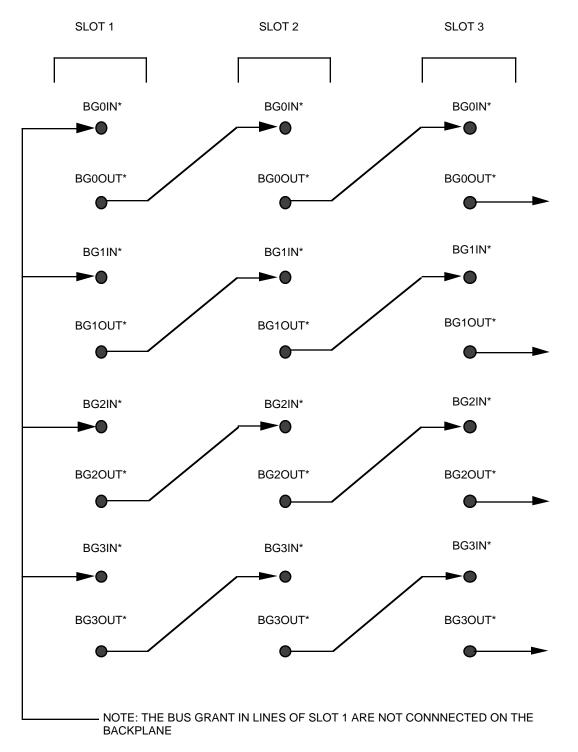

| Figure 3 - 2  | Illustration Of The Daisy Chain Bus Grant Lines                            | 124 |

| Figure 3 - 3  | Block Diagram.                                                             |     |

| Figure 3 - 4  | Block Diagram                                                              |     |

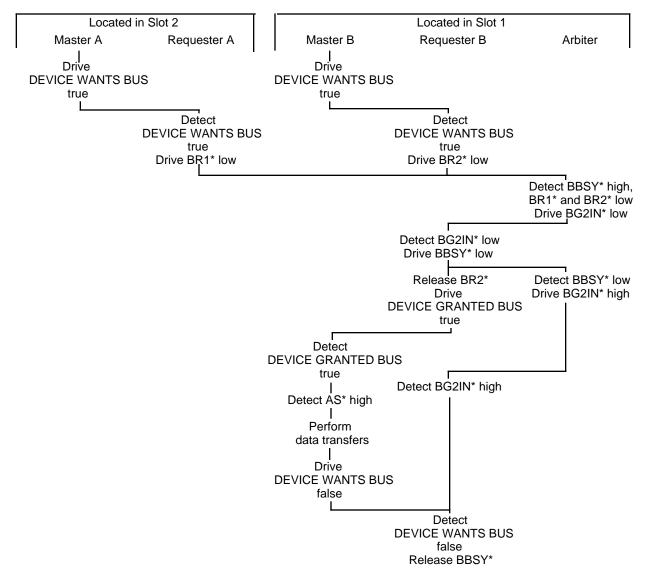

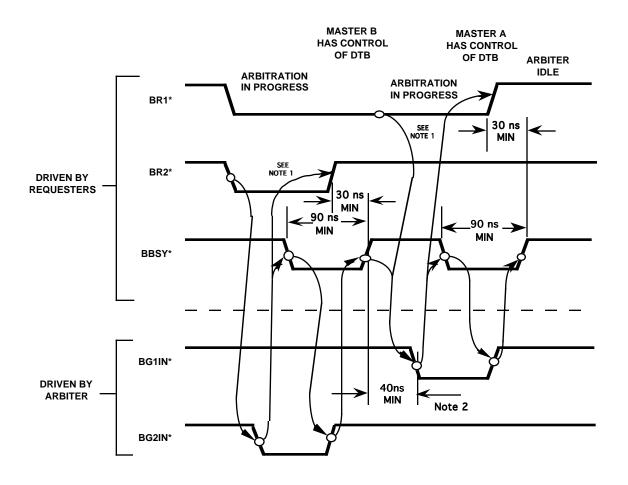

| Figure 3 - 5  | Arbitration Flow Diagram Two Requesters,                                   | 136 |

| Figure 3 - 6  |                                                                            | 150 |

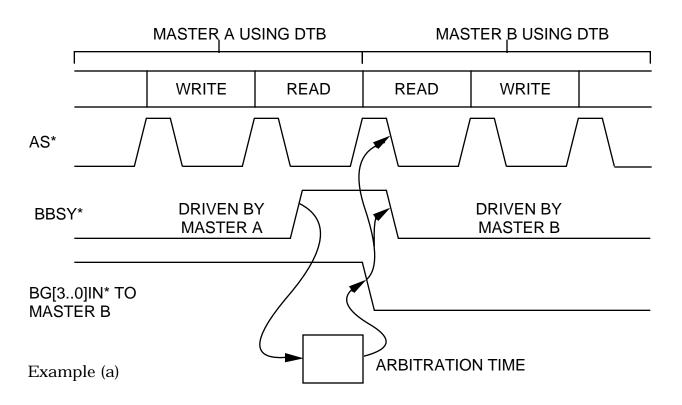

| Figure 5 - 0  | Arbitration Sequence Diagram Two Requesters, Two Request                   | 190 |

| Figure 2 7    | Levels.                                                                    |     |

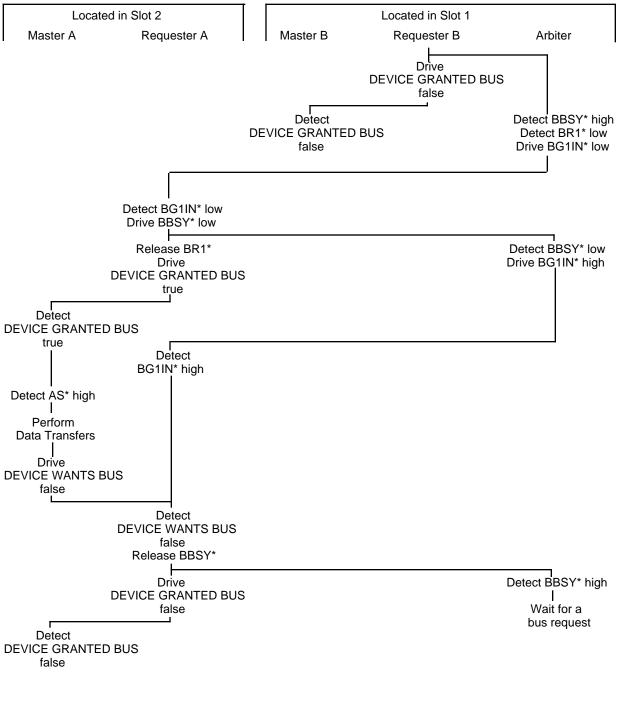

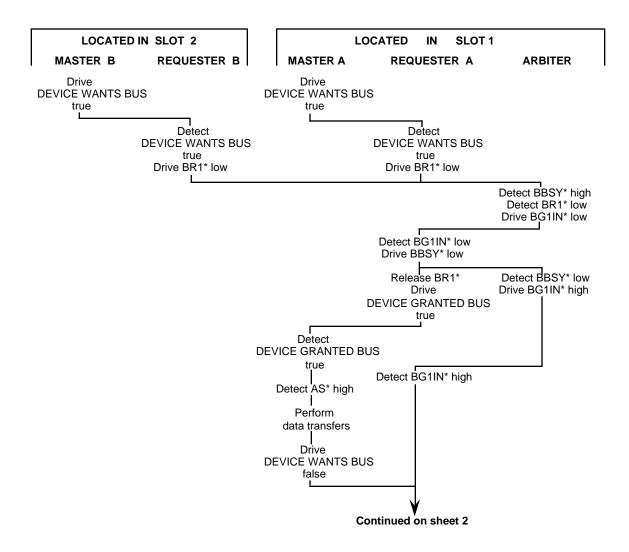

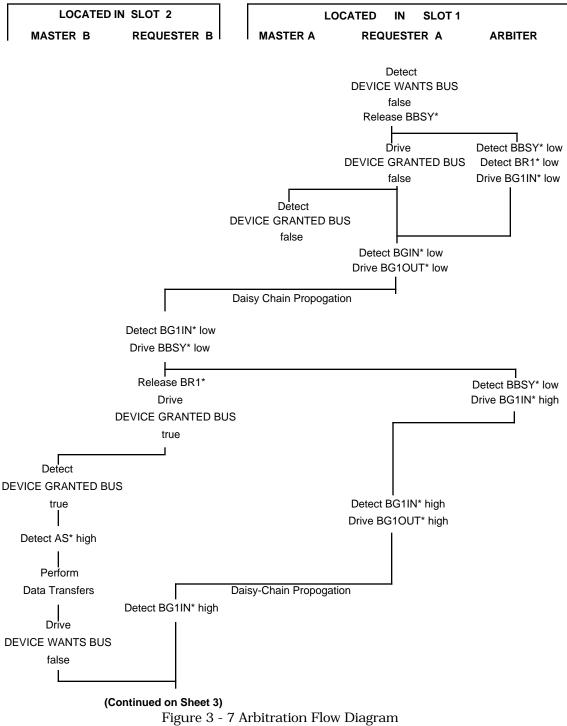

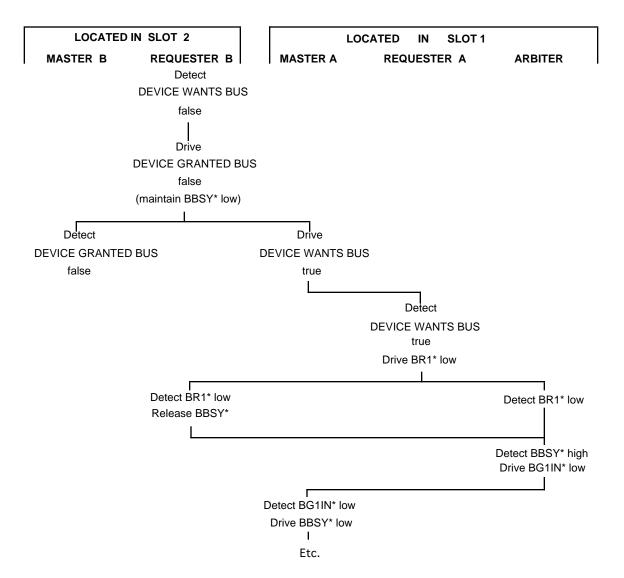

| Figure 3 - 7  | Arbitration Flow Diagram                                                   |     |

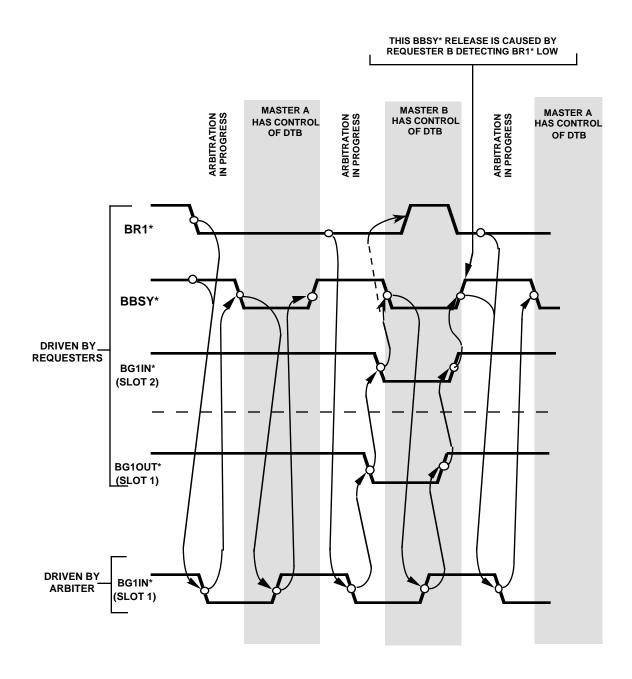

| Figure 3 - 8  | Arbitration Sequence Diagram.                                              |     |

| Figure 4 - 1  | Priority Interrupt Bus Functional Diagram                                  |     |

| Figure 4 - 2  | Interrupt Subsystem Structure                                              |     |

| Figure 4 - 3  | Interrupt Subsystem Structure                                              | 148 |

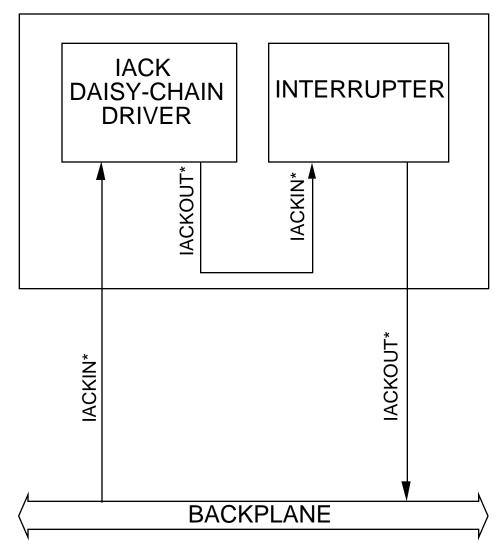

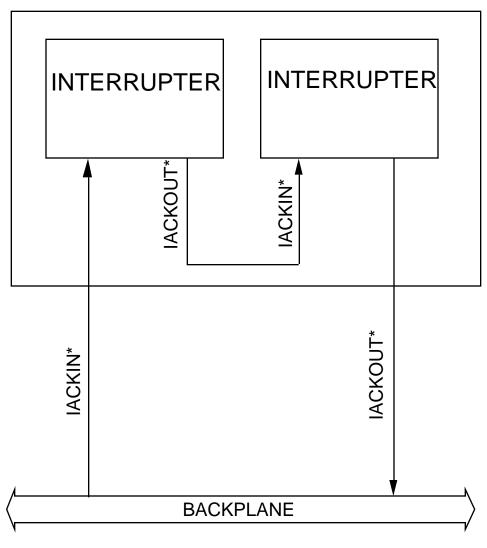

| Figure 4 - 4  | IACKIN*/IACKOUT* DAISY-CHAIN                                   |      |

|---------------|----------------------------------------------------------------|------|

| Figure 4 - 5  | Block Diagram.                                                 |      |

| Figure 4 - 6  | Block Diagram                                                  |      |

| Figure 4 - 7  | Block Diagram                                                  |      |

| Figure 4 - 8  | Release Of Interrupt Request Lines By ROAK And RORA            |      |

| inguio i o    | Interrupters                                                   |      |

| Figure 4 - 9  | An IACK Daisy-Chain Driver And Interrupter On The Same Board   |      |

| Figure 4 - 10 | Two Interrupters On The Same Board                             |      |

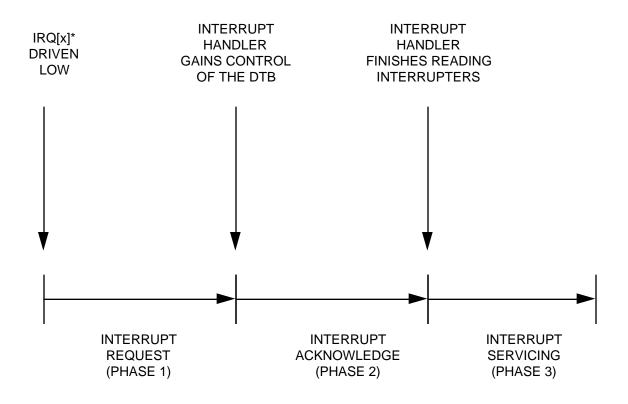

| Figure 4 - 11 | The Three Phases Of An Interrupt Sequence                      | 166  |

| Figure 4 - 12 | Two Interrupt Handlers, Each Monitoring One Interrupt          |      |

| Figure 4 - 13 | Two Interrupt Handlers, Each Monitoring Several Interrupt      | 168  |

| Figure 4 - 14 | Typical Single Handler Interrupt System Operation              | 170  |

| Figure 4 - 15 | Typical Distributed Interrupt System With Two Interrupt        |      |

| liguit 4 10   | Handlers, Flow Diagram                                         | 173  |

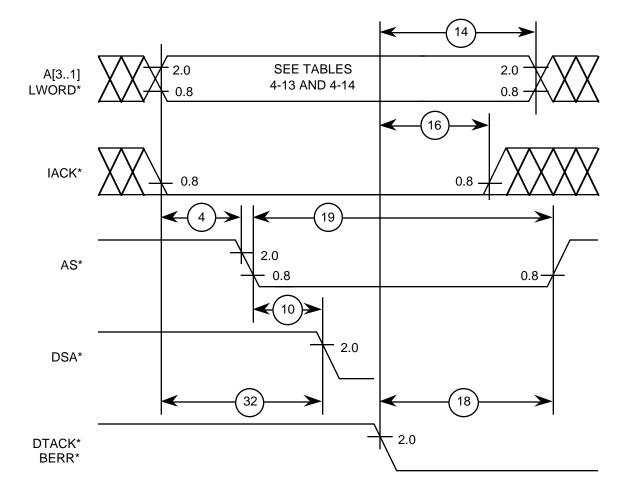

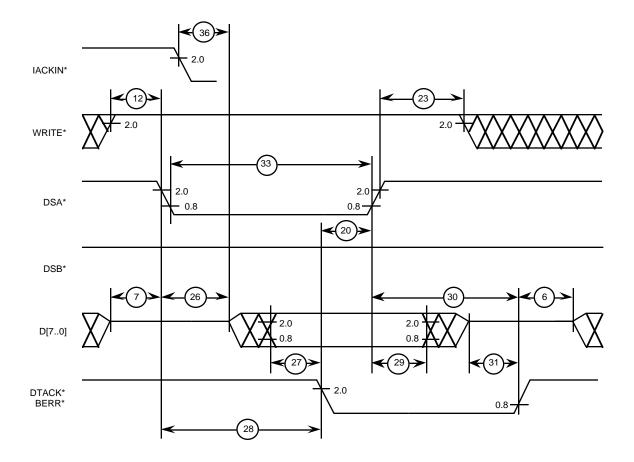

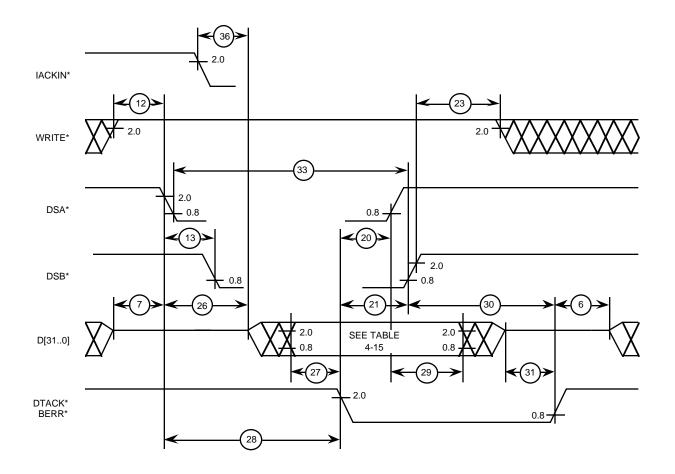

| Figure 4 - 16 | Interrupt Handler And InterrupterInterrupter Selection Timing  | 180  |

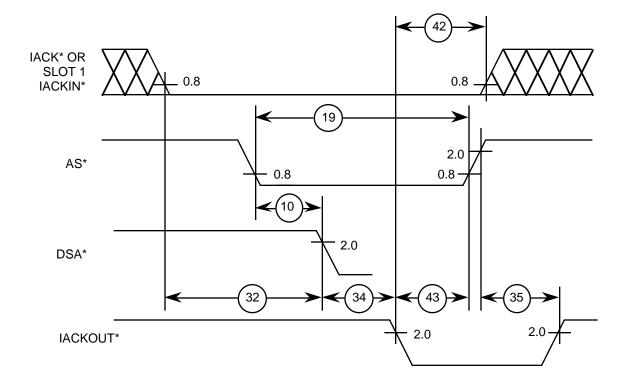

| Figure 4 - 17 | IACK Daisy-Chain DriverInterrupter Selection Timing            |      |

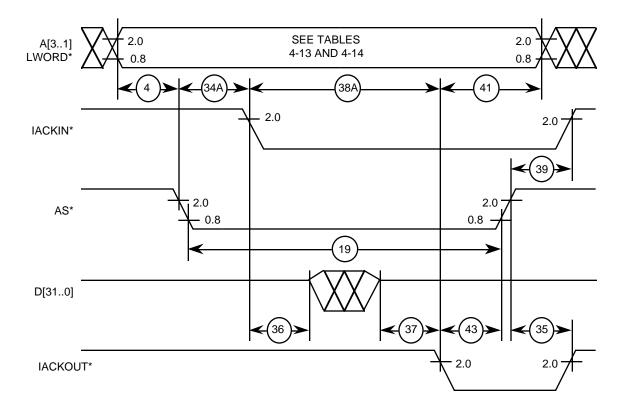

| Figure 4 - 18 | Participating InterrupterInterrupter Selection Timing          |      |

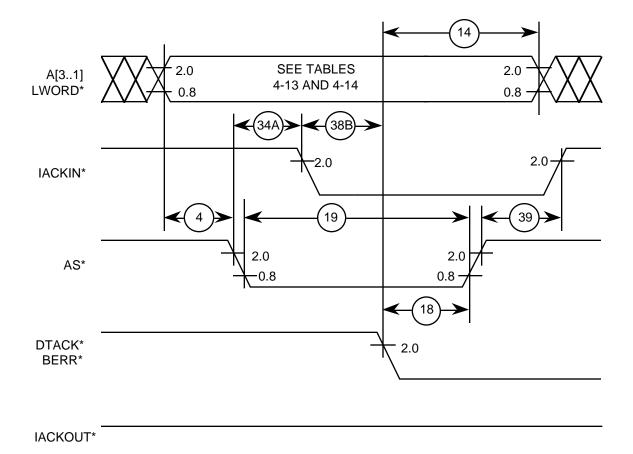

|               | Responding Interrupter-Interrupter Selection Timing            | 102  |

| Figure 4 - 19 |                                                                |      |

| Figure 4 - 20 | Interrupt HandlerStatus/Id Transfer Timing                     | 104  |

| Figure 4 - 21 | Interrupt HandlerStatus/Id Transfer Timing                     | 105  |

| Figure 4 - 22 | Responding InterrupterStatus/Id Transfer Timing                |      |

| Figure 4 - 23 | Responding InterrupterStatus/Id Transfer Timing                | .196 |

| Figure 4 - 24 | IACK Daisy-Chain Driver, Responding Interrupter, And           | 107  |

|               | Participating Interrupter IACK Daisy-Chain Inter-Cycle Timing  |      |

| Figure 5 - 1  | Utility Bus Block Diagram                                      |      |

| Figure 5 - 2  | System Clock Driver Timing                                     | 201  |

| Figure 5 - 3  | Block Diagram Of Power Monitor Module                          |      |

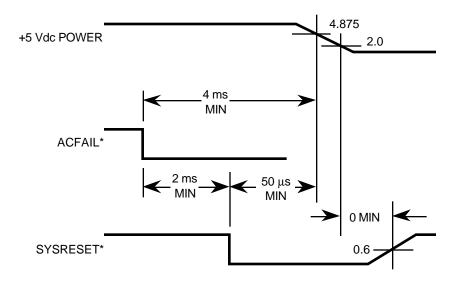

| Figure 5 - 4  | Power Monitor Power Failure Timing                             | 203  |

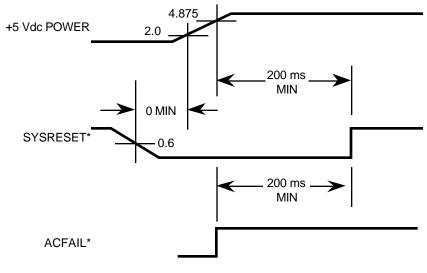

| Figure 5 - 5  | Power Monitor System Restart Timing                            |      |

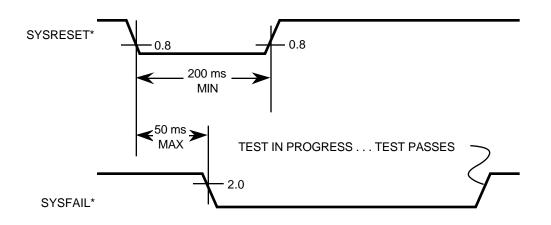

| Figure 5 - 6  | SYSRESET* and SYSFAIL* Timing Diagram                          | 206  |

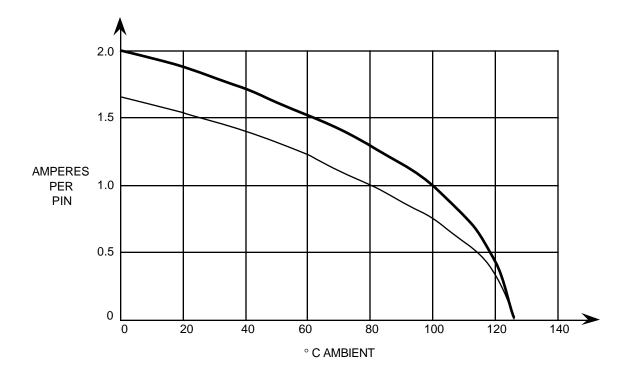

| Figure 5 - 7  | Current Rating For Power Pins                                  | 208  |

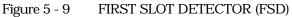

| Figure 5 - 9  | First Slot Detector (FSD)                                      | 215  |

| Figure 6 - 1  | VMEbus Signal Levels                                           | 220  |

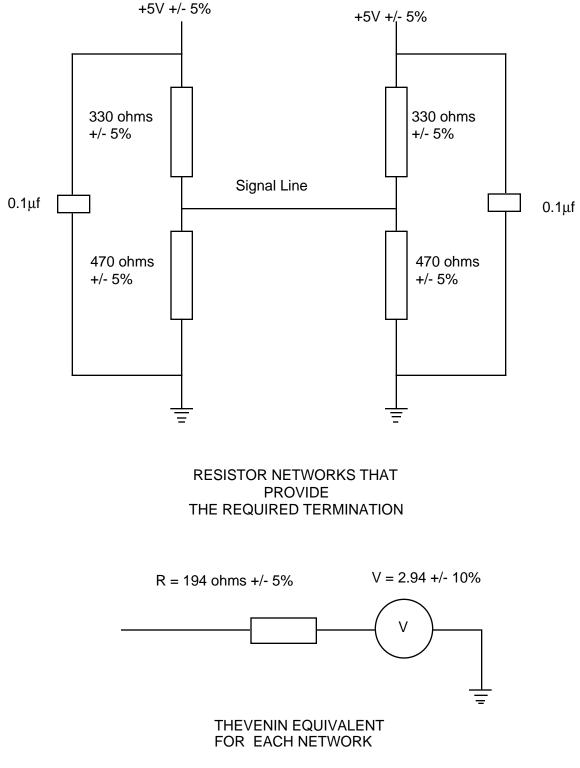

| Figure 6 - 2  | Standard Bus Termination                                       | 227  |

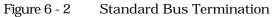

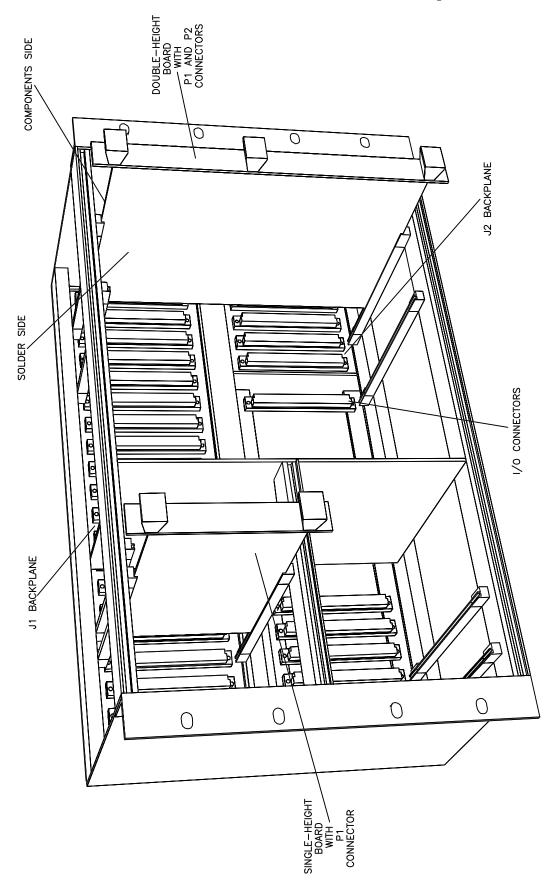

| Figure 7 - 1  | Subrack with Mixed Board Sizes                                 |      |

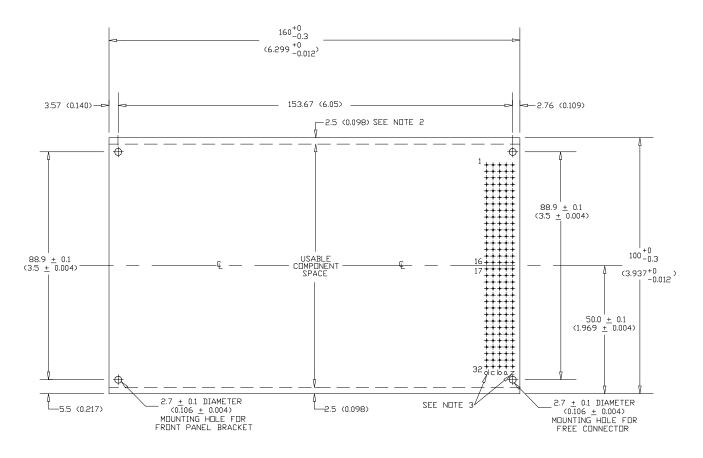

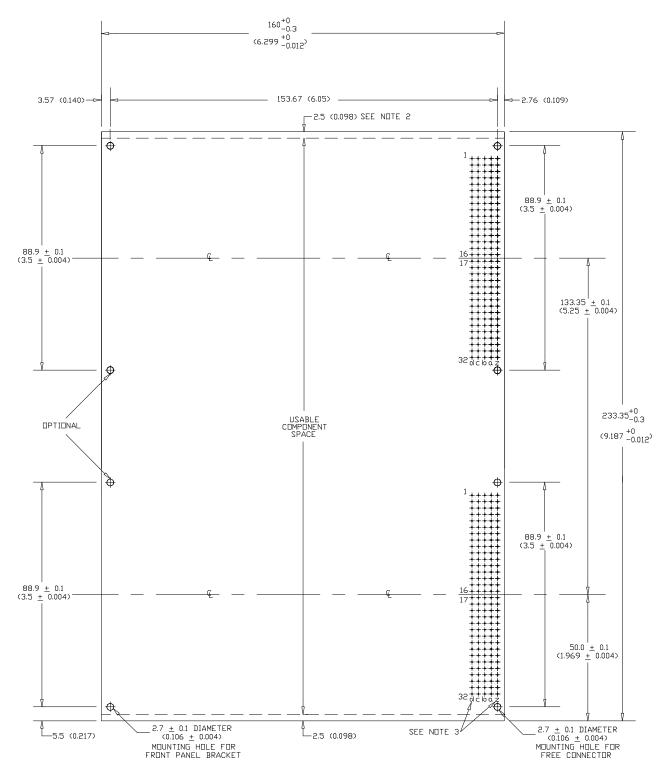

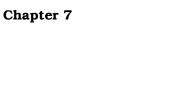

| Figure 7 - 2  | Single Height Board                                            |      |

| Figure 7 - 3  | Double Height Board                                            |      |

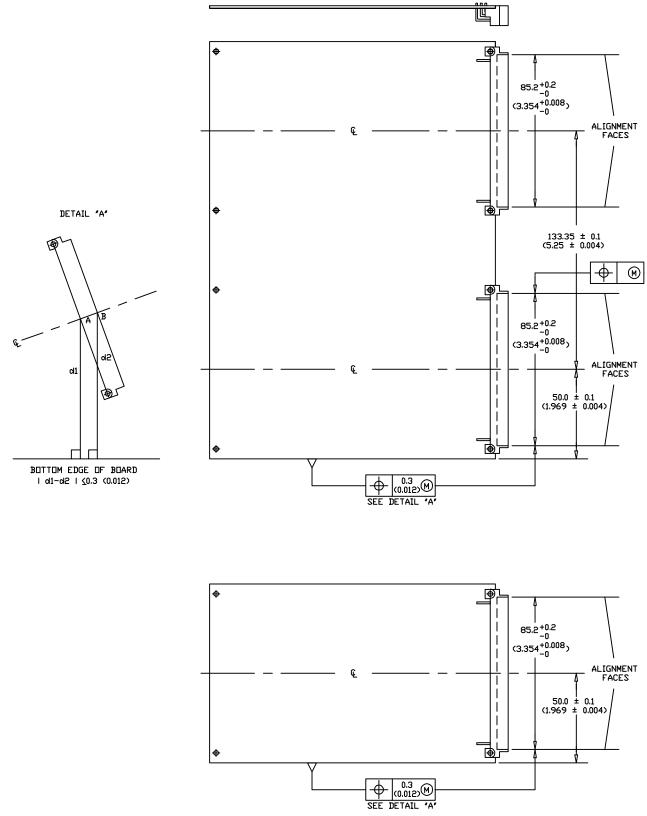

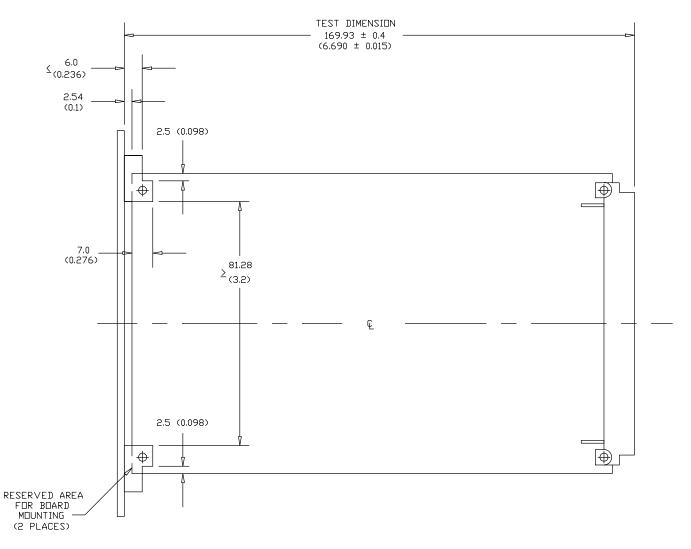

| Figure 7 - 4  | Connector Position On Single And Double Height Boards          | 251  |

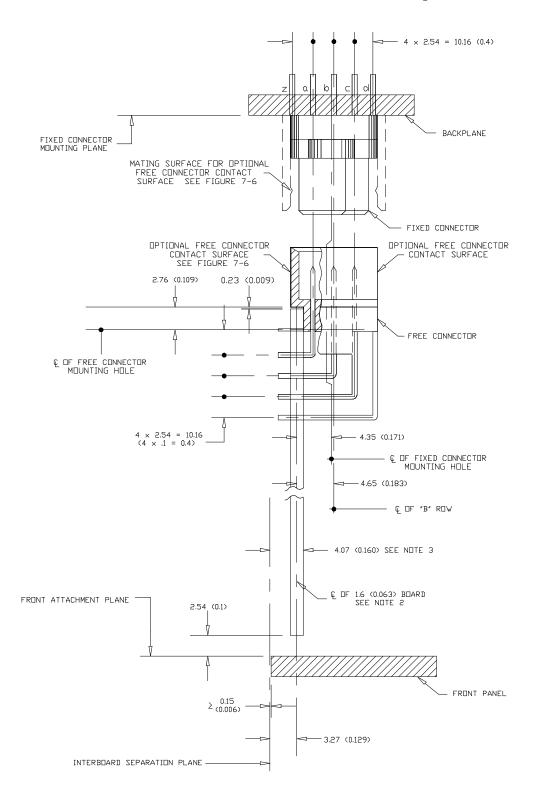

| Figure 7 - 5  | Cross Sectional View Of Board, Connector, Backplane, And Front |      |

|               | Panel                                                          |      |

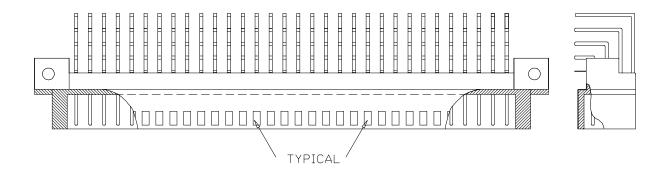

| Figure 7 - 6  | Optional Enhanced DIN Connector                                | 253  |

| Figure 7 - 7  | Component Height, Lead Length And Board Warpage                |      |

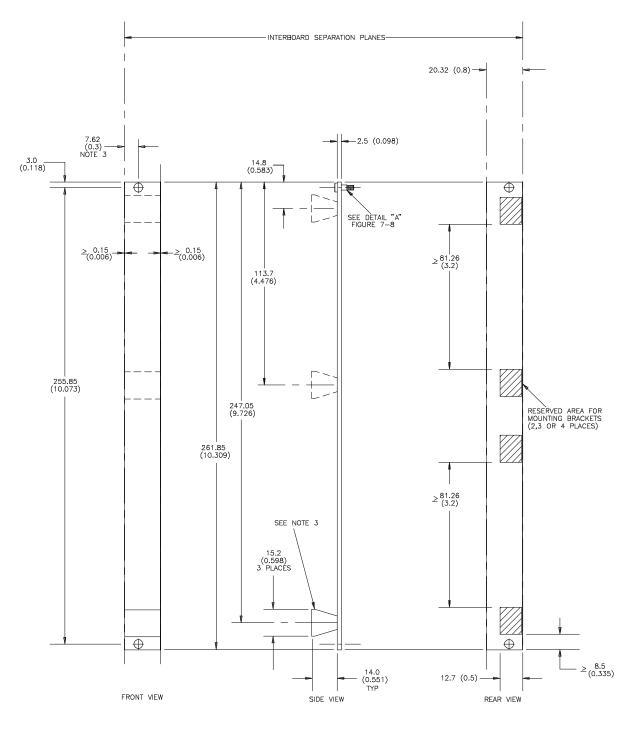

| Figure 7 - 8  | Single Height, Single Width Front Panel                        | 255  |

| Figure 7 - 9  | Double Height, Single Width Front Panel                        |      |

| Figure 7 - 10 | Front Panel Mounting Brackets And Dimensions Of Single         |      |

| 0             | Height Boards                                                  | 257  |

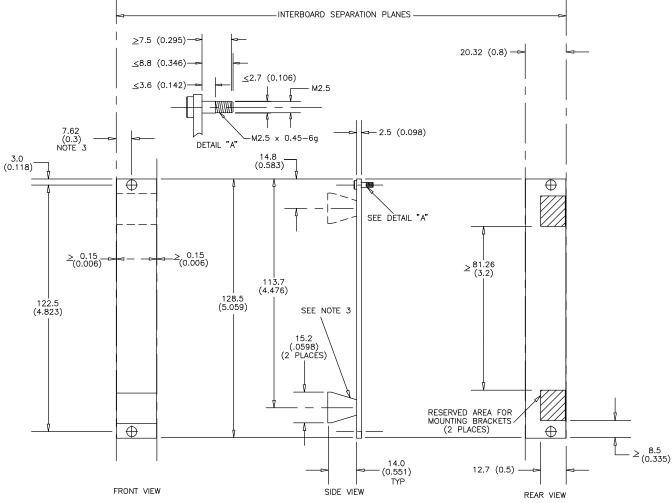

| Figure 7 - 11 | Front Panel Mounting Brackets And Dimensions Of Double         |      |

| 0             | Height Boards                                                  | 258  |

| Figure 7 - 12 | Single Height Filler Panel                                     |      |

| Figure 7 - 13 | Double Height Filler Panel                                     |      |

| Figure 7 - 14 | Detailed Dimensions of a J1 and a J2 Backplane                 |      |

| Figure 7 - 15 | Detailed Dimensions of a J1/J2 Backplane                       |      |

| Figure 7 - 16 | "Off-Board Type" Backplane Termination                         |      |

| Figure 7 - 17 | "On-Board Type" Backplane Termination                          |      |

| Figure 7 - 18 | 21 Slot Sub Rack                                               |      |

| Figure 7 - 19 | Board Guide Detail.                                            |      |

| 0             |                                                                |      |

## List of Tables

| Table 2 - 1       | The Eight Categories Of Byte Locations                                                                                 | 16   |

|-------------------|------------------------------------------------------------------------------------------------------------------------|------|

| Table 2 - 28      | Address Alignment on Bus                                                                                               | 16   |

| Table 2 - 2       | Signal Levels During Data Transfers                                                                                    | 18   |

| Table 2 - 3       | Address Modifier Codes                                                                                                 | 21   |

| Table 2 - 4       | Use Of Data Lines To Move Data During Nonmultiplexed Data                                                              |      |

| <b>T</b> 1 1 2 22 | Transfers.                                                                                                             | 24   |

| Table 2 - 29      | Use Of The Address And Data Lines For Muliplexed Data Cycles                                                           | 25   |

| Table 2 - 5       | RULES And PERMISSIONS That Specify The Use Of The Dotted                                                               |      |

|                   | Lines By The Various Types Of Masters                                                                                  | 30   |

| Table 2 - 6       | Slaves - RULES And PERMISSIONS That Specify The Use of The                                                             |      |

| Table 2 - 7       | Use Of The BTO() Mnemonic.                                                                                             | 34   |

| Table 2 - 8       | Location Monitors - RULES And PERMISSIONS That Specify The<br>Use Of The Dotted Lines By The Various Types Of Location |      |

|                   | Monitors                                                                                                               |      |

| Table 2 - 9       | Mnemonics That Specify Addressing Capabilities                                                                         | 38   |

| Table 2 - 10      | Mnemonics That Specify Basic Data Transfer Capabilities                                                                |      |

| Table 2 - 11      | Mnemonics That Specify Block Transfer Capabilities                                                                     |      |

| Table 2 - 12      | The Mnemonic That Specifies Read-Modify-Write Capabilities                                                             | 46   |

| Table 2 - 13      | Transferring 32 Bits Of Data Using Multiple-Byte Transfer Cycles                                                       |      |

| Table 2 - 14      | Transferring 16 Bits Of Data Using Multiple-Byte Transfer Cycles                                                       |      |

| Table 2 - 15      | Mnemonic That Specifies Unaligned Transfer Capability                                                                  | 50   |

| Table 2 - 16      | Mnemonics That Specify Address Only Capability                                                                         | 51   |

| Table 2 - 30      | Configuration ROM / Control & Status Registers                                                                         | 54   |

| Table 2 - 31      | Control And Status Register Base Definition                                                                            | 54   |

| Table 2 - 32      | Configuration ROM Definition                                                                                           | 55   |

| Table 2 - 17      | Timing Diagrams That Define Master, Slave, And Location                                                                | ~ ~  |

|                   | Monitor Operation (See Table 2-22 For Timing Values)                                                                   |      |

| Table 2 - 18      | Definitions Of Mnemonics Used In Tables 2 - 19, 2 - 20, And 2 - 21                                                     |      |

| Table 2 - 19      | Use Of The Address And Data Lines To Select A Byte Group                                                               | 75   |

| Table 2 - 20      | Use of DS1*, DS0*, A1, A2, and LWORD* During the Address Phase of the                                                  | 76   |

| Table 2 - 21      | Use Of The Data Lines To Transfer Data                                                                                 |      |

| Table 2 - 22      | Master, Slave, And Location Monitor Timing Parameters                                                                  |      |

| Table 2 - 23      | Bus-Timer Timing Parameters                                                                                            |      |

| Table 2 - 24      | Master, Timing RULEs and OBSERVATIONs                                                                                  |      |

| Table 2 - 25      | Slave, Timing RULEs and OBSERVATIONs                                                                                   | 89   |

| Table 2 - 26      | Location Monitor, Timing OBSERVATIONs                                                                                  | 93   |

| Table 2 - 27      | Bus Timer, Timing RULEs                                                                                                | 94   |

| Table 4 - 1       | RULES And PERMISSIONS That Specify The Use Of The Dotted                                                               |      |

|                   | Lines                                                                                                                  | .153 |

| Table 4 - 2       | RULES And PERMISSIONS That Specify The Use Of The Dotted                                                               | .155 |

| Table 4 - 3       | Use Of The IH() Mnemonic To Specify Interrupt                                                                          | .158 |

| Table 4 - 4       | Use Of The I() Mnemonic To Specify Interrupt Request                                                                   |      |

| Table 4 - 5       | Mnemonics That Specify Status/Id Transfer Capabilities                                                                 | .159 |

| Table 4 - 6       | Mnemonics That Specify Interrupt Request Release Capabilities                                                          |      |

| Table 4 - 7       | 3-Bit Interrupt Acknowledge Code                                                                                       |      |

| Table 4 - 8       | Timing Diagrams That Define Interrupt Handler And                                                                      | .176 |

| Table 4 - 9       | Timing Diagrams That Define IACK Daisy-Chain Driver                                                                    |      |

|                   | Operation                                                                                                              | .177 |

| Table 4 - 10      | Timing Diagrams That Define Participating Interrupter<br>Operation                                                     |      |

| Table 4 - 11      | Timing Diagrams That Define Responding Interrupter Operation                                                           | .177 |

| Table 4 - 12 | Definitions Of Mnemonics Used In Tables 4-13, 4-14, And 4-15 | 178 |

|--------------|--------------------------------------------------------------|-----|

| Table 4 - 13 | Use Of Addressing Lines During Interrupt Acknowledge Cycles  | 179 |

| Table 4 - 14 | Use Of The DS1*, DS0*, LWORD*, And WRITE* Lines During       | 179 |

| Table 4 - 15 | Use of the data bus lines to transfer the Status/Id          |     |

| Table 4 - 16 | Interrupt Handler, Interrupter, And IACK DAISY-CHAIN         | 180 |

| Table 4 - 17 | Interrupt Handler, Timing RULEs And OBSERVATIONs             |     |

| Table 4 - 18 | Interrupter, Timing RULEs And OBSERVATIONs                   |     |

| Table 4 - 19 | IACK Daisy-Chain Driver, Timing RULEs And OBSERVATIONs       | 188 |

| Table 5 - 1  | Module Drive During Power-Up and Power-Down Sequences        | 205 |

| Table 6 - 1  | Bus Voltage Specification                                    | 218 |

| Table 6 - 2  | Bus Driving And Receiving Requirements                       |     |

| Table 6 - 3  | Bus Driver Summary                                           |     |

| Table 7 - 1  | J1/P1 Pin Assignments                                        |     |

| Table 7 - 2  | J2/P2 Pin Assignments                                        |     |

### Abstract

The VME64 specification establishes a framework for 8-, 16-, 32, and 64-bit parallelbus computer architectures that can implement single and multiprocessor systems. It is based on the VMEbus specification released by the VMEbus Manufacturers Group (now VITA) in August of 1982. This bus includes the initial four basic subbuses: (1) data transfer bus, (2) priority interrupt bus, (3) arbitration bus, and (4) utility bus. Other architectures with other subbuses are possible within this VME framework.

The data transfer bus will support 8-, 16-, 32-, and 64-bit data transfers in multiplexed and non multiplexed form. The transfer protocols are asynchronous with varying degrees of handshaking dependent on the speeds required. The priority interrupt subsystem provides real-time interrupt services to the system. The allocation of bus mastership is performed by the arbitration subsystem which allows the implementation of several prioritization algorithms. The utility bus provides the system with power plus power-up and power-down synchronization. The mechanical specifications of boards, backplanes, subracks, and enclosures are based on IEC 297 and IEEE 1101.1 specifications, also known as the Eurocard form factor. Additional standards exist that can be used as sub-busses to this architecture for data transfer transactions, peripheral interfaces and intra-crate communications among compatible modules.

### FOREWORD

#### (This foreword is not part of ANSI/VITA 1-1994.)

The architectural concepts of VMEbus are based on the VERSAbus developed by Motorola in the late 1970s. Motorola's European Microsystems group in Munich, West Germany proposed the development of a VERSAbus-like product line of computers and controllers based on the Eurocard mechanical standard. To demonstrate the concept, Max Loesel and Sven Rau developed three prototype boards: (1) a 68000 CPU card, (2) a dynamic memory card, and (3) a static memory card. They named the new bus VERSAbus-E, which was later renamed "VME" by Lyman Hevle, then VP of the Motorola Microsystems Operation (and later the founder of VITA). VME is the acronym for VERSA-module Europe. Motorola, Mostek, and Signetics agreed to jointly develop and support the new bus architecture in early 1981.

John Black of Motorola, Craig McKenna of Mostek, and Cecil Kaplinsky of Signetics developed the first draft of the VMEbus specification. In October of 1981, at the Systems 81 trade show in Munich, West Germany, Motorola, Mostek, and Signetics announced their joint support for VMEbus, and placed Revision A of the specification in the public domain.

In August of 1982, Revision B of the VMEbus specification was published by the newly formed VMEbus Manufacturers Group (now VITA). This new revision refined the electrical specifications for the signal line drivers and receivers, and also brought the mechanical specifications more in line with the developing IEC 297 standard, the formal specifications for Eurocard mechanical formats.

In the latter part of 1982, the French delegation of the International Electrotechnical Commission (IEC) proposed Revision B of the VMEbus specification as an international standard. The IEC SC47B subcommittee nominated Mira Pauker of Philips, France, as the chairperson of an editorial committee, formally starting international standardization of the VMEbus.

In March of 1983, the IEEE Microprocessor Standards Committee (MSC) requested authorization to establish a working group to standardize the VMEbus in the US. This request was approved by the IEEE Standards Board, and the P1014 Working Group was established. Wayne Fischer was appointed first chairman of the working group. John Black served as chairman of the P1014 Technical Subcommittee.

The IEC, IEEE, and VMEbus Manufacturers Group (now VITA) distributed copies of Revision B for comment, and received requests for changes to the document as a result. These comments made it clear that it was time to go forward past revision B. In December of 1983, a meeting was held that included John Black, Mira Pauker, Wayne Fischer, and Craig McKenna. It was agreed that a revision C should be created, and that it should take into consideration all comments received by the three organizations. John Black and Shlomo Pri-Tal of Motorola incorporated the changes from all sources into a common document. The VMEbus Manufacturers Group (now VITA) labeled the document Revision C.1 and placed it in the public domain. The IEEE labeled it P1014 Draft 1.2, and the IEC labeled it IEC 821 Bus. Subsequent ballots in the IEEE P1014 group and in the MSC resulted in more comments, and required that the IEEE P1014 draft be updated. This work resulted in the ANSI/IEEE 1014-1987 specification.

In 1989, John Peters of Performance Technologies, Inc. (Rochester, NY) developed the initial concept of VME64: multiplexing address and data lines (A64/D64) on the VMEbus. This concept was shown for the first time in 1989 and placed in the VITA Technical Committee in 1990 as a performance enhancement to the VMEbus specification. In 1991, the PAR (Project Authorization Request) for P1014R (revisions to the VMEbus specification) was granted by the IEEE. Ray Alderman, Technical Director of VITA, co-chaired the activity with Kim Clohessy of DY 4 Systems (Nepean, Ontario, Canada).

At the end of 1992, the additional enhancements to VMEbus (A40/D32, Locked Cycles, Rescinding DTACK\*, Autoslot-ID, Auto System Controller, and enhanced DIN connector mechanicals) required more work to complete this document. In 1992, the VITA Technical Committee suspended work with the IEEE and sought accreditation as a standards developer organization (SDO) with the American National Standards Institute. The original IEEE Par P1014R was subsequently withdrawn by the IEEE. The VITA Technical Committee returned to using the public domain VMEbus C.1 specification as its base level document to which it added new enhancements. This enhancement work was undertaken entirely by the VITA Technical Committee resulting in this document. The tremendous undertaking of the document editing was accomplished by Kim Clohessy of DY 4 Systems, the technical co-chair of the activity with great help from Frank Hom who created the mechanical drawings, and with exceptional contributions by each chapter editor.

Additional enhancements proposed to the VME64 Subcommittee have been placed in another VITA subcommittee: the VME64 Extensions Document. Two other activities began in late 1992: (1) BLLI (VMEbus Board-level Live Insertion Specifications), and (2) VSLI (VMEbus System-level Live Insertion with Fault Tolerance).

New activities begun in 1993 using the base-VME architecture involve the implementation of high-speed serial and parallel sub-buses for use as I/O interconnections and data mover subsystems. These architectures can be used as message switches, routers, and small multiprocessor parallel architectures.

VITA's application for recognition as an accredited standards developer organization of ANSI (American National Standards Institute) was granted in June 1993. Numerous other documents, including mezzanine, P2, and serial bus standards, have been placed with VITA as the Public Domain Administrator of these technologies.

## VMEBUS Specification Genealogy

| VMEbus         | Revision B and C.1 (Public Domain)                                                                |

|----------------|---------------------------------------------------------------------------------------------------|

| IEEE 1014-1987 | Versatile Backplane Bus VMEbus                                                                    |

| VITA 1-1994    | VME64 Specification                                                                               |

| IEEE 1096-1988 | VSBbus Specification (IEEE)                                                                       |

| IEC 821        | A Bus Specification                                                                               |

| IEEE 1101.1    | IEEE Standard for Mechanical Core Specifications for<br>Microcomputers Using IEC 603-2 Connectors |

| IEEE 1101.2    | IEEE Standard for Mechanical Core Specification for<br>Conduction-Cooled Eurocards                |

This standard was constructed through the many hours of hard work by the members of the VME64 Subcommittee (of the VITA Technical Committee) and the commitment of their companies to this standard.

| NAME                                                                                                                                                                              | COMPANY                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ray Alderman                                                                                                                                                                      | PEP Modular Computers                                                                                                                                                                                                                     |

| Michael Humphrey                                                                                                                                                                  | VITA                                                                                                                                                                                                                                      |

| John Rynearson                                                                                                                                                                    | VITA                                                                                                                                                                                                                                      |

| Martin Blake                                                                                                                                                                      | BICC-VERO UK                                                                                                                                                                                                                              |

| Kim Clohessy                                                                                                                                                                      | DY 4 Systems, Inc.                                                                                                                                                                                                                        |

| Jing Kwok                                                                                                                                                                         | DY 4 Systems, Inc.                                                                                                                                                                                                                        |

| Clarence Peckham                                                                                                                                                                  | Heurikon Corporation                                                                                                                                                                                                                      |

| Dennis Terry                                                                                                                                                                      | Heurikon Corporation                                                                                                                                                                                                                      |

| Wayne Fischer                                                                                                                                                                     | Force Computers Inc.                                                                                                                                                                                                                      |

| Jack Regula                                                                                                                                                                       | Consultant                                                                                                                                                                                                                                |

| Tad Kubic                                                                                                                                                                         | Dawn VME Products, Inc.                                                                                                                                                                                                                   |

| Will Hamsher                                                                                                                                                                      | AMP, Inc.                                                                                                                                                                                                                                 |

| Doug Reubendall                                                                                                                                                                   | AMP, Inc.                                                                                                                                                                                                                                 |

| William Mahusen                                                                                                                                                                   | Performance Technologies, Inc.                                                                                                                                                                                                            |

|                                                                                                                                                                                   |                                                                                                                                                                                                                                           |

| Thanos Mentzelopoulos                                                                                                                                                             | Ironics, Inc.                                                                                                                                                                                                                             |

| Thanos Mentzelopoulos<br>Joel Silverman                                                                                                                                           | Ironics, Inc.<br>Radstone Technology Corp.                                                                                                                                                                                                |

|                                                                                                                                                                                   | ·                                                                                                                                                                                                                                         |

| Joel Silverman                                                                                                                                                                    | Radstone Technology Corp.                                                                                                                                                                                                                 |

| Joel Silverman<br>Colin Davies                                                                                                                                                    | Radstone Technology Corp.<br>Radstone Technology UK                                                                                                                                                                                       |

| Joel Silverman<br>Colin Davies<br>Frank Hom                                                                                                                                       | Radstone Technology Corp.<br>Radstone Technology UK<br>Electronic Solutions                                                                                                                                                               |

| Joel Silverman<br>Colin Davies<br>Frank Hom<br>Keith Burgess                                                                                                                      | Radstone Technology Corp.<br>Radstone Technology UK<br>Electronic Solutions<br>Mizar                                                                                                                                                      |

| Joel Silverman<br>Colin Davies<br>Frank Hom<br>Keith Burgess<br>John Black                                                                                                        | Radstone Technology Corp.<br>Radstone Technology UK<br>Electronic Solutions<br>Mizar<br>Micrology PBT                                                                                                                                     |

| Joel Silverman<br>Colin Davies<br>Frank Hom<br>Keith Burgess<br>John Black<br>Greg Hill                                                                                           | Radstone Technology Corp.<br>Radstone Technology UK<br>Electronic Solutions<br>Mizar<br>Micrology PBT<br>Hewlett-Packard Co.                                                                                                              |

| Joel Silverman<br>Colin Davies<br>Frank Hom<br>Keith Burgess<br>John Black<br>Greg Hill<br>Sam Babb                                                                               | Radstone Technology Corp.<br>Radstone Technology UK<br>Electronic Solutions<br>Mizar<br>Micrology PBT<br>Hewlett-Packard Co.<br>Hewlett Packard Co.                                                                                       |

| Joel Silverman<br>Colin Davies<br>Frank Hom<br>Keith Burgess<br>John Black<br>Greg Hill<br>Sam Babb<br>Ben LaPointe                                                               | Radstone Technology Corp.<br>Radstone Technology UK<br>Electronic Solutions<br>Mizar<br>Micrology PBT<br>Hewlett-Packard Co.<br>Hewlett Packard Co.<br>Motorola GEG                                                                       |

| Joel Silverman<br>Colin Davies<br>Frank Hom<br>Keith Burgess<br>John Black<br>Greg Hill<br>Sam Babb<br>Ben LaPointe<br>Chau Pham                                                  | Radstone Technology Corp.<br>Radstone Technology UK<br>Electronic Solutions<br>Mizar<br>Micrology PBT<br>Hewlett-Packard Co.<br>Hewlett Packard Co.<br>Motorola GEG<br>Motorola MCG                                                       |

| Joel Silverman<br>Colin Davies<br>Frank Hom<br>Keith Burgess<br>John Black<br>Greg Hill<br>Sam Babb<br>Ben LaPointe<br>Chau Pham<br>Mac Rush                                      | Radstone Technology Corp.<br>Radstone Technology UK<br>Electronic Solutions<br>Mizar<br>Micrology PBT<br>Hewlett-Packard Co.<br>Hewlett Packard Co.<br>Motorola GEG<br>Motorola MCG                                                       |

| Joel Silverman<br>Colin Davies<br>Frank Hom<br>Keith Burgess<br>John Black<br>Greg Hill<br>Sam Babb<br>Ben LaPointe<br>Chau Pham<br>Mac Rush<br>Mike Hasenfratz                   | Radstone Technology Corp.<br>Radstone Technology UK<br>Electronic Solutions<br>Mizar<br>Micrology PBT<br>Hewlett-Packard Co.<br>Hewlett Packard Co.<br>Motorola GEG<br>Motorola MCG<br>Motorola MCG<br>Micro Memory, Inc.                 |

| Joel Silverman<br>Colin Davies<br>Frank Hom<br>Keith Burgess<br>John Black<br>Greg Hill<br>Sam Babb<br>Ben LaPointe<br>Chau Pham<br>Mac Rush<br>Mike Hasenfratz<br>Richard DeBock | Radstone Technology Corp.<br>Radstone Technology UK<br>Electronic Solutions<br>Mizar<br>Micrology PBT<br>Hewlett-Packard Co.<br>Hewlett Packard Co.<br>Motorola GEG<br>Motorola MCG<br>Motorola MCG<br>Micro Memory, Inc.<br>Matrix Corp. |

#### Table of Contents

Dr. Chris Eck Mike Thompson Eike Waltz Tom Baillio Steve Corbesero Dave Horton Mike Maas Mike Munroe CERN-Geneva Schroff, Inc. Schroff, Inc. Mercury Computer Systems, Inc. Mupac Corp. Cypress Semiconductor Cypress Semiconductor Hybricon Corp.

The following are acknowledged for their extra contributions as chapter editors.

Kim Clohessy Wayne Fischer Chau Pham Frank Hom Richard DeBock Jing Kwok Mike Hasenfratz DY-4 Systems Inc. Force Computers, Inc. Motorola MCG Electronic Solutions Matrix Corp. DY 4 Systems, Inc. Micro Memory, Inc.

#### Canvass Ballot

Consensus for this standard was achieved by use of the Canvass Method.

The following organizations, recognized as having an interest in the standardization of VME64, participated in the Canvass Ballot process. Inclusion in this list does not necessarily imply that the organization concurred with the submittal of the proposed standard to ANSI.

767 AWACS Adept Technology AMP **AT&T Bell Laboratories Berg Electronics** Bit 3 Computer CERN CSPI **Cypress Semiconductor Dawn VME Products Dialogic Corporation** Digital Equipment Corp. DY 4 Systems **Electronic Solutions Force Computers** Harting Elektronik Heurikon Corporation Hewlett-Packard Hughes Aircraft Company Hybricon Corporation IBM **IXTHOS** Loral Western Devel. Lab Los Alamos Nat'l Lab Matrix Corporation Micro Memory Micrology **MITRE** Corporation Motorola Computer Group Mupac Corporation Newbridge Microsystems Object Technology Inc. **PEP Modular Computers** Philips Ind. Automation Picosoft **Radstone Technology** Schroff

Technology Consulting Texas Instruments VERO Electronics VITA VME MEMBER Winchester Electronics

## Chapter 1

## Introduction to the VMEBUS Specification

#### 1.1 VMEBUS Specification Objectives

The VMEbus specification defines an interfacing system used to interconnect microprocessors, data storage, and peripheral control devices in a closely coupled hardware configuration. The system has been conceived with the following objectives:

- a. To allow communication between devices on the VMEbus without disturbing the internal activities of other devices interfaced to the VMEbus.

- b. To specify the electrical and mechanical system characteristics required to design devices that will reliably and unambiguously communicate with other devices interfaced to the VMEbus.

- c. To specify protocols that precisely define the interaction between the VMEbus and devices interfaced to it.

- d. To provide terminology and definitions that describe system protocol.

- e. To allow a broad range of design latitude so that the designer can optimize cost and/or performance without affecting system compatibility.

- f. To provide a system where performance is primarily device limited, rather than system interface limited.

- 1.2 VMEBUS Interface System Elements

#### 1.2.1 Basic Definitions

The VMEbus structure can be described from two points of view: its mechanical structure and its functional structure. The mechanical specification describes the physical dimensions of subracks, backplanes, front panels, plug-in boards, etc. The VMEbus functional specification describes how the bus works, what functional modules are involved in each transaction, and the rules which govern their behavior. This section provides informal definitions for some basic terms used to describe both the mechanical and the functional structure of the VMEbus.

#### 1.2.1.1 Terms Used to Describe the VMEbus Mechanical Structure

VMEbus Backplane — A printed circuit (PC) board with 96 or 160 pin connectors and signal paths that bus the connector pins. Some VMEbus systems have a single PC board, called the J1 backplane. It provides the signal paths needed for basic operation. Other VMEbus systems also have an optional second PC board, called a J2 backplane. It provides the additional 96 or 160 pin connectors and signal paths needed for wider data and address transfers. Still others have a single PC board that provides the signal conductors of both the J1 and J2 backplanes.

Board — A printed circuit (PC) board, its collection of electronic components, with either one or two 96 or 160 pin connectors that can be plugged into VMEbus backplane connectors.

Slot — A position where a board can be inserted into a VMEbus backplane. If the VMEbus system has both a J1 and a J2 backplane (or a combination J1/J2 backplane) each slot provides a pair of 96 or 160 pin connectors. If the system has only a J1 backplane, then each slot provides a single 96 or 160 pin connector.

Subrack — A rigid framework that provides mechanical support for boards inserted into the backplane, ensuring that the connectors mate properly and that adjacent boards do not contact each other. It also guides the cooling airflow through the system, and ensures that inserted boards do not disengage themselves from the backplane due to vibration or shock.

1.2.1.2 Terms Used to Describe the VMEbus Functional Structure

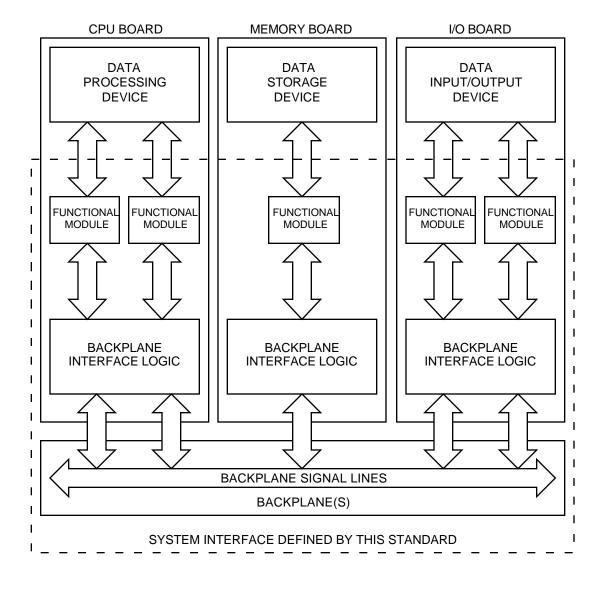

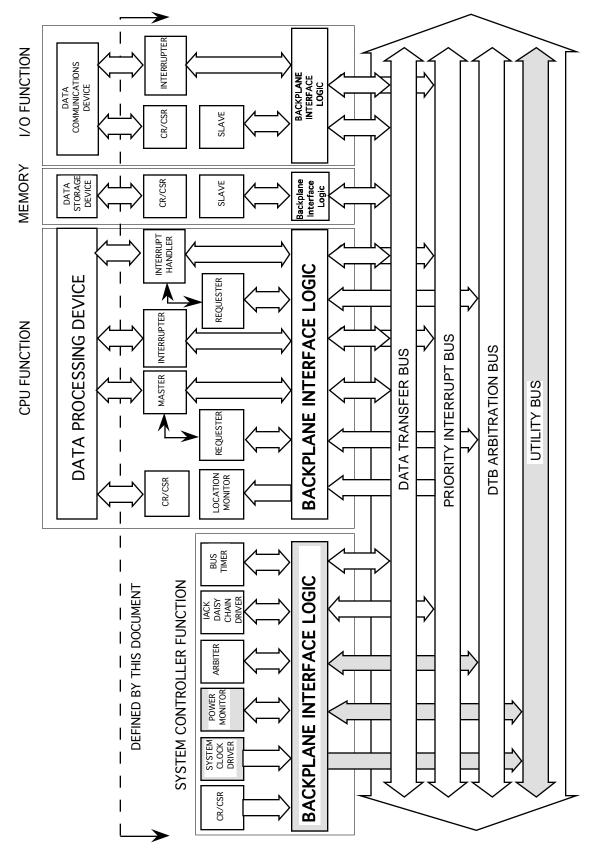

Figure 1-1 shows a simplified block diagram of the functional structure, including the VMEbus signal lines, backplane interface logic, and functional modules.

Backplane Interface Logic — Special interface logic that takes into account the characteristics of the backplane: its signal line impedance, propagation time, termination values, etc. The VMEbus specification prescribes certain rules for the design of this logic based on the maximum length of the backplane and its maximum number of board slots.

Functional Module — A collection of electronic circuitry that resides on one VMEbus board and works together to accomplish a task.

Data Transfer Bus — One of the four buses provided by the VMEbus backplane. The Data Transfer Bus allows Masters to direct the transfer of binary data between themselves and Slaves. (Data Transfer Bus is often abbreviated DTB.)

Data Transfer Bus Cycle — A sequence of level transitions on the signal lines of the DTB that result in the transfer of an address or an address and data between a Master and a Slave. The Data Transfer Bus cycle is divided into two portions, the address broadcast and then zero or more data transfers. There are 34 types of Data Transfer Bus cycles. They are defined later in this chapter.

Master — A functional module that initiates DTB cycles in order to transfer data between itself and a Slave module.

Figure 1 - 1 System Elements Defined By This Document

3

Slave — A functional module that detects DTB cycles initiated by a Master and, when those cycles specify its participation, transfers data between itself and the Master.

Location Monitor - A functional module that monitors data transfers over the DTB in order to detect accesses to the locations it has been assigned to watch. When an access to one of these assigned locations occurs, the Location Monitor generates an on-board signal.

Bus Timer — A functional module with a preset time-out period which terminates the DTB cycle if a transfer exceeds the time-out period. Without this module, if the Master tries to transfer data to or from a nonexistent Slave location it might wait forever. The Bus Timer prevents this by terminating the cycle.

Priority Interrupt Bus — One of the four buses provided by the VMEbus backplane. The Priority Interrupt Bus allows Interrupter modules to send interrupt requests to Interrupt Handlers.

Interrupter — A functional module that generates an interrupt request on the Priority Interrupt Bus and then provides Status/ID information when the Interrupt Handler requests it.

Interrupt Handler - A functional module that detects interrupt requests generated by Interrupters and responds to those requests by asking for Status/ID information.

Status/Id -- An eight, sixteen, or thirty two bit value returned by an interrupter to an interrupt handler during an interrupt acknowledge cycle.

Daisy-Chain — A special type of VMEbus signal line that is used to propagate a signal level from board to board, starting with the first slot and ending with the last slot. There are four bus grant daisy-chains and one interrupt acknowledge daisy-chain on the VMEbus.

IACK Daisy-Chain Driver — A functional module which activates the interrupt acknowledge daisy-chain whenever an Interrupt Handler acknowledges an interrupt request. This daisy-chain ensures that only one Interrupter will respond with its STATUS/ID when more than one has generated an interrupt request.

Arbitration Bus — One of the four buses provided by the VMEbus backplane. This bus allows an Arbiter module and several Requester modules to coordinate use of the DTB.

Requester — A functional module that resides on the same board as a Master or Interrupt Handler and requests use of the DTB whenever its Master or Interrupt Handler needs it.

Arbiter - A functional module that accepts bus requests from Requester modules and grants control of the DTB to one Requester at a time.

Utility Bus — One of the four buses provided by the VMEbus backplane. This bus includes signals that provide periodic timing and coordinate the power-up and power-down of VMEbus systems.

CR/CSR -- A functional module that provides Configuration ROM information and Control and Status Registers. The module provides manufacturing and board ID and other important board information. The CSRs are used for software configuration of a VMEbus system.

System Clock Driver - A functional module that provides a 16 MHz timing signal on the Utility Bus.

Serial Bus — A functional module that provides a bused 2 wire interface between cards in the backplane, independent of the other VMEbus modules.

Power Monitor Module - A functional module that monitors the status of the primary power source to the VMEbus system, and signals when that power has strayed outside the limits required for reliable system operation. Since most systems are powered by an AC source, the Power Monitor is typically designed to detect drop-out or brown-out conditions on AC lines.

System Controller Board - A board which resides in slot 1 of a VMEbus backplane and has a System Clock Driver, an Arbiter, an IACK Daisy-Chain Driver, and a Bus Timer. Some also have a Power Monitor.

1.2.1.3 Types of Cycles on the VMEbus

Read Cycle — A DTB cycle used to transfer 1, 2, 3, 4 or 8 bytes from a Slave to a Master. The cycle begins when the Master broadcasts an address and an address modifier. Each Slave captures the address modifier and address and checks to see if it is to respond to the cycle. If so, it retrieves the data from its internal storage, places it on the data bus and acknowledges the transfer. The Master then terminates the cycle.

Write Cycle — A DTB cycle used to transfer 1, 2, 3, 4 or 8 bytes from a Master to a Slave. The cycle begins when the Master broadcasts an address and address modifier and places data on the DTB. Each Slave captures the address and address modifier and checks to see if it is to respond to the cycle. If so, it stores the data and then acknowledges the transfer. The Master then terminates the cycle.

Block Read Cycle — A DTB cycle used to transfer a block of 1 to 256 bytes from a Slave to a Master. This transfer is done using a string of 1, 2, or 4 byte data transfers. Once the block transfer is started, the Master does not release the DTB until all of the bytes have been transferred. It differs from a string of read cycles in that the Master broadcasts only one address and address modifier (at the beginning of the cycle). Then the Slave increments this address on each transfer so that the data for the next transfer is retrieved from the next higher location.

Block Write Cycle — A DTB cycle used to transfer a block of 1 to 256 bytes from a Master to a Slave. The block write cycle is very similar to the block read cycle. It uses a string of 1, 2, or 4 byte data transfers. The Master does not release the DTB until all of the bytes have been transferred. It differs from a string of write cycles in that the Master broadcasts only one address and address modifier (at the beginning of the cycle). Then the Slave increments this address on each transfer so that the data from the next transfer is stored in the next higher location.

Multiplexed Cycle - A DTB cycle that transfers address information and/or data information using both the address and data buses. Multiplexed cycles are used in four cases.

- a: A64 the full address bus and the full data bus are combined to create a 64 bit address.

- b: MBLT the full address bus and the full data bus are combined to create a 64 bit data word.

- c: A40 The full 24 bit address bus and the full 16 bit data bus on the P1/J1 connector are combined to create a 40 bit address. This mode is especially useful for 3U boards which have a J1 connector only.

- d: MD32 The lower 16 address lines and the lower 16 data lines are combined to create a 32 bit data word. This mode is especially useful for 3U modules.

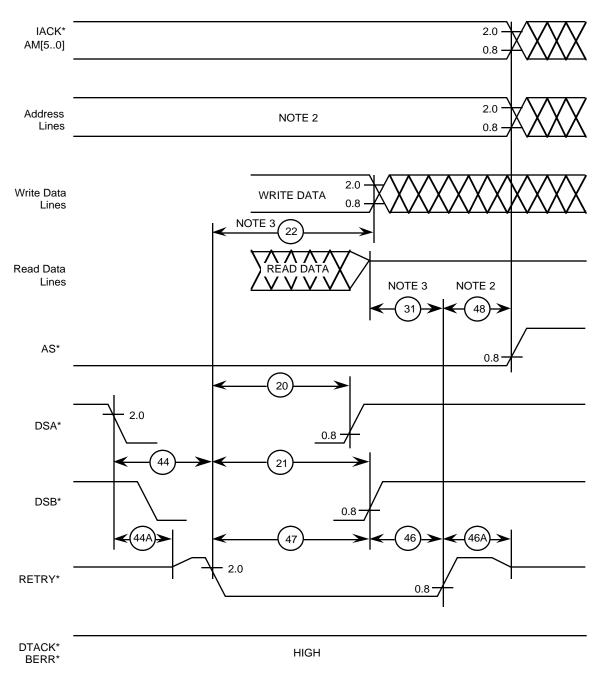

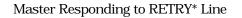

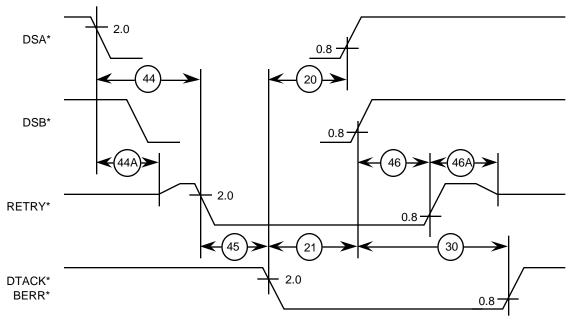

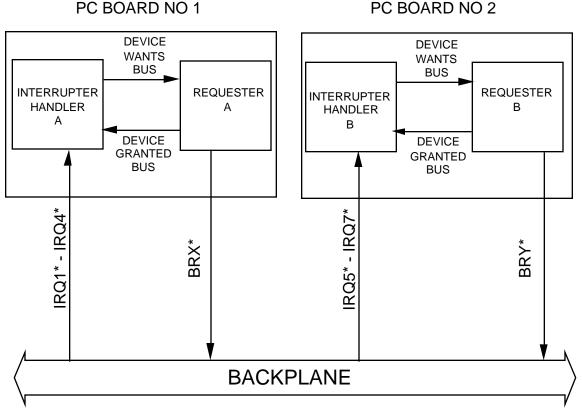

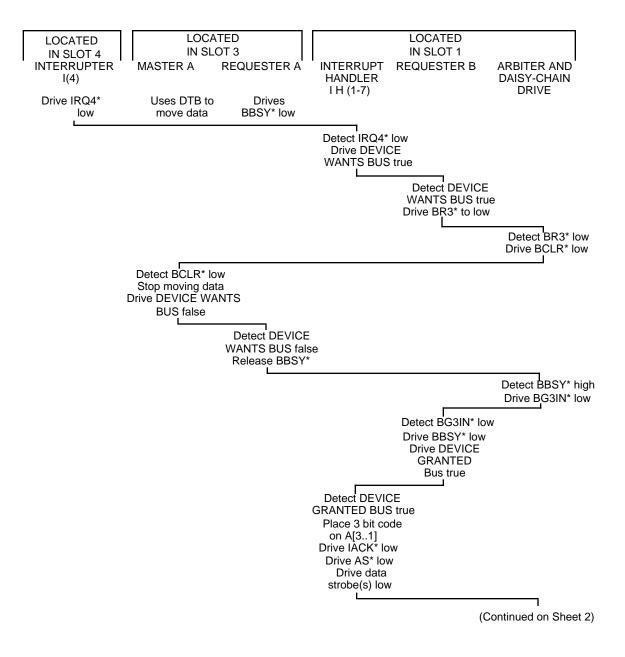

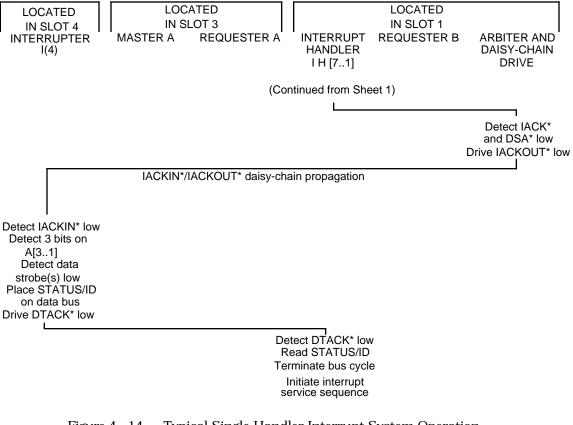

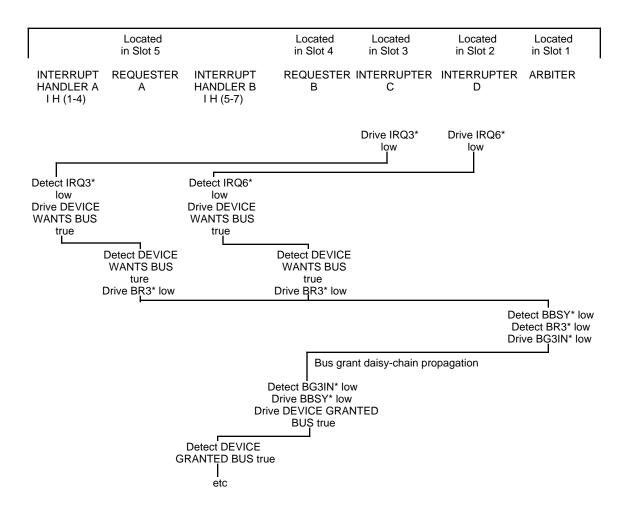

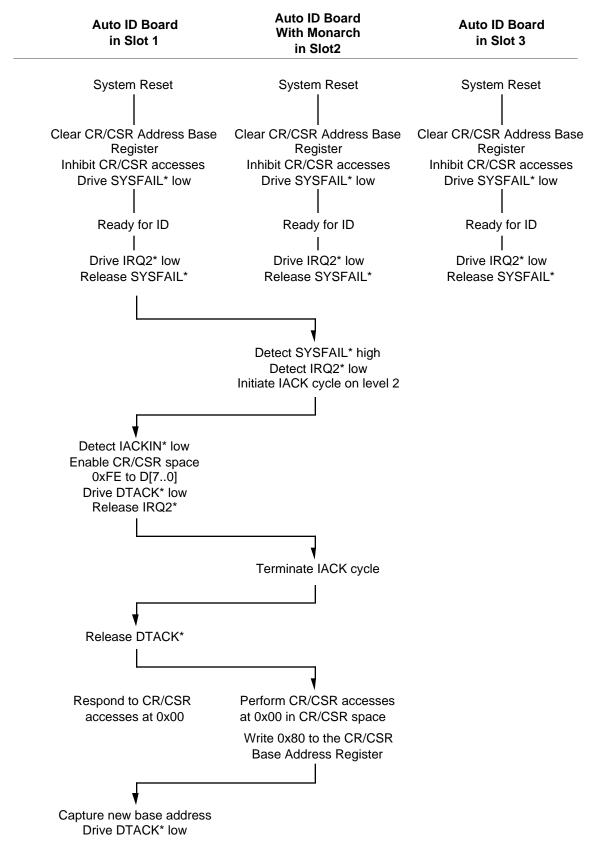

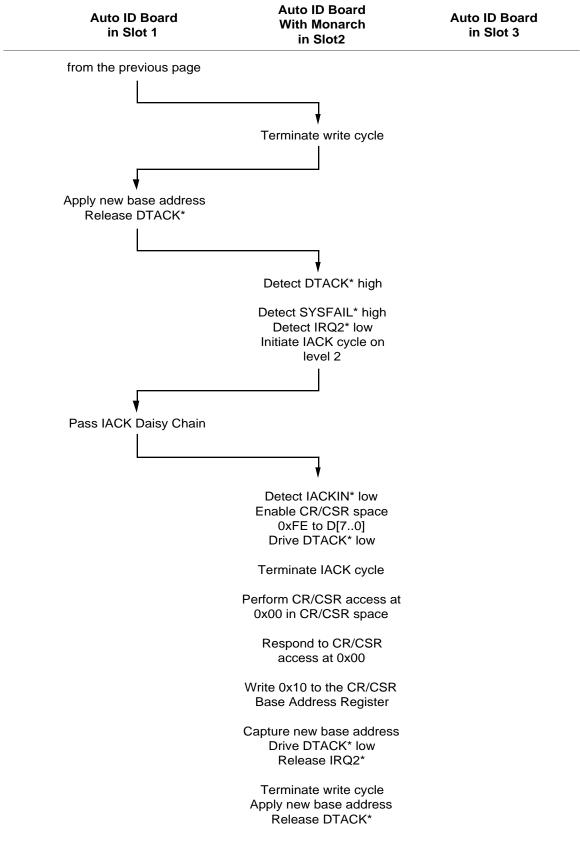

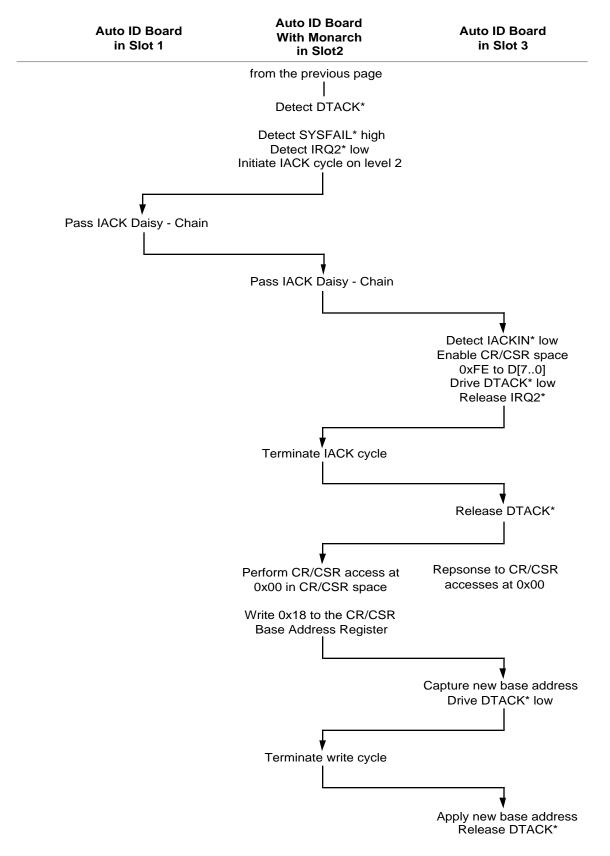

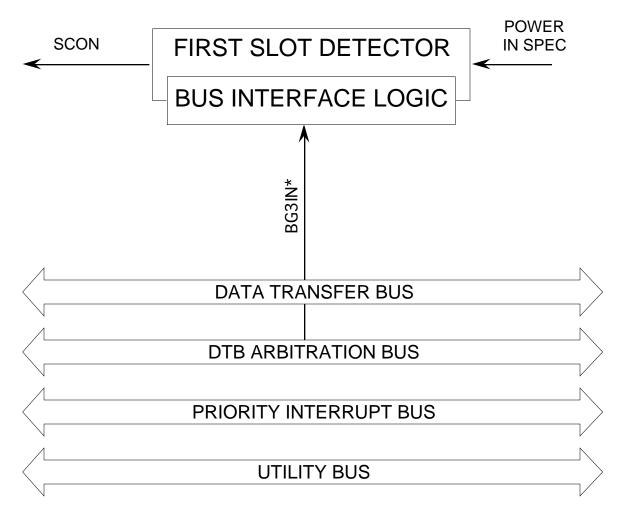

Multiplexed cycles are used in both basic transfers and block transfers. A64 and A40 basic transfers support 1 byte, 2 byte and 4 byte transfers. In addition MBLT cycles support 8 byte transfers.