# PolarFire<sup>®</sup> FPGA and PolarFire SoC FPGA Power-Up and Resets User Guide

# Introduction

Microchip's PolarFire<sup>®</sup> FPGAs are the fifth-generation family of non-volatile FPGA devices, built on state-of-the-art 28 nm non-volatile process technology. PolarFire FPGAs deliver the lowest power at mid-range densities. PolarFire FPGAs lower the cost of mid-range FPGAs by integrating the industry's lowest power FPGA fabric, lowest power 12.7 Gbps transceiver lane, built-in low power dual PCI Express Gen2 (EP/RP), and, on select data security (S) devices, an integrated low-power crypto co-processor.

Microchip's PolarFire SoC FPGAs are the fifth-generation family of non-volatile SoC FPGA devices, built on state-ofthe-art 28 nm non-volatile process technology. The PolarFire SoC family offers industry's first RISC-V based SoC FPGAs capable of running Linux. It combines a powerful 64-bit 5x core RISC-V Microprocessor Subsystem (MSS), based on SiFive's U54-MC family, with the PolarFire FPGA fabric in a single device.

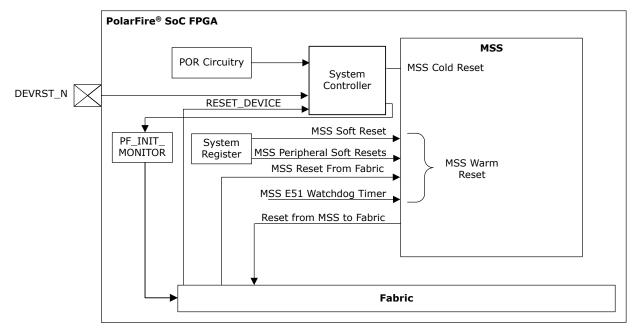

Both PolarFire FPGA and PolarFire SoC FPGAs use advanced power-up circuitry to ensure reliable power-up. When the device is powered on, the Power-on Reset (POR) circuitry and the System Controller ensure a systematic POR. System Controller is responsible for device boot and design initialization. This document describes the entire process of device power-up and resets.

The following table summarizes the power-up and reset states in PolarFire FPGA and PolarFire SoC FPGA families.

| Component                        | PolarFire FPGA (MPF) | PolarFire SoC FPGA<br>(MPFS) |

|----------------------------------|----------------------|------------------------------|

| Power-On                         | 1                    | ✓                            |

| Device Boot                      | ✓                    | ✓                            |

| Design and Memory Initialization | ✓                    | 1                            |

| • uPROM                          | ✓                    | 1                            |

| • sNVM                           | ✓                    | 1                            |

| SPI Flash                        | ✓                    | 1                            |

| • eNVM                           | —                    | 1                            |

| MSS Pre-Boot                     | —                    | ✓                            |

| MSS User Boot                    | —                    | ✓                            |

| Device Reset                     | 1                    | ✓                            |

| MSS Reset                        | —                    | 1                            |

#### Table 1. Power-Up and Reset States

## References

- For more information about embedded memory blocks, see PolarFire FPGA and PolarFire SoC FPGA Fabric User Guide.

- For more information about MSS booting, see PolarFire SoC Software Development and Tool Flow User Guide.

- For more information about PCIe initialization process, see PolarFire FPGA and PolarFire SoC FPGA PCI Express User Guide.

- For more information about Power-Up to Functional Timing, see PolarFire FPGA Datasheet or PolarFire SoC FPGA Advance Datasheet.

- For more information about MSS, see PolarFire SoC FPGA MSS Technical Reference Manual.

- For more information on power supply sequencing requirements and recommendations, see UG0726: PolarFire FPGA Board Design User Guide or UG0901: PolarFire SoC Board Design Guidelines User Guide.

# **Table of Contents**

| Intr | oductio  | n                                           | 1   |

|------|----------|---------------------------------------------|-----|

|      | Refere   | ences                                       | 2   |

| 1.   | Acron    | yms                                         | . 5 |

| 2.   | Power    | r-Up                                        | . 6 |

|      | 2.1.     | Power-On                                    | . 6 |

|      | 2.2.     | Device Boot                                 | 6   |

|      | 2.3.     | Design and Memory Initialization            | . 7 |

|      | 2.4.     | MSS Pre-Boot (For PolarFire SoC FPGA Only)  | 25  |

|      | 2.5.     | MSS User Boot (For PolarFire SoC FPGA Only) |     |

|      | 2.6.     | HSIO/GPIO Bank Initialization               |     |

|      | 2.7.     | I/O Recalibration                           |     |

|      | 2.8.     | Transceiver Initialization                  |     |

|      | 2.9.     | User PLLs and DLLs Initialization           |     |

|      |          | PCIe Initialization                         |     |

|      | 2.11.    | State of Blocks During Power-Up             | 35  |

| 3.   | Polar    | Fire FPGA Resets                            | 37  |

|      | 3.1.     | Hard Resets                                 | 37  |

|      | 3.2.     | User Reset Generation Scheme                | 38  |

| 4.   | Polar    | Fire SoC FPGA Resets                        | 41  |

|      | 4.1.     | Hard Resets                                 |     |

|      | 4.2.     | MSS Resets                                  | 41  |

|      | 4.3.     | User Reset Generation Scheme                | 43  |

| 5.   | Syste    | m Controller Suspend Mode                   | 46  |

|      | 5.1.     | Device Programming and System Services      | 46  |

|      | 5.2.     | PolarFire SoC Reboot                        | 46  |

| 6.   | Apper    | ndix: Power Supplies                        | 48  |

| 7.   | Revisi   | on History                                  | 49  |

| Mic  | rochip   | FPGA Support                                | 52  |

| The  | Micro    | chip Website                                | 52  |

| Pro  | duct Cl  | nange Notification Service                  | 52  |

| Cus  | stomer   | Support                                     | 52  |

| Mic  | rochip   | Devices Code Protection Feature             | 52  |

| Leg  | al Noti  | ce                                          | 53  |

| Tra  | demark   | S                                           | 53  |

| Qua  | ality Ma | nagement System                             | 54  |

| Worldwide Sales and Service |

|-----------------------------|

|-----------------------------|

# 1. Acronyms

The following table lists the acronyms used in this document.

## Table 1-1. List of Acronyms

| Acronym | Expanded                                      |  |  |  |  |

|---------|-----------------------------------------------|--|--|--|--|

| AMBA    | ARM Advanced Microcontroller Bus Architecture |  |  |  |  |

| eNVM    | embedded Non-Volatile Memory                  |  |  |  |  |

| MSS     | Microprocessor Subsystem                      |  |  |  |  |

| POR     | Power on Reset                                |  |  |  |  |

| SCB     | System Controller Bus                         |  |  |  |  |

| sNVM    | Secure Non-volatile Memory                    |  |  |  |  |

| HSIO    | High-speed IO                                 |  |  |  |  |

| GPIO    | General Purpose IO                            |  |  |  |  |

| PLL     | Phase-locked loop                             |  |  |  |  |

| DLL     | Delay-locked loop                             |  |  |  |  |

| FIC     | Fabric Interface Controller                   |  |  |  |  |

| PCle    | Peripheral Component Interconnect Express     |  |  |  |  |

| SCSM    | System Controller Suspend Mode                |  |  |  |  |

| PUFT    | Power-Up to Function Time                     |  |  |  |  |

# 2. Power-Up

The device power-up process includes the following sequential steps:

- 2.1. Power-On

- 2.2. Device Boot

- 2.3. Design and Memory Initialization

- 2.4. MSS Pre-Boot (For PolarFire SoC FPGA Only)

- 2.5. MSS User Boot (For PolarFire SoC FPGA Only)

- 2.6. HSIO/GPIO Bank Initialization

- 2.8. Transceiver Initialization

- 2.9. User PLLs and DLLs Initialization

- 2.10. PCIe Initialization

- 2.11. State of Blocks During Power-Up

## 2.1 Power-On

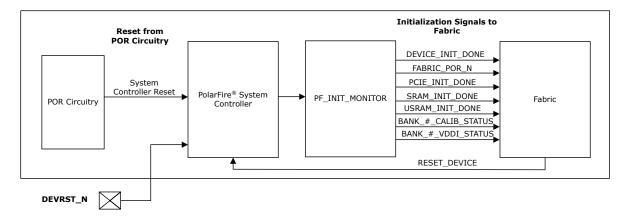

When the device is powered on, the POR circuitry detects voltage ramp-up on the VDD, VDD18, and VDD25 power supply rails using voltage detectors. For a list of power supplies, see 6. Appendix: Power Supplies. The System Controller remains in the reset state until the required voltage threshold levels are reached. The System Controller is responsible for enabling, or turning on the FPGA fabric and related IOs.

The voltage detectors in the devices are calibrated with a high-level of accuracy to ensure reliable monitoring of minimum threshold levels. For power-supply threshold voltage levels to release POR, see the "Power-on Reset Voltages" section in respective PolarFire FPGA Datasheet or PolarFire SoC FPGA Advance Datasheet. The device boot starts after a fixed delay of 10 µs once the voltage supply rails reach their respective threshold levels.

In both the device families, there are separate voltage detectors to monitor IO bank supplies. During POR, the dedicated IO bank is powered-up, the serial transceivers and the fabric are powered down, and HSIO/GPIO banks are tri-stated. Separate detectors in the associated IO bank controller (for Bank 3) detect when the VDDI3 is at the level required to allow enabling the inputs and subsequently (after a delay of 200 ns) the outputs of the dedicated IO bank (including SPI configuration and JTAG IO).

For more information on power supply sequencing requirements and recommendations, see the "Core Power Supply Operations" section, in respective UG0726: PolarFire FPGA Board Design User Guide or UG0901: PolarFire SoC Board Design Guidelines User Guide.

## 2.2 Device Boot

After POR circuitry releases the System Controller from reset, the device boot-up procedure is executed by the System Controller to bring-up the FPGA fabric and related IOs. The System Controller always executes the same device boot-up sequence irrespective of the user design.

The following events occur during device boot-up:

- sNVM is powered up and enabled for normal operation.

- Transceiver IOs are enabled.

- User voltage detectors are enabled.

- FPGA fabric is powered-up and enabled.

- HSIO and GPIO banks are configured based on the user configuration in the Libero<sup>®</sup> SoC

- Only GPIO can be used before calibration.

- MSS is powered down and MSSIOs are tri-stated (for PolarFire SoC FPGA only).

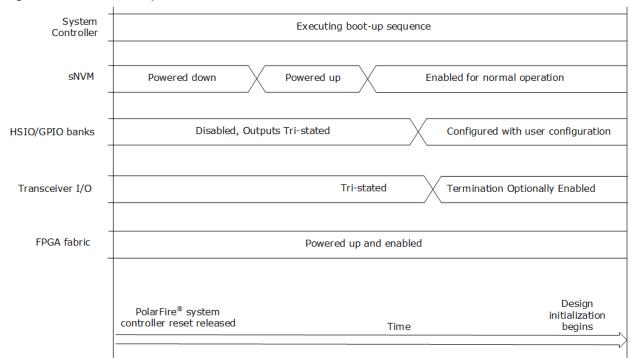

The following illustration shows the boot-up sequence for a programmed PolarFire FPGA device.

Figure 2-1. Device Boot-Up for PolarFire FPGA

# 2.3 Design and Memory Initialization

After the device boot process completes, the fabric RAM blocks (LSRAMs and µSRAMs) are initialized to zero by default. In both the device families, the fabric RAM blocks can be initialized with known values, if desired. PCIe and XCVR blocks used in the design are initialized with the user configuration data at power-up. The System Controller performs the design and memory initialization during the power-up sequence. The memory initialization data can be stored in µPROM, sNVM, or an external SPI Flash. The storage location of the initialization data is selected during the Libero design flow. The initialization data can be encrypted for storing in external SPI Flash.

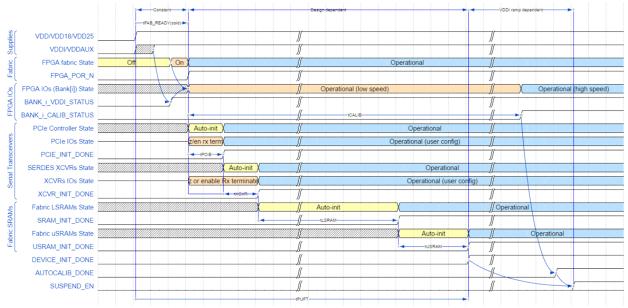

The following figure shows the sequence in which the fabric, PCIe, Transceiver, LSRAMs, and µSRAMs are automatically initialized. The sequence is customized depending on the resources instantiated in the user design. For example, the PCIE\_INIT\_DONE will not assert if the user design does not contain PCIe. As a result, the sequence skips the PCIe initialization and moves to the next step. At this stage in PolarFire SoC FPGA device, the MSS remains in reset.

In Libero SoC, memory initialization can be done using any of the following methods:

- Importing the content file using the fabric RAMs tab of the Configure Design Initialization Data and Memories option after Place and Route is performed. For more information, see 2.3.7. How To Set Up Design and Memory Initialization.

- Importing the content file using the LSRAM and µSRAM Configurator before Place and Route. For more information, see 2.3.9. RAM Initialization Before Place and Route.

The user can monitor the design initialization status using the Initialization Monitor.

#### Figure 2-2. Power-up To Functional Time (PUFT)

The total power-up to functional time is as shown in the following equation:

tPUFT = tFAB\_READY(cold/warm) + max((tPCIE + tXCVR + tLSRAM + tUSRAM), tCALIB)

PUFT is variable depending on the design configuration.

For more information about typical PUFT, see respective PolarFire FPGA Datasheet or PolarFire SoC FPGA Advance Datasheet.

#### Notes:

- Power-up To Functional Time is based on the case where VDDI/VDDAUX of IO banks are powered either before or after VDD/VDD18/VDD25. The IO bank enable time is measured from the assertion time of VDD/VDD18/ VDD25. If VDDI/VDDAUX of IO banks are powered sufficiently after VDD/VDD18/VDD25, then the IO bank enable time is measured from the assertion of VDDI/VDDAUX. In this case, IO operation is indicated by the assertion of BANK\_#\_VDDI\_STATUS, rather than being measured relative to FABRIC\_POR\_N negation.

- The assertion of AUTOCALIB\_DONE can occur before or after the assertion of DEVICE\_INIT\_DONE. The time taken for the assertion of AUTOCALIB\_DONE depends on:

- The time when VDDI/VDDAUX is up after VDD/VDD18/VDD25 is powered on.

- The ramp times of VDDI of each IO bank designated for auto-calibration.

- How much auto-initialization is to be performed for the PCIe, SerDes transceivers and fabric LSRAMs.

- If any of the IO banks specified for auto-calibration do not have their VDDI/VDDAUX powered on within the auto-calibration timeout window, then it auto-calibrates whenever VDDI/VDDAUX is subsequently powered on. To obtain an accurate calibration on such IO banks, it is necessary to initiate a re-calibration (using CALIB\_START from fabric).

- SUSPEND\_EN asserts (if the suspend mode is enabled) about 100 system controller clock cycles after assertion of DEVICE\_INIT\_DONE or AUTOCALIB\_DONE.

- Both the device families have built-in tamper detection features to monitor voltage supplies and flags to detect minimum or maximum threshold values. These flags are valid only after design initialization, and not during POR.

The following signals are asserted during the design initialization:

- DEVICE\_INIT\_DONE: asserted once the execution of design initialization is complete.

- FABRIC\_POR\_N: de-asserted when the fabric is operational.

- PCIE\_INIT\_DONE: used by fabric logic to hold PCIe-related fabric logic in reset until the PCIe controller is initialized. PCIE\_INIT\_DONE is asserted after initializing the PCIe lane instances placed in the PCIe quad. If XCVR lanes are placed in the PCIe capable quad, then XCVR\_INIT\_DONE is asserted.

- XCVR\_INIT\_DONE: asserted when the XCVR block is initialized.

- SRAM\_INIT\_DONE: asserted when the LSRAM blocks are initialized.

- USRAM\_INIT\_DONE: asserted when the µSRAM blocks are initialized.

- BANK\_#\_CALIB\_STATUS: This signal can be used by user logic to determine if the calibration completes for each IO banks. # denotes the bank number (0,1, 7, 8, and 9).

- BANK\_#\_VDDI\_STATUS: This signal can be used to monitor status of VDDI supply on specific IO banks. This signal is the output signal from the INIT\_MONITOR IP if any of the corresponding bank is selected. # denotes the bank number (0,1, 7, 8, and 9).

- SRAM\_INIT\_FROM\_SNVM\_DONE: asserted when SRAM is initialized from sNVM.

- USRAM\_INIT\_FROM\_SNVM\_DONE: asserted when USRAM is initialized from sNVM.

- SRAM\_INIT\_FROM\_UPROM\_DONE: asserted when SRAM is initialized from µPROM.

- USRAM\_INIT\_FROM\_UPROM\_DONE: asserted when USRAM is initialized from µPROM.

- SRAM\_INIT\_FROM\_SPI\_DONE: asserted when SRAM is initialized from SPI.

- USRAM\_INIT\_FROM\_SPI\_DONE: asserted when USRAM is initialized from SPI.

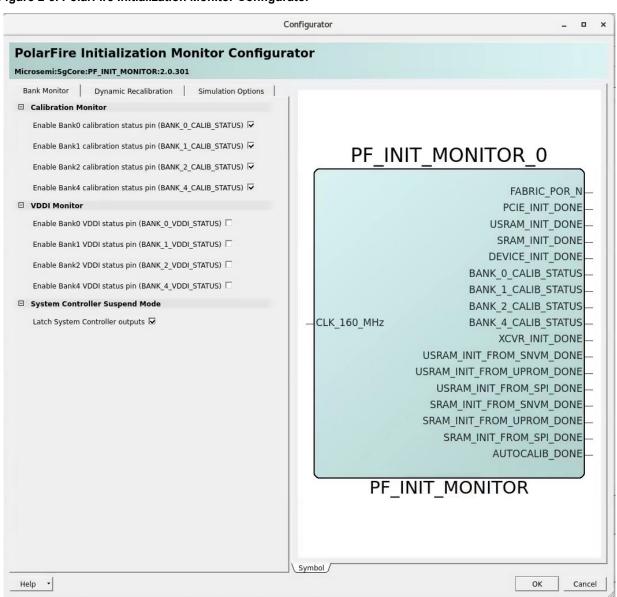

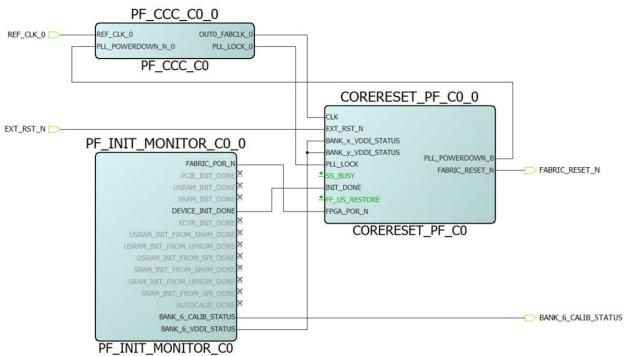

### 2.3.1 PolarFire Initialization Monitor

PolarFire Initialization Monitor (PF\_INIT\_MONITOR) is an available IP that exposes the device configuration status to the FPGA fabric. This IP must be instantiated in the FPGA fabric in all designs and is used to gate the operation of user fabric logic until the device initialization is complete. The assertion of DEVICE\_INIT\_DONE signifies the completion of device configuration. PolarFire and PolarFireSoC devices have a System Controller Suspend mode (SCSM) feature that can be used to force the system controller into reset after device initialization is complete. This mode is desirable for safety critical applications to protect the device from unintended device programming or zeroization of the device due to Single Event Upset (SEU) events. When using the device System Controller Suspend mode feature, the Latch System Controller outputs option must be enabled. The exposed CLK\_160\_MHZ port must be connected to the internal 160 MHz RCOSC. The PF\_INIT\_MONITOR IP is available in the IP Catalog under Clock and Management as shown in the following figure.

**Note:** For PolarFire and RT PolarFire devices, when using the System Controller Suspend mode feature of the device and the JTAG\_TRST\_B pin is asserted to a logic high, all outputs of the PF\_INIT\_MONITOR macro are forced = 0. This scenario occurs when the user intends to reprogram the device or debug the device using SmartDebug. Since the PF\_INIT\_MONITOR macro outputs are often used for resetting the user logic design, so appropriate user design considerations must be made for this operational case. For more information about System Controller Suspend mode feature, see PolarFire FPGA and PolarFire SoC FPGA System Services User Guide.

Figure 2-3. PolarFire Initialization Monitor Configurator

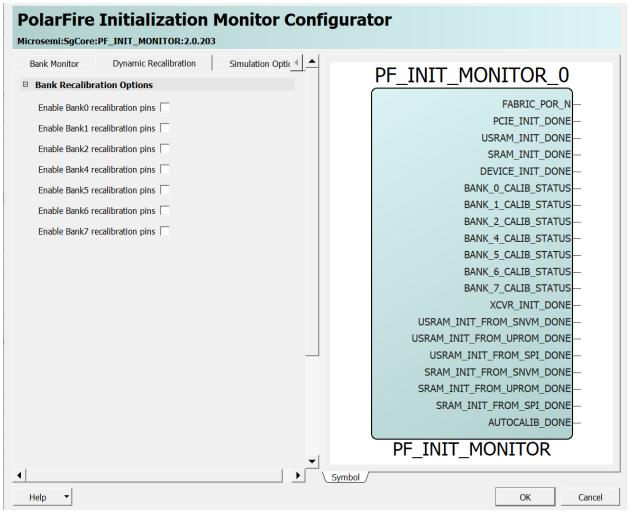

The following figure shows the Dynamic Recalibration tab.

Figure 2-4. PolarFire Initialization Monitor Configurator - Dynamic Recalibration

PolarFire Initialization Monitor provides simulation support. Use the **Simulation Options** tab to specify the time of releasing the output signals from the zero time instance. The following figure shows the **Simulation Options** tab.

| L Configurator                                        | X                                            |

|-------------------------------------------------------|----------------------------------------------|

| PolarFire Initialization Monitor Configurator         |                                              |

| Bank Monitor Dynamic Recalibration Simulation Options | PF_INIT_MONITOR_0                            |

| FABRIC_POR_N assertion delay (ns)                     |                                              |

| PCIE_INIT_DONE assertion delay (ns) 4                 | PCIE_INIT_DONE                               |

| USRAM_INIT_DONE assertion delay (ns) 5                | SRAM INIT DONE                               |

| SRAM_INIT_DONE assertion delay (ns) 6                 | DEVICE_INIT_DONE                             |

| DEVICE_INIT_DONE assertion delay (ns) 7               | BANK_0_CALIB_STATUS                          |

| Calibration monitor                                   | BANK_1_CALIB_STATUS                          |

| www.window.snip                                       | BANK_2_CALIB_STATUS                          |

| BANK_0_CALIE_STATUS assertion delay (ns) 1            | BANK_4_CALIB_STATUS                          |

| BANK_1_CALIB_STATUS assertion delay (ns) 1            | BANK_5_CALIB_STATUS—<br>BANK 6 CALIB STATUS— |

| BANK_2_CALIB_STATUS assertion delay (ns) 1            | BANK_0_CALIB_STATUS                          |

| BANK_4_CALIB_STATUS assertion delay (ns) 1            | XCVR INIT DONE                               |

| BANK_5_CALIB_STATUS assertion delay (ns)              | USRAM_INIT_FROM_SNVM_DONE_                   |

| BANK_6_CALIB_STATUS assertion delay (rs) 1            | USRAM_INIT_FROM_UPROM_DONE                   |

| BANK_7_CALIB_STATUS assertion delay (ns)              | USRAM_INIT_FROM_SPI_DONE                     |

|                                                       | SRAM_INIT_FROM_SNVM_DONE                     |

| UDDI monitor                                          | SRAM_INIT_FROM_UPROM_DONE                    |

| BANK_0_VDDI_STATUS assertion delay (ns)               | SRAM_INIT_FROM_SPI_DONE                      |

| BANK_1_VDDI_STATUS assertion delay (ns)               | AUTOCALIB_DONE                               |

| BANK_2_VDDI_STATUS assertion delay (ns)               | PF_INIT_MONITOR                              |

| BANK_4_VDDI_STATUS assertion delay (ns) 1 Symbol      |                                              |

| Help 🔻                                                | OK Cancel                                    |

Figure 2-5. PolarFire Initialization Monitor Configurator - Simulation Options

**Note:** IOs must be calibrated before initiating the training logic of the DDR controller. This requires generating a reset signal by ANDing the DEVICE\_INIT\_DONE and BANK\_#\_CALIB\_STATUS signals of the PFSOC\_INIT\_MONITOR IP. BANK\_# refers to the BANK where the DDR subsystem is placed.

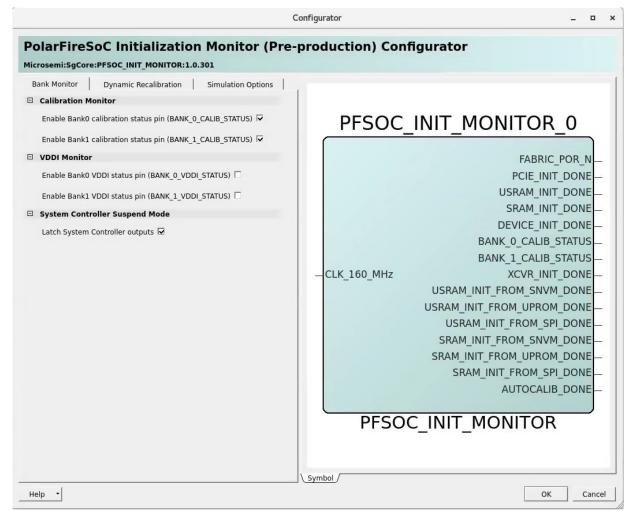

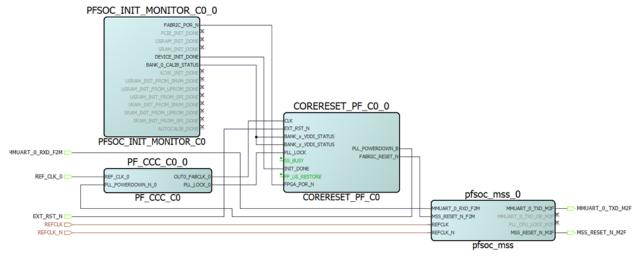

## 2.3.2 PolarFire SoC Initialization Monitor

PolarFire SoC Initialization Monitor (PFSOC\_INIT\_MONITOR) is an IP that exposes the device configuration status to the FPGA fabric. This IP must be instantiated in the FPGA fabric in all designs and can be used to gate the operation of user fabric logic until the device initialization is complete. The assertion of DEVICE\_INIT\_DONE signifies the completion of the device configuration. PolarFire and PolarFireSoC devices have a System Controller Suspend mode feature that can be used to force the system controller into reset after device initialization is complete. This mode is essential for safety critical applications to protect the device from unintended device programming or zeroization of the device due to Single Event Upset (SEU) events. When using the device System Controller Suspend mode feature, the Latch System Controller outputs option must be enabled. The exposed CLK\_160\_MHZ port must be connected to the internal 160 MHz RCOSC. The PFSOC\_INIT\_MONITOR IP is available in the IP Catalog under Clock and Management as shown in the following figure.

Figure 2-6. PolarFire SoC Initialization Monitor Configurator

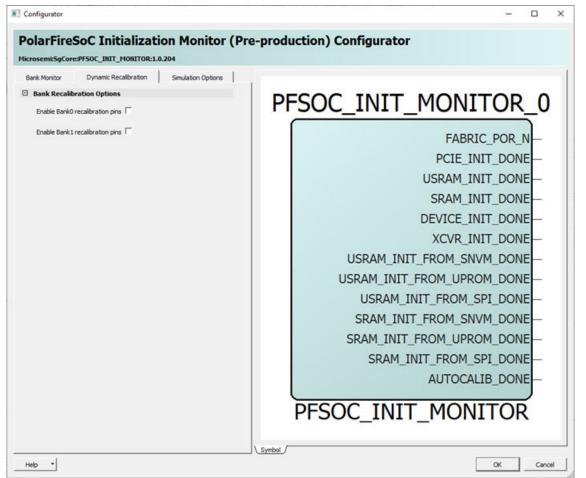

The following figure shows the Dynamic Recalibration tab.

Figure 2-7. PolarFire SoC Initialization Monitor Configurator - Dynamic Recalibration

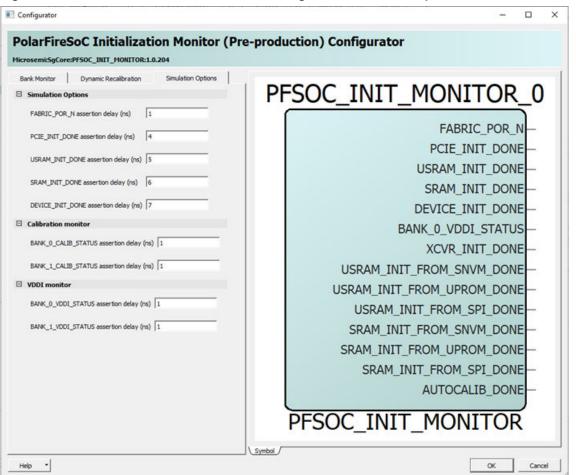

PolarFire SoC Initialization Monitor provides simulation support. Use the **Simulation Options** tab to specify the time of releasing the output signals from the zero time instance. The following figure shows the **Simulation Options** tab.

Figure 2-8. PolarFire SoC Initialization Monitor Configurator - Simulation Options

**Note:** IOs must be calibrated before initiating the training logic of the DDR controller. This requires generating a reset signal by ANDing the DEVICE\_INIT\_DONE and BANK\_#\_CALIB\_STATUS signals of the PFSOC\_INIT\_MONITOR IP. BANK\_# refers to the BANK where the DDR subsystem is placed.

## 2.3.3 Secured Non-Volatile Memory (sNVM)

Each device has 56 Kbytes of sNVM, organized into 221 pages of 236 or 252 bytes depending on whether the data is stored as plain text or encrypted/authenticated data. It can be accessed through system service calls to the System Controller. Pages within the sNVM can be marked as ROM during bit-stream programming. The sNVM content can be used to initialize LSRAMs and µSRAMs with secure data.

The following formulas applies where there is at least one LSRAM or USRAM to be auto-initialized in the user design, giving a duration in milliseconds, for the initialization of the RAM blocks from sNVM.

tLSRAM\_pt\_SNVM = ((14.0875+(541.4125×L))/1000)±6%

tUSRAM\_pt\_SNVM = ((14.0875+(29.325×L))/1000)±6%

Where,

L = Number of LSRAMs to be auto-initialized

U = Number of small SRAMs to be auto-initialized

Note: pt in "tLSRAM\_pt\_SNVM" and "tUSRAM\_pt\_SNVM" refers to "plaintext" .

## 2.3.4 Embedded Non-Volatile Memory (eNVM) (For PolarFire SoC FPGA Only)

PolarFire SoC FPGA devices include one embedded non-volatile memory (eNVM) block size of 128 KB. eNVM supports Single error correction and dual error detection (SECDED) protected, High Data Retention Time. For more information, see PolarFire FPGA and PolarFire SoC FPGA Security User Guide.

### 2.3.5 µPROM

Both the device families have a micro programmable read-only memory (µPROM) row located at the bottom of the fabric, providing up to 513 Kbytes of non-volatile, read-only memory. The address bus is 16-bit wide and the read data bus is 9-bit wide. Fabric logic has access to the entire µPROM data.

The following formulas apply where there is at least one LSRAM or USRAM to be auto-initialized in the user design, giving a duration in milliseconds.

tLSRAM\_pt\_UPROM = ((30.1325+(663.7125×L))/1000)±6%

tUSRAM\_pt\_UPROM = ((30.1325+(28.75×U))/1000)±6%

Where,

L = Number of LSRAMs to be auto-initialized

U = Number of small SRAMs to be auto-initialized

Note: pt in "tLSRAM\_pt\_UPROM" and "tUSRAM\_pt\_UPROM" refers to "plaintext" .

### 2.3.6 External SPI Flash

The SPI Flash memory interfaces with the System Controller's SPI interface and can store the programming images. The System Controller supports devices from vendors like Micron, Winbond, and Spansion.

Fabric SRAM (tLSRAM and tUSRAM) in SPI Flash can be initialized using Plaintext Initialization Data, Authenticated Plaintext Initialization Data, and Authenticated Encrypted Initialization Data.

If user design does not require the auto-initialization of any large FPGA fabric SRAMs, the tLSRAM parameter is zero. If user design does not require the auto-initialization of any small FPGA fabric SRAMs (USRAMs), the tUSRAM parameter is zero.

#### 2.3.6.1 Plaintext Initialization Data Without Authentication

The following formulas apply where there is at least one LSRAM or USRAM to be auto-initialized in the user design from SPI Flash, giving a duration in milliseconds.

tLSRAM\_pt = [[{(ROUNDUP(4.034×L)+1)×8192/f} + (130×L)]/1000]+1 ±6%

tUSRAM\_pt = [[{(ROUNDUP(0.144×U)+1)×8192/f} + (25×U)]/1000]+1 ±6%

Where,

L = Number of LSRAMs to be auto-initialized

U = Number of small SRAMs to be auto-initialized

f = Frequency of the SPI clock in MHz

Note: pt in "tLSRAM\_pt" and "tUSRAM\_pt" refers to "plaintext" .

#### 2.3.6.2 Authenticated Plaintext Initialization Data

If authentication of the plaintext initialization data is selected, an additional 103 ms  $\pm$  6% must be added to the tLSRAM\_pt and tUSRAM\_pt timing parameters.

Note: pt in "tLSRAM\_pt" and "tUSRAM\_pt" refers to "plaintext" .

#### 2.3.6.3 Authenticated Encrypted Initialization Data

The following formula calculates the additional time required for LSRAM to perform the encryption.

tLSRAM\_enc = tLSRAM\_pt+tLSRAM\_auth+((ROUNDUP((L×2560)/1024,1)+1)×1024×8/DIsram)/1000

Where, pt in "tLSRAM\_pt" refers to "plaintext".

Note: DIsram depends on the SPI SCK frequency.

The following table lists the LSRAM encrypted data divisor settings.

#### Table 2-1. LSRAM Encrypted Data Divisor Settings

| SPI_SCK frequency (MHz) | DIsram |

|-------------------------|--------|

| 13.33                   | 180    |

| 20                      | 30     |

| 40                      | 15     |

The following formula calculates the additional time required for USRAM to perform the encryption.

tUSRAM\_enc = tUSRAM\_pt+tUSRAM\_auth+((ROUNDUP((U×2560)/1024,1)+1)×1024×8/Dusram)/1000

Where,

- tLSRAM\_pt = tLSRAM

- tUSRAM\_pt = tUSRAM

- auth in "tLSRAM\_auth" and "tUSRAM\_auth" refers to "Authenticated Plaintext".

- pt in "tUSRAM\_pt" refers to "plaintext".

- tLSRAM\_auth = tUSRAM\_auth =  $103ms \pm 6\%$ .

Note: Dusram depends on the SPI SCK frequency.

The following table lists the USRAM encrypted data divisor settings.

#### Table 2-2. USRAM Encrypted Data Divisor Settings

| SPI_SCK frequency (MHz) | Disram |

|-------------------------|--------|

| 20                      | 45     |

| 40                      | 20     |

For SPI\_SCK frequency of 13.3 MHz, the formula is as follows:

tUSRAM\_enc = tUSRAM\_pt + tUSRAM\_auth + 0.01

### 2.3.7 How To Set Up Design and Memory Initialization

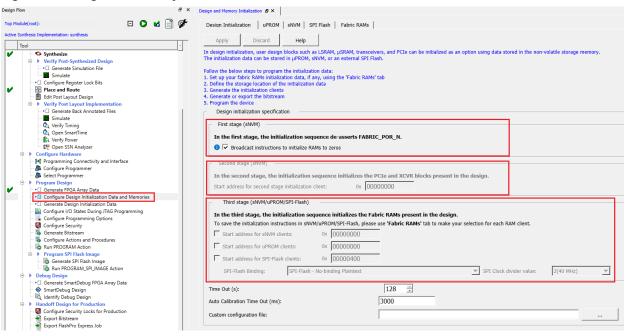

This section describes how to initialize PCIe, transceivers, and fabric RAM blocks using the **Configure Design Initialization Data and Memories** option in Libero SoC. Design and Memory Initialization is divided into three stages of initialization as shown in the following figure.

#### Figure 2-9. Design and Memory Initialization

- 1. The first stage client is responsible for bring-up of FPGA fabric and related IOs, and then de-asserts the FABRIC\_POR\_N signal. This client is stored in the sNVM at the top of the address space.

- 2. The second stage client initializes the PCIe and XCVR blocks present in the design. The client is stored in the sNVM and the starting address of the client is configurable.

- The third stage client initializes the fabric RAMs present in the design. Each logical RAM in the design can be initialized from a different Storage Type—sNVM, µPROM, or SPI Flash. The starting address of these storage types is configurable.

#### Important:

- Broadcast instructions to initialize RAMs to zeros option initializes all RAM blocks to zeros before FABRIC\_POR\_N signal is asserted. On enabling this option, the physical instances with zero data in UIC stage 2\_3 or stage\_3 assembly files are filtered out.

- The second stage client initializes the PCIe and XCVR blocks present in the design. Import a text file to change the default PCIe/XCVR register values (custom configuration). This modifies the Stage 2 generated assembly file (from default flow). The format in the text file to change the register content is as follows: Instance\_Name, Register:Field\_Name, and Hex value separated by spaces. For example: PF\_PCIE\_0/PCIESS\_LANE0\_Pipe\_AXI0 SER\_DRV\_CTRL:TXDRVTRIM 0xFFFFFF

- When initializing RAM from SPI Flash, ensure that the System Controller SPI interface is in the Master mode by setting the IO\_CFG\_INTF pin to 1.

- The SPI Clock divider value specifies the required SPI SCK frequency to read the initialization data from SPI Flash. The SPI Clock divider value must be selected based on the external SPI Flash operating frequency range.

- SPI part for the PolarFire FPGA is MT25QU01GBBB and for the PolarFire SoC FPGA is MT25QL01GBBB. Flash is connected to Bank 6 (1.8V) on the PolarFire FPGA and Bank 3 (3.3V) on the PolarFire SoC FPGA.

#### Table 2-3. SPI Clock Divider Value

| SPI Clock Divider Value | SCK Frequency |

|-------------------------|---------------|

| 2                       | 40 MHz        |

| 4                       | 20 MHz        |

| continued               |               |  |  |

|-------------------------|---------------|--|--|

| SPI Clock Divider Value | SCK Frequency |  |  |

| 6                       | 13.3 MHz      |  |  |

Follow these steps to initialize fabric RAMs at power-up:

- 1. Select the required logical RAM from the **Fabric RAMs** tab and click **Edit**. The Edit Fabric RAM Initialization Client window provides the following options to:

- Initialize the client from an Intel-Hex (\*.hex), Simple-Hex(\*.shx), Motorola-S (\*.s), or Microchip Binary (\*.mem)

- Initialize the client with Zeros

- Create the client as a placeholder with no content

- Select Storage Type for the client

## Figure 2-10. Fabric RAMs

| Usage statistics<br>LSRAM Memory<br>Available Memory(Bytes): 207<br>Used Memory(Bytes): | Clients Clients Load design configuration Edit Initialize all clients from: Initialize all Clients from sNVM Filter out Inferred RAMs R720 R720                                                                                                                                                     |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                         | Logical Insta     Logical Insta     COREAXI4INTERCONNECT_C0_0/COREAXI4INTERCONNECT_C0_0/SlvConvertor_loop[0].slvcnv/s                                                                                                                                                                               |

| Used Memory(Bytes):<br>Used Memory(Bytes):                                              | t Fabric RAM Initialization Client ? × <pre> tame: _enblk1.u_SlvAxi4WriteID/genblk1.rdata_interleave_fifo/genblk1[0].ram/mem[1:0] IName: _eave_fifo/genblk1[0].ram/mem_mem_0_0/RAM64x12_PHYS_0/INST_RAM64x12_IP Initialization Options initialized Content from Synthesis icontent from file:</pre> |

| Storage                                                                                 | e for: 6 High Speed C Low power<br>e Type sNVM<br>sNVM<br>uPROM<br>elp SPI-Flash<br>OK Close                                                                                                                                                                                                        |

- 2. After configuring the RAM initialization client, click **Apply** on the **Fabric RAMs** tab.

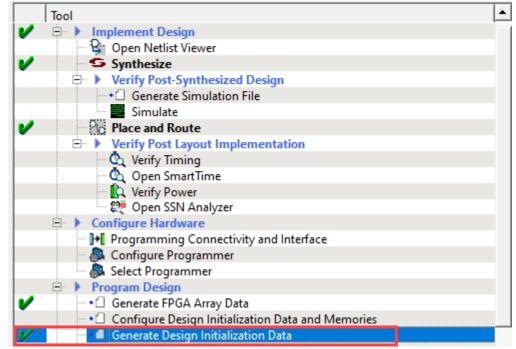

- 3. Select **Generate Design Initialization Data** under **Design Flow** tab. It automatically generates the first, second, and third stage initialization clients, which are automatically added to the non-volatile memory that the user chooses.

The **Generate Design Initialization Data** is highlighted as shown in the following figure.

Figure 2-11. Generate Design Initialization Data

The initialization clients are added to the respective tab; µPROM, SNVM, SPI Flash, or eNVM (for PolarFire SoC FPGA only). When plaintext or ciphertext authenticated clients are added, **Initialize sNVM Master Key** option is enabled and grayed out, as shown in the following figure.

### Figure 2-12. Initialization Clients Generated in sNVM

| Design Initialization uPROM sNVM | * SF | pt f | Flash   Fabric RAMs      |            |                 |             |

|----------------------------------|------|------|--------------------------|------------|-----------------|-------------|

| Apply Discard Help               |      |      |                          |            |                 |             |

| ☑ Initialize sNVM Master Key     |      |      |                          |            |                 |             |

| Usage statistics                 |      | Cli  | ents                     |            |                 |             |

| Available memory (in pages): 22  | 1    | 0    | Programming PlainTe      | ext Auther | nticated and Ci | pherText /  |

| Used memory (in pages): 21       |      |      | Add 🔻 Edit               | Delete     | Load desig      | ın configur |

| Free memory (in pages):          | 3    |      | Client Name              | Start Page | Number of bytes | End Page    |

|                                  |      | 1    | s1                       | 0          | 28200           | 111 _       |

|                                  |      | 2    | s2                       | 112        | 21900           | 198         |

|                                  |      | 3    | INIT_STAGE_1_SNVM_CLIENT | 202        | 4368            | 219         |

|                                  |      | 4    | s233                     | 200        | 2               | 200         |

|                                  |      |      |                          |            |                 | ·           |

**Important:** The second stage client is added to sNVM if the user design includes the PCIe or XCVR block.

The following figure shows the **Configure Bitstream** dialog, which is updated as per the sNVM configurations.

Figure 2-13. Configure Bitstream

| Program                                   | OK    |

|-------------------------------------------|-------|

| I ⊂ Custom security                       |       |

| ✓ Fabric/sNVM                             | Cance |

| □ Sanitize all sNVM pages in ERASE action | Help  |

| └ Initialize sNVM Master Key              |       |

|                                           |       |

If SPI Flash is selected as the storage type, the initialization client is added to the **SPI Flash** tab as shown in the following figure.

#### Figure 2-14. Third Initialization Client on SPI Flash

| Design Initialization   uPROM   sNVM   SPI Flash   Fabric RAMs   eNVM |                                                                                                            |      |      |       |              |  |  |  |                |

|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|------|-------|--------------|--|--|--|----------------|

| Apply Discard H                                                       | ielp                                                                                                       |      |      |       |              |  |  |  |                |

| Enable Auto Update                                                    |                                                                                                            |      |      |       |              |  |  |  |                |

| SPI Flash memory size: 128                                            | MB                                                                                                         |      |      |       |              |  |  |  |                |

| Usage statistics                                                      | SPI Flash Clie                                                                                             | nts  |      |       |              |  |  |  |                |

| Available memory (KB): 131071<br>Used memory (KB): 5                  | Available memory (03):131071         Add         Edit         Delete           Used memory (03):         5 |      |      |       |              |  |  |  |                |

|                                                                       |                                                                                                            |      |      |       |              |  |  |  |                |

| Free memory (KB) : 131066                                             | Program                                                                                                    | Name | Туре | Index | Content File |  |  |  | Protection for |

| Free memory (KB): 131066                                              | Program Name Type Index Content File Start End Design Protection for                                       |      |      |       |              |  |  |  |                |

4. If an external SPI Flash is chosen for stage 3, before completing the **Run PROGRAM Action**, you should generate **Generate SPI Flash Image** and **Run PROGRAM\_SPI\_IMAGE Action** from the **Design Flow** tab, as shown in the following figure.

Figure 2-15. Program SPI Flash Image

| V | 🖻 🕨 Program SPI Flash Image  |  |

|---|------------------------------|--|

| V | Generate SPI Flash Image     |  |

| V | Run PROGRAM_SPI_IMAGE Action |  |

These steps ensure that PCIe, XCVR, and Fabric RAMs present in the design are initialized during power-up using initialization clients placed in the non-volatile memory based on the user selection.

## 2.3.7.1 SPI Flash Client Configuration

Memory initialization data stored in SPI Flash can be encrypted and binded with the device. The Design Initialization tab provides the following encryption/binding options:

- SPI Flash Binding Encrypted with Default Key In this case, KLK is used as the root key for authentication and encryption/decryption

- SPI Flash Binding Encrypted with User Encryption Key 1 (UEK1) In this case, UEK1 is used as the root key for authentication and encryption/decryption

- SPI Flash Binding Encrypted with User Encryption Key 2 (UEK2) In this case, UEK2 is used as the root key for authentication and encryption/decryption

## 2.3.7.2 eNVM Client Configuration (For PolarFire SoC FPGA Only)

If eNVM is selected as the storage type, the initialization client is added to the eNVM tab as shown in the following figure. Once the initialization client is added to the eNVM, double-click **Generate Bitstream** from the **Design Flow** tab.

| Figure 2-16. Fourth Stage Initia | lization Client in eNVM    |            |                           |          |

|----------------------------------|----------------------------|------------|---------------------------|----------|

| Design Initialization uPROM sNVM | SPI Flash Fabric RAMs eNVM |            |                           |          |

| Apply Discard                    | Help                       |            |                           |          |

| Usage statistics                 | Clients                    |            |                           |          |

| Available memory (in pages): 512 |                            |            |                           |          |

| Used memory (in pages): 368      | Add 🔻 Edit                 | Delete     | .oad design configuration |          |

| Free memory (in pages): 144      |                            |            |                           |          |

|                                  | Client Name                | Start Page | Number of bytes           | End Page |

|                                  | 1 BOOT_MODE_1_ENVM_CLIEN   | го         | 94048                     | 367      |

|                                  |                            |            |                           |          |

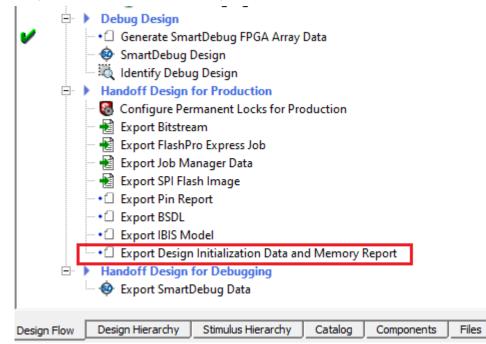

Double-click **Design Initialization Data and Memory Report** to generate the report. See the following figure.

### Figure 2-17. Design Initialization Data and Memory Report

Right-click BOOT\_MODE\_1\_ENVM\_CLIENT and select Edit to edit the Plaintext Boot Mode 1 client as shown in the following figure.

#### Figure 2-18. Edit PlainText Boot Mode 1 Client

| Content from file:                                      |                      |  |

|---------------------------------------------------------|----------------------|--|

| <ul> <li>Content from file:</li> <li>Format:</li> </ul> | hss-envm-wrapper.hex |  |

|                                                         | : ① 0x 20220000      |  |

| Start page (decimal):                                   | 0 <u>*</u> 0x0       |  |

| Number of bytes (decimal):                              | 94048 368 pages      |  |

|                                                         |                      |  |

| _ |  |

|---|--|

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

**Important:** Select **Include this client in eNVM digest calculation** option if the client is updated through bitstream; JTAG, SPI Slave, and SPI Master Programming.

The following figure shows the **Configure Bitstream** dialog, which is updated as per the eNVM configurations.

#### Figure 2-19. Configure Bitstream

| Configure Bitstream                     | ×      |

|-----------------------------------------|--------|

| Program<br>Custom security              | ОК     |

| Fabric/sNVM                             | Cancel |

| Sanitize all sNVM pages in ERASE action | Help   |

| Initialize sNVM Master Key              |        |

| v eNVM                                  |        |

| Sanitize all eNVM pages in ERASE action |        |

#### 2.3.8 Power-up To Functional (PUFT) Timing Data Report

The information about PUFT timing data is available in the Design Initialization Data and Memories report of the Libero SoC. To indicate the completion of initialization of each block, such as PCIE, XCVR, RAMs, a signal is asserted as part of device initialization after power-up (this is done as part of UIC). For example, PCIE\_INIT\_DONE signal is asserted after all the PCIE related registers are configured. The last signal that is asserted is DEVICE\_INIT\_DONE. The PUFT timing parameters such as TPCIE, TXCVR, TLSRAM, and TUSRAM are included in the PUFT timing data report. For information, see respective PolarFire FPGA Datasheet or PolarFire SoC FPGA Advance Datasheet.

In cases of PCIE and XCVR blocks, the number of instructions used to initialize the registers of that block are counted after FABRIC\_POR is asserted in each case. Software implementation of PUF timing for any signal is a product of 'number of instructions' and a constant (average time taken for one UIC instruction). This number is added to the report for every signal.

PUFT<sub>signal</sub> = (Number\_Of\_Instructions × Constant ) ns

This constant is based on the run time (of UIC script) data collected. Based on the number of instructions in that design and the amount of time taken by UIC, the average time taken for one UIC instruction is calculated.

In case of SRAM and µSRAM blocks, the amount of time taken to initialize vary from number of blocks measured on a device. This average time to initialize one block is used to compute the PUF timing of that signal. There is a constant time taken by system controller to copy the data to initialize the first block (Constant\_Copy\_Time). When the first block is being initialized, the data for initializing the second block is copied in background.

PUFT<sub>signal</sub> = Constant\_Copy\_Time + (Number\_Of\_Blocks × Average\_Time\_to\_Init\_One\_Block ) ns

These signals are asserted in a sequence so the PUFT timing for each signal depends on:

- The previous block(s) in the sequence being instantiated in the user design (or not)

- The configuration of the block (Some configurations may need a few additional registers.)

SRAMs and µSRAMs can be initialized from different storage locations (sNVM, UPROM, and SPI). In the case of SPI, additional data needs to be collected depending on the SPI clock divider value and the encryption type selected.

#### 2.3.9 RAM Initialization Before Place and Route

During Fabric RAM IP core creation, the content file can be imported for simulation. The path of the content file is stored and passed to the Design and Memory Initialization stage.

Follow these steps to initialize Fabric RAM using LSRAM and µSRAM configurator:

1. In the **PF Two-Port Large SRAM Configurator** window, select the **Memory Initialization Settings** tab. Then, select the **Initialize RAM at Power-up** check box as shown in the following figure.

#### Figure 2-20. PF Two-Port Large SRAM Configurator Window

| M_0<br>    |

|------------|

|            |

|            |

|            |

|            |

| DATA[19:0] |

| DATA[19:0] |

| DATA[19:0  |

|            |

|            |

|            |

| M          |

| M.         |

|            |

|            |

|            |

|            |

|            |

|            |

|            |

|            |

| M          |

Select the Import File option and import memory content file (Intel-Hex) from the Import Memory Content dialog box, as shown in the following figure. File extensions are set to \*.hex for Intel-Hex files during import. The imported memory content is displayed in the RAM Content Editor pane.

| Parameter settings Port               | settings Memory Initialization Settings                                                                                          |                                                                                   | -                                                 |                                                                     |              |             |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------|--------------|-------------|

| Initialize RAM at Power U             |                                                                                                                                  |                                                                                   |                                                   |                                                                     |              |             |

|                                       |                                                                                                                                  |                                                                                   |                                                   |                                                                     |              |             |

| RAM Configuration                     | Write Read                                                                                                                       |                                                                                   |                                                   |                                                                     |              |             |

|                                       | 1024 1024                                                                                                                        |                                                                                   |                                                   |                                                                     |              |             |

|                                       | 20 20                                                                                                                            |                                                                                   |                                                   | F                                                                   | PF TP        | SRAM_0      |

| Ram Initialization                    |                                                                                                                                  |                                                                                   |                                                   |                                                                     | a station of | 0.011_0     |

| Content from file                     | 1                                                                                                                                | Reset All Values                                                                  |                                                   |                                                                     | TA[19:0]     |             |

| RAM Content Editor                    |                                                                                                                                  |                                                                                   |                                                   |                                                                     | DR[9:0]      |             |

|                                       |                                                                                                                                  |                                                                                   |                                                   | D AD                                                                | 00100        | D DATA[10.  |

| Write Port View                       | Read Port View                                                                                                                   |                                                                                   |                                                   | 10000000                                                            | DR[9:0]      | R_DATA[19:0 |

| Write Port View                       | Read Port View                                                                                                                   | 1                                                                                 |                                                   | -W_EN                                                               |              | K_DATA[19.  |

| Write Port View                       | Read Port View                                                                                                                   | 1                                                                                 |                                                   | 10000000                                                            |              | K_DAIA[19.  |

| Import Memory Content                 |                                                                                                                                  |                                                                                   |                                                   | -W_EN                                                               | ×            |             |

| Import Memory Content                 |                                                                                                                                  | <ul> <li>O Search EAP4</li> </ul>                                                 | UG upd                                            | -W_EN                                                               | ×            | PSRAM       |

| Import Memory Content                 | sktop_backup2 > EAP4 UG update ~                                                                                                 | <ul> <li>O Search EAP4</li> </ul>                                                 | UG upd                                            | -W_EN                                                               | ×            |             |

| Import Memory Content<br>→ ~ ↑ 📕 « De | sktop_backup2 > EAP4 UG update ~                                                                                                 | Search EAP4                                                                       | (III )                                            | -W_EN                                                               | ×            |             |

| Import Memory Content                 | sktop_backup2 > EAP4 UG update ~                                                                                                 | Date modified                                                                     | d I                                               | - W_EN                                                              | ×            |             |

| Import Memory Content<br>             | sktop_backup2 > EAP4 UG update ~                                                                                                 | Date modified<br>7/28/2015 3:2                                                    | d<br>4 PM                                         | ate Type HEX File                                                   | ×            |             |

| Import Memory Content<br>             | sktop_backup2 > EAP4 UG update ~                                                                                                 | Date modified<br>7/28/2015 3:2<br>2/5/2014 3:29                                   | d<br>4 PM<br>PM                                   | ate Type HEX File HEX File                                          | ×            |             |

| Import Memory Content<br>             | sktop_backup2 > EAP4 UG update<br>Name<br>intel_hex.hex<br>intel_hex_g4x.hex<br>Large_G4M_hex_file.hex                           | Date modified<br>7/28/2015 3:2                                                    | 8<br>4 PM<br>2 AM                                 | ate Type HEX File                                                   | ×            |             |

| Import Memory Content<br>             | sktop_backup2 > EAP4 UG update ~                                                                                                 | Date modifier<br>7/28/2015 3:2<br>2/5/2014 3:29<br>2/6/2014 11:1                  | 1                                                 | HEX File<br>HEX File                                                | ×            |             |

| Import Memory Content<br>             | sktop_backup2 > EAP4 UG update<br>Name<br>intel_hex.hex<br>intel_hex_g4x.hex<br>Large_G4M_hex_file.hex<br>Large_G4X_hex_file.hex | Date modifier<br>7/28/2015 3:2<br>2/5/2014 3:29<br>2/6/2014 11:1<br>2/6/2014 10:4 | <pre> # # # # # # # # # # # # # # # # # # #</pre> | W_EN<br>ate<br>Type<br>HEX File<br>HEX File<br>HEX File<br>HEX File | ×            |             |

#### Figure 2-21. Import Memory Content

3. After Place and Route, select the storage type for the content file and generate the initialization client using the procedure mentioned in 2.3.7. How To Set Up Design and Memory Initialization.

For more information about LSRAM and µSRAM Configurators and user options, see the **"Embedded Memory Blocks**" section in PolarFire FPGA and PolarFire SoC FPGA Fabric User Guide.

# 2.4 MSS Pre-Boot (For PolarFire SoC FPGA Only)

Upon successful completion of Design Initialization (assertion of DEVICE\_INIT\_DONE), MSS Pre-boot starts its execution. The MSS is released from a reset after completion of all normal startup procedures. The System Controller manages the programming, initialization, and configuration of the devices. For ES devices, MSS Pre-boot does not occur if the programmed device is configured for System Controller suspend mode.

The MSS pre-boot phase of initialization is coordinated by System Controller firmware, although it may make use of the E51 in the MSS Core Complex to perform certain parts of the pre-boot sequence.

The following events occur during the MSS pre-boot stage:

- Power-up of the MSS embedded Non-Volatile Memory (eNVM)

- Initialization of the redundancy repair associated with the MSS Core Complex L2 cache

- Authentication of User boot code (if User Secure boot option is enabled)

- Handover operational MSS to User Boot code

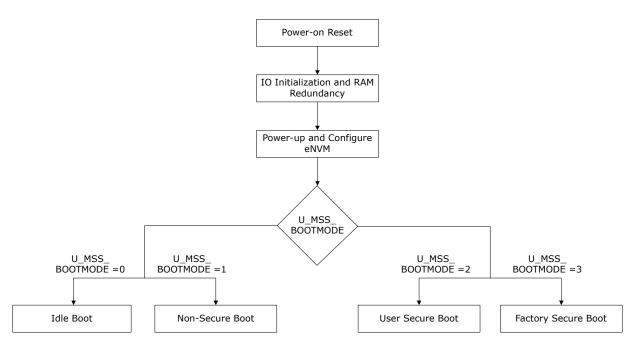

The MSS Core Complex can be booted in one of four modes. The following table lists the MSS pre-boot options, which can be configured and programmed into the sNVM. The boot mode is defined by the user parameter

U\_MSS\_BOOTMODE[1:0]. Additional boot configuration data is mode-dependent and is defined by the user parameter U\_MSS\_BOOTCFG (see Table 2-6 and Table 2-8 ).

| U_MSS_BOOTMODE[1:0] | Mode                | Description                                                                |

|---------------------|---------------------|----------------------------------------------------------------------------|

| 0                   | Idle boot           | MSS Core Complex boots from boot ROM if MSS is not configured              |

| 1                   | Non-secure boot     | MSS Core Complex boots directly from address defined by the U_MSS_BOOTADDR |

| 2                   | User secure boot    | MSS Core Complex boots from sNVM                                           |

| 3                   | Factory secure boot | MSS Core Complex boots using the factory secure boot protocol              |

The boot option is selected as part of the Libero design flow. Changing the mode can only be achieved through the generation of a new FPGA programming file.

#### Figure 2-22. MSS Pre-boot Flow

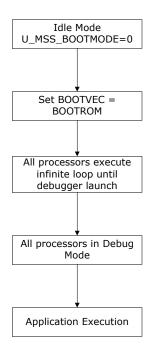

## 2.4.1 Idle Boot

If the MSS is not configured (For example, blank device), then the MSS Core Complex executes a boot ROM program which holds all the processors in an infinite loop until a debugger connects to the target. The boot vector registers maintain their value until the device is reset or a new boot mode configuration is programmed. For configured devices, this mode can be implemented using the U\_MSS\_BOOTMODE=0 boot option in the Libero configurator.

**Note:** In this mode, U\_MSS\_BOOTCFG is not used.

The following figure shows the Idle boot flow.

#### Figure 2-23. Idle Boot Flow

## 2.4.2 Non-Secure Boot

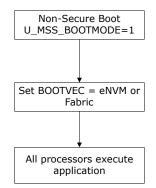

In this mode, the MSS Core Complex executes from a specified eNVM address without authentication. It provides the fastest boot option, but there is no authentication of the code image. The address can be specified by setting U\_MSS\_BOOTADDR in the Libero Configurator. This mode can also be used to boot from any FPGA fabric memory resource through FIC. This mode is implemented using the U\_MSS\_BOOTMODE=1 boot option.

The MSS Core Complex is released from reset with boot vectors defined by U\_MSS\_BOOTCFG (as listed in the following table).

| Offset (bytes) | Size (bytes) | Name     | Description          |

|----------------|--------------|----------|----------------------|

| 0              | 4            | BOOTVEC0 | Boot vector for E51  |

| 4              | 4            | BOOTVEC1 | Boot vector for U540 |

| 8              | 4            | BOOTVEC2 | Boot vector for U541 |

| 16             | 4            | BOOTVEC3 | Boot vector for U542 |

| 20             | 4            | BOOTVEC4 | Boot vector for U543 |

Table 2-5. U\_MSS\_BOOTCFG Usage in Non-Secure Boot Mode 1

The following figure shows the Non-Secure boot flow.

#### Figure 2-24. Non-Secure Boot Flow

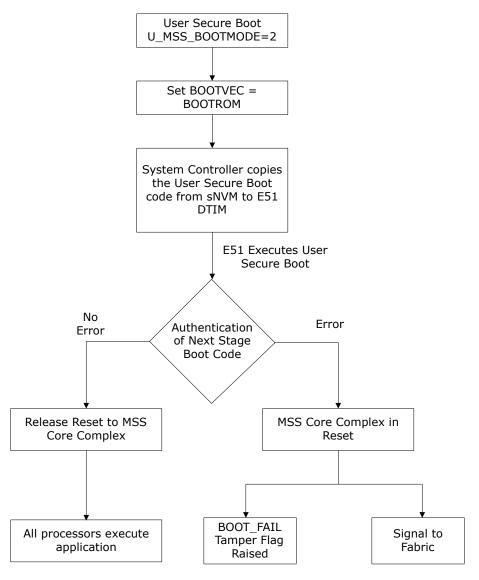

## 2.4.3 User Secure Boot

This mode allows user to implement their own custom secure boot and the user secure boot code is placed in the sNVM. The sNVM is a 56 Kbytes non-volatile memory that can be protected by the built-in physically unclonable function (PUF). This boot method is considered secured because sNVM pages marked as ROM are immutable. On power up, the System Controller copies the user secure boot code from sNVM to Data Tightly Integrated Memory (DTIM) of the E51 Monitor core. E51 starts executing the user secure boot code.

If the size of the user secure boot code is more than the size of the DTIM then user needs to split the boot code into two stages. The sNVM may contain the next stage of the user boot sequence, which may perform authentication of the next boot stage using the user authentication/decryption algorithm.

If authenticated or encrypted pages are used, then the same USK key (that is, U\_MSS\_BOOT\_SNVM\_USK) must be used for all authenticated/encrypted pages.

If authentication fails, the MSS Core Complex can be placed in reset and the BOOT\_FAIL tamper flag can be raised. This mode is implemented using the U\_MSS\_BOOTMODE=2 boot option.

| Offset (bytes) | Size (bytes) | Name                 | Description                       |

|----------------|--------------|----------------------|-----------------------------------|

| 0              | 1            | U_MSS_BOOT_SNVM_PAGE | Start page in SNVM                |

| 1              | 3            | RESERVED             | For alignment                     |

| 4              | 12           | U_MSS_BOOT_SNVM_USK  | For authenticated/encrypted pages |

#### Table 2-6. U\_MSS\_BOOTCFG Usage in User Secure Boot

The following figure shows the user secure boot flow.

#### Figure 2-25. Factory Secure Boot

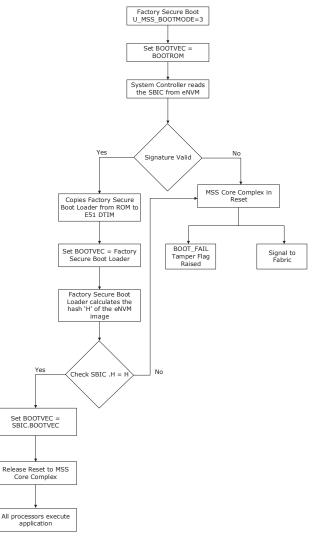

## 2.4.4 Factory Secure Boot

In this mode, the System Controller reads the Secure Boot Image Certificate (SBIC) from eNVM and validates the SBIC. On successful validation, System Controller copies the factory secure boot code from its private, secure memory area and loads it into the DTIM of the E51 Monitor core. The default secure boot performs a signature check on the eNVM image using SBIC which is stored in eNVM. If no errors are reported, reset is released to the MSS Core Complex. If errors are reported, the MSS Core Complex is placed in reset and the BOOT\_FAIL tamper flag is raised. Then, the System Controller activates a tamper flag which asserts a signal to the FPGA fabric for user action. This mode is implemented using the U MSS BOOTMODE=3 boot option.

The SBIC contains the address, size, hash, and Elliptic Curve Digital Signature Algorithm (ECDSA) signature of the protected binary blob. ECDSA offers a variant of the DSA, which uses elliptic curve cryptography. It also contains the reset vector for each Hardware thread/core/processor core (Hart) in the system.

#### Table 2-7. Secure Boot Image Certificate (SBIC)

| Offset | Size (bytes) | Value     | Description                      |

|--------|--------------|-----------|----------------------------------|

| 0      | 4            | IMAGEADDR | Address of UBL in MSS memory map |

| continued |              |              |                             |  |  |

|-----------|--------------|--------------|-----------------------------|--|--|

| Offset    | Size (bytes) | Value        | Description                 |  |  |

| 4         | 4            | IMAGELEN     | Size of UBL in bytes        |  |  |

| 8         | 4            | BOOTVEC0     | Boot vector in UBL for E51  |  |  |

| 12        | 4            | BOOTVEC1     | Boot vector in UBL for U540 |  |  |

| 16        | 4            | BOOTVEC2     | Boot vector in UBL for U541 |  |  |

| 20        | 4            | BOOTVEC3     | Boot vector in UBL for U542 |  |  |

| 24        | 4            | BOOTVEC4     | Boot vector in UBL for U543 |  |  |

| 28        | 1            | OPTIONS[7:0] | SBIC options                |  |  |

| 28        | 3            | RESERVED     | -                           |  |  |

| 32        | 8            | VERSION      | SBIC/Image version          |  |  |

| 40        | 16           | DSN          | Optional DSN binding        |  |  |

| 56        | 48           | Н            | UBL image SHA-384 hash      |  |  |

| 104       | 104          | CODESIG      | DER-encoded ECDSA signature |  |  |

| Total     | 208          | Bytes        | -                           |  |  |

## DSN

If the DSN field is non-zero, it is compared against the device's own serial number. If the comparison fails, then the boot\_fail tamper flag is set and authentication is aborted.

## VERSION

If SBIC revocation is enabled by U\_MSS\_REVOCATION\_ENABLE, the SBIC is rejected unless the value of VERSION is greater than or equal to the revocation threshold.

#### SBIC REVOCATION OPTION

If SBIC revocation is enabled by U\_MSS\_REVOCATION\_ENABLE and OPTIONS[0] is '1', all the SBIC versions less than VERSION are revoked upon complete authentication of the SBIC. The revocation threshold remains at the new value until it increments again by a future SBIC with OPTIONS[0] = '1' and a higher VERSION field. The revocation threshold may only be incremented using this mechanism and can only be reset by a bit-stream.

When the revocation threshold is updated dynamically, the threshold is stored using the redundant storage scheme used for passcodes such that a power failure during device boot does not cause a subsequent device boot to fail. If the update of revocation threshold fails, it is guaranteed that the threshold value is either the new value or the previous one.

| Offset<br>(bytes) | Size (bytes) | Name                    | Description                          |

|-------------------|--------------|-------------------------|--------------------------------------|

| 0                 | 4            | U_MSS_SBIC_ADDR         | Address of SBIC in MSS address space |

| 4                 | 4            | U_MSS_REVOCATION_ENABLE | Enable SBIC revocation if non-zero   |

The following figure shows the factory secure boot flow.

#### Figure 2-26. Factory Secure Boot Flow

# 2.5 MSS User Boot (For PolarFire SoC FPGA Only)

MSS user boot takes place when the control is given from System Controller to MSS Core Complex. Upon successful MSS pre-boot, System Controller releases the reset to the MSS Core Complex. MSS can be booted up in one of the following ways:

- Bare Metal Application

- Linux Application

- AMP Application

For more information about MSS booting, see PolarFire SoC Software Development and Tool Flow User Guide.

# 2.6 HSIO/GPIO Bank Initialization

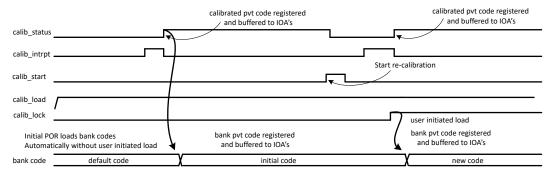

Unused GPIO and HSIO banks can be left powered down or powered up. During the device power-up, the used GPIO and HSIO banks are simultaneously powered up along with all the other power supplies. All of the banks are initialized automatically with Flash configuration bits when fabric is powered up. All of the powered-up user IOs (HSIO/GPIO) go through an initial PVT calibration on power-up.

The time at which IOs are functional depends on a combination of the following:

- Device boot

- · Ramp-up time of the power applied to the IO banks

- · Calibration time of IOs (For example, DDR interfaces)

For low-speed operations below 100 MHz, IOs are functional after the power applied to IO banks exceeds the threshold levels. When GPIO is mapped to the OUTPUT PAD signals, the drive strength is weakened when initial calibration is complete. This occurs because the initial pre-calibrated drive strength is at maximum calibration code until IO calibration status/AUTOCALIB\_DONE signal is asserted. It is recommended to monitor the IO calibration status/AUTOCALIB\_DONE signal for both high-speed and low-speed signals because of the drive strength change.

If the user requires the IOs to be usable immediately upon completion of device boot, the IO power ramp time must be sufficiently short. The user can also apply slow or delayed IO power ramp times on IO banks to delay the time until which the IOs are usable. If the user is applying slow ramp rates to IO banks power supplies, the user logic in the fabric must monitor the state of the IO banks to know when they are usable as low-speed IOs.

#### Figure 2-27. Ramp-up Time

| I/O Bank Settings                          |                                                                                         |              | ? ×    |

|--------------------------------------------|-----------------------------------------------------------------------------------------|--------------|--------|

| Bank                                       |                                                                                         |              |        |

| Choose Bank: Bank2 - GPIO 🔽 Lock           | ed                                                                                      |              |        |

| Attributes                                 |                                                                                         |              |        |

| Auto Calibration                           |                                                                                         |              |        |

| Auto Calibration Ramp Time (ms) 50         |                                                                                         |              | -      |

| Voltage Selection                          |                                                                                         |              |        |

| Range                                      | Min T                                                                                   | ypical       | Max    |

| VDDI: Unassigned                           | N/A                                                                                     | N/A          | N/A    |

| VREF:                                      |                                                                                         |              |        |

| Use VREF default pins                      |                                                                                         |              |        |

| How to handle placed macros incompatible w | ith VDDI/VREF                                                                           |              |        |

| Unplace them                               |                                                                                         |              |        |

| C Change I/O technology to be compatible   |                                                                                         |              |        |

| Available Technologies                     | Disabled                                                                                | l Technologi | es     |

|                                            | BUSLVDSE25<br>HCSL25<br>HCSL33<br>HSTL15I<br>HSTL15II<br>HSUL18I<br>HSUL18II<br>LCMDS25 |              | •      |

| Help                                       | C                                                                                       | ж            | Cancel |

The high-speed IO calibration process occurs automatically. The user's design in the FPGA fabric must monitor the completion of IO calibration or AUTOCALIB\_DONE to use the IOs for high-speed applications. The status of

the IO calibration and bank power supply can be monitored using the status signals of the PolarFire/PolarFire SoC Initialization Monitor IP. The following figure shows Auto calibration timeout settings. Configure the Timeout option based on selected GPIO or HSIO in the user design.

| Figure | 2-28. | Auto | Calibration | Timeout |

|--------|-------|------|-------------|---------|

|--------|-------|------|-------------|---------|

| Reports 8 × StartPage 8 × top.                                                                                                                                              | .v B × PF_IOD_GENERIC_TX_CO.    | v 🗗 🗙 📔 Constraint Manage               | er 🗗 🗙 Design and Memory Initial          | ization 🗗 × 🛛 5 top 🗗 ×        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------|-------------------------------------------|--------------------------------|

| Design Initialization UPROM SNVM SPI Flash                                                                                                                                  | Fabric RAMs                     |                                         |                                           |                                |

| Apply Discard Help                                                                                                                                                          |                                 |                                         |                                           |                                |

| In design initialization, user design blocks such as L                                                                                                                      |                                 | e initialized as an option using data s | tored in the non-volatile storage memory. |                                |

| The initialization data can be stored in µPROM, sNV                                                                                                                         |                                 |                                         |                                           |                                |

| Follow the below steps to program the initialization<br>1. Set up your fabric RAMs initialization data, if any<br>2. Define the storage location of the initialization data | y, using the 'Fabric RAMs' tab  |                                         |                                           |                                |

| 2. Define the storage location of the initialization of     3. Generate the initialization clients     4. Generate or export the bitstream                                  | sta                             |                                         |                                           |                                |

| 5. Program the device                                                                                                                                                       |                                 |                                         |                                           |                                |