#### Disco-Kraken PCB Drawings Index - EPON Based

Rev. 5-Oct-2023

| PDF<br>Page<br>Num | Subject                                | Drawing Numbers                                                                                                              |

|--------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

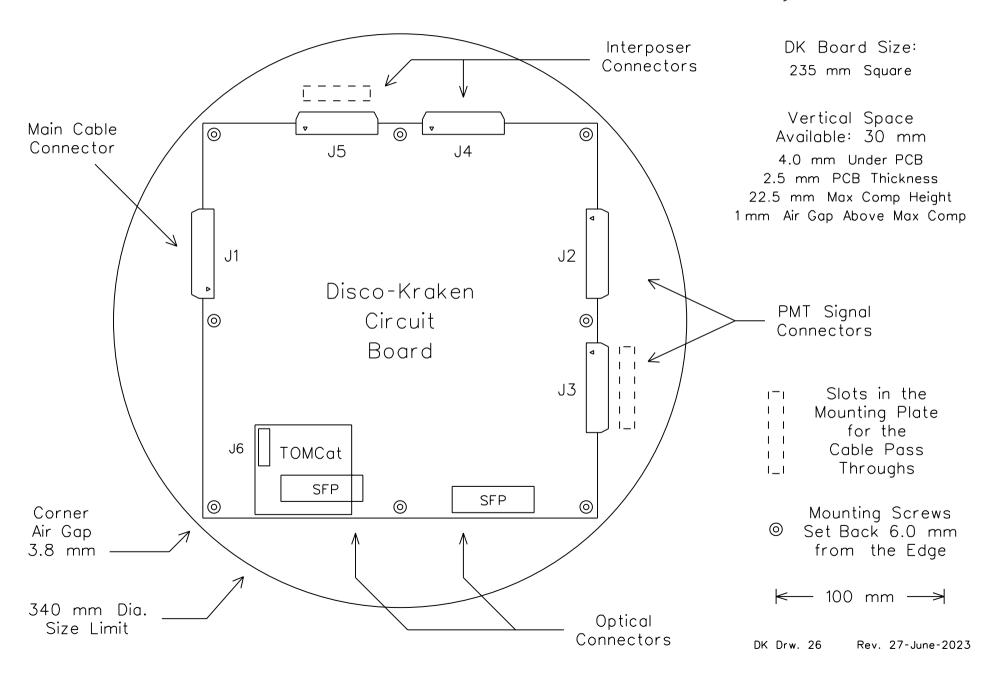

| 2                  | DK Board Size and General Layout:      | Drw. 26, 63                                                                                                                  |

| 4                  | Pin Layout FPGA/CPU MPFS250T-FCVG784:  | Drw. 25, 61                                                                                                                  |

| 6                  | FPGA/CPU 22 Power Loads                | Drw. 45                                                                                                                      |

| 7                  | FPGA/CPU 9 Power Feed Fills:           | bulk_1v2<br>bulk_3v3<br>core_1v05<br>digital_1v8<br>digital_2v5<br>fpga_p11_2v5<br>xcvr_1v05<br>xcvr_c1k_2v5<br>xcvr_p11_2v5 |

| 16                 | Layer Usage in this 10 Layer DK PCB De | esign Study                                                                                                                  |

| 17                 | PCB Physical Layers - Power Fills:     | physical_layer_3<br>physical_layer_5<br>physical_layer_6                                                                     |

| 20                 | BGA Escapes for DDR Memory             | ddr4_bga_escapes                                                                                                             |

| 21                 | Example 10 Layer Stackup from a Previo | ous High-Speed Design                                                                                                        |

All DK board design files are available on the web:

https://web.pa.msu.edu/people/edmunds/Disco\_Kraken/

### <u>Disco-Kraken - Board Size and Layout</u>

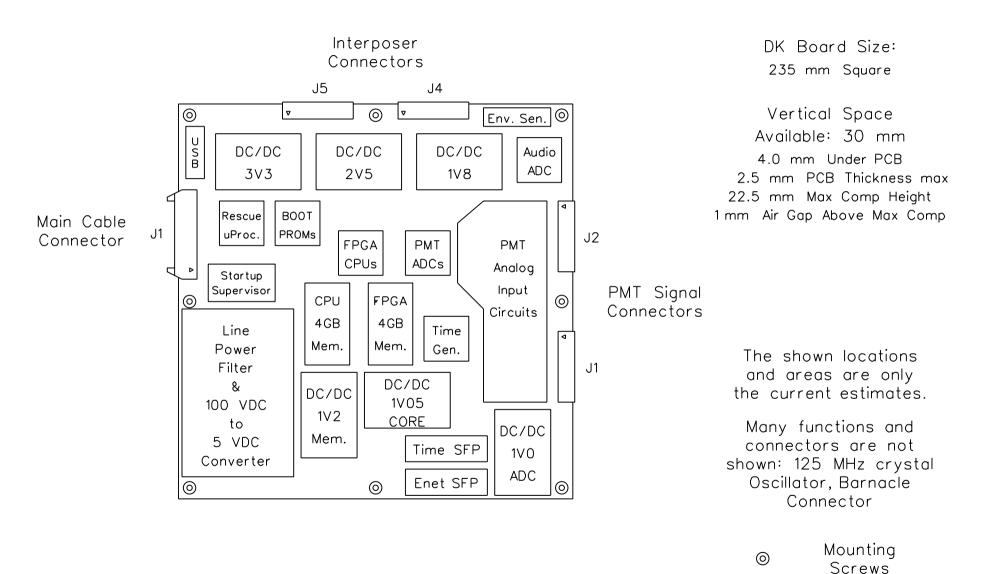

### <u>Disco-Kraken - PCB Floor Plan</u>

DK Drw. 63

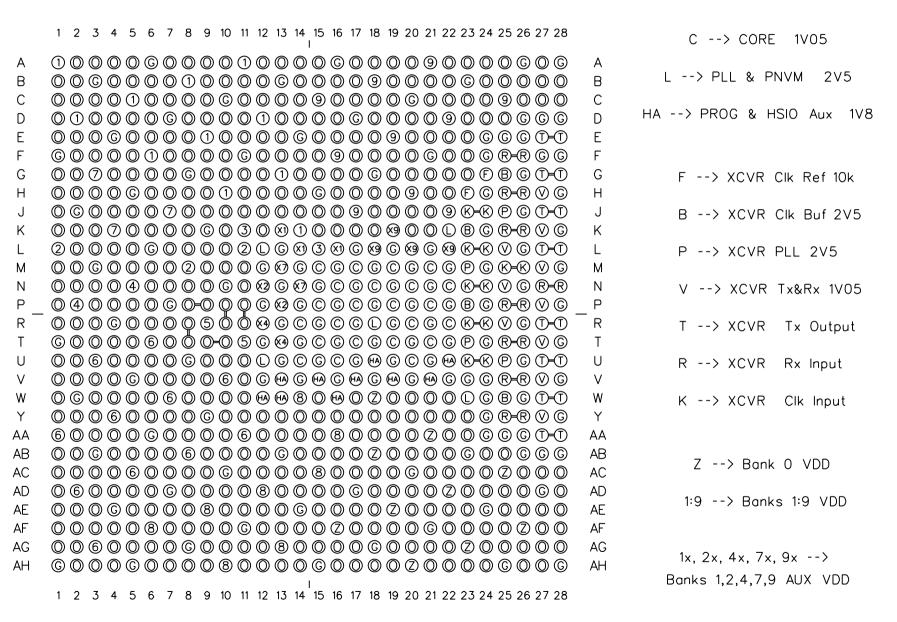

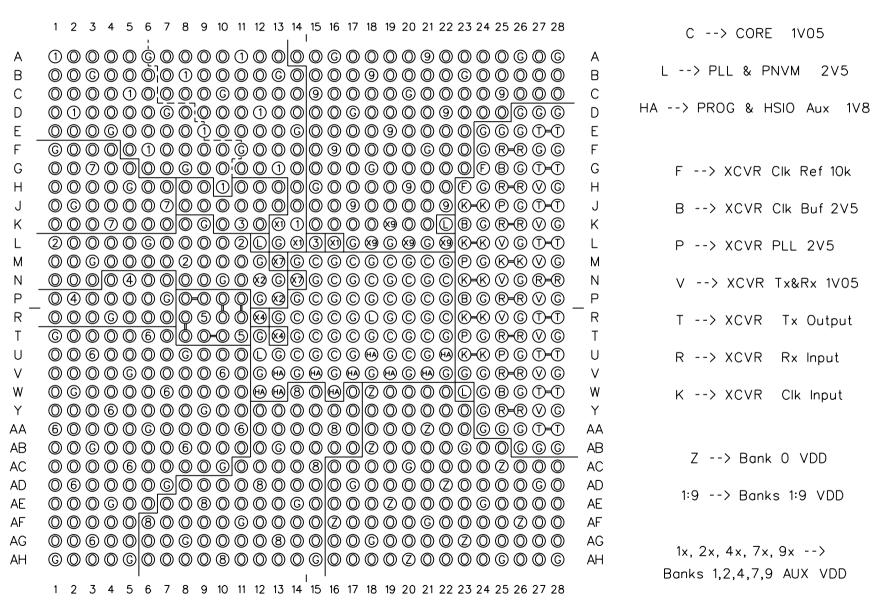

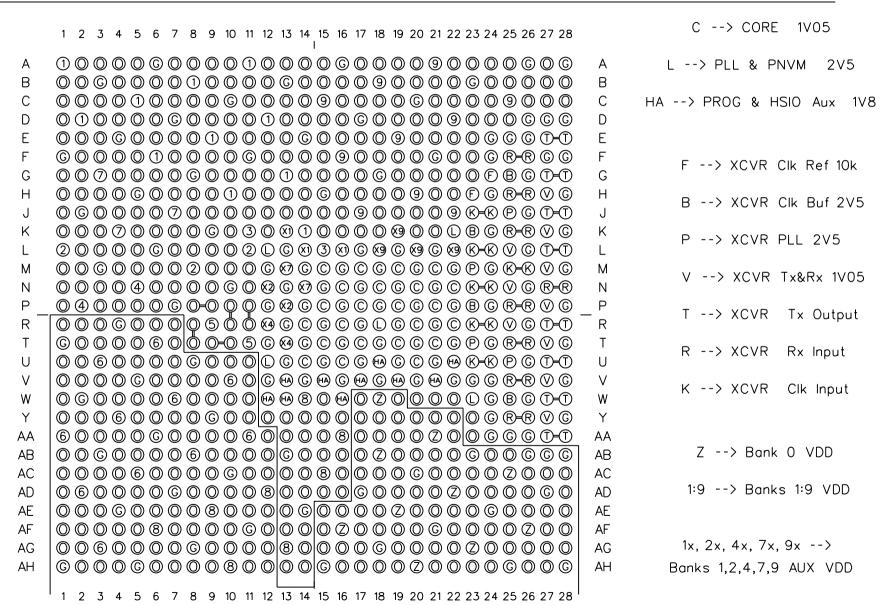

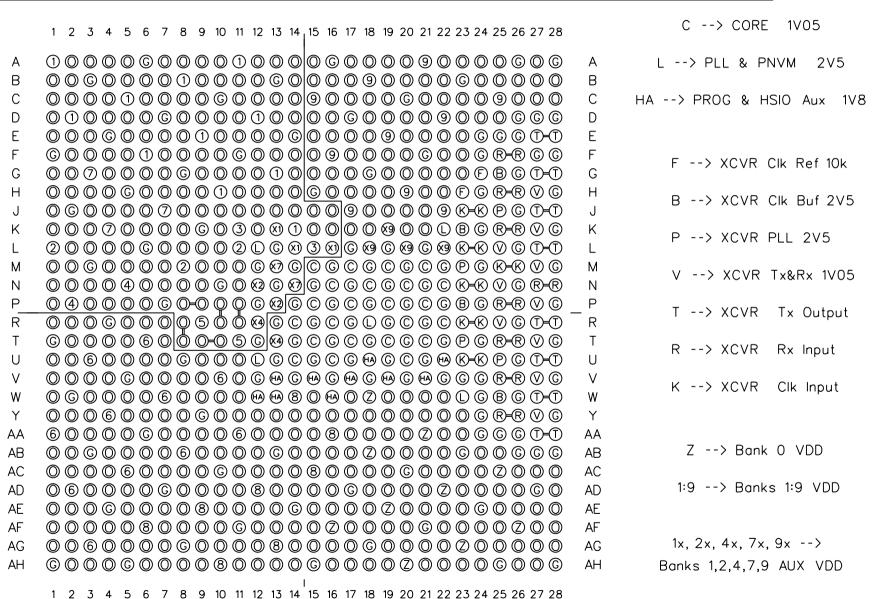

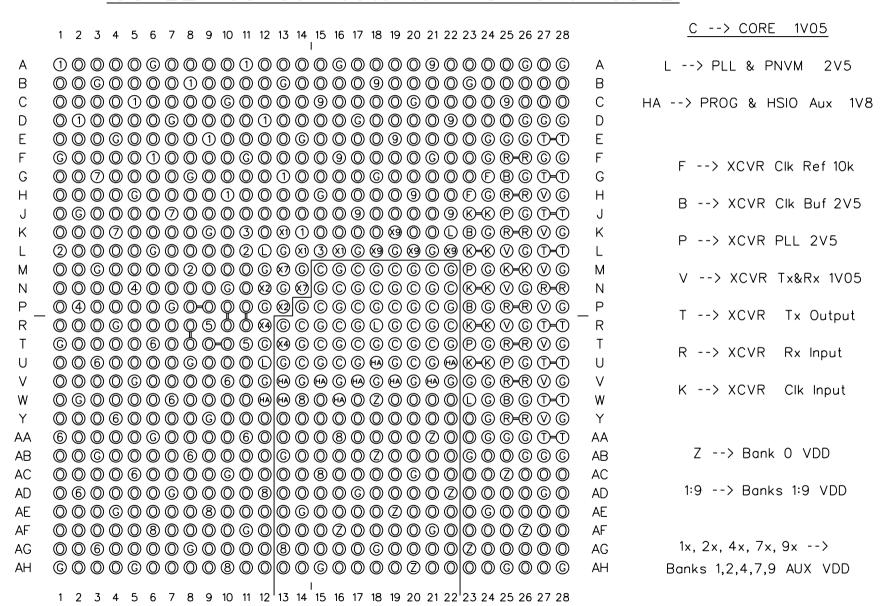

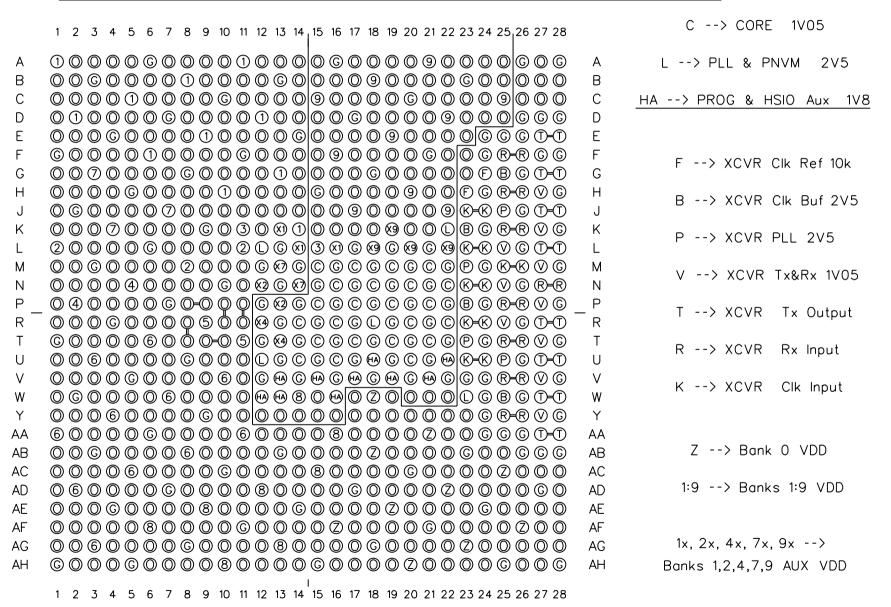

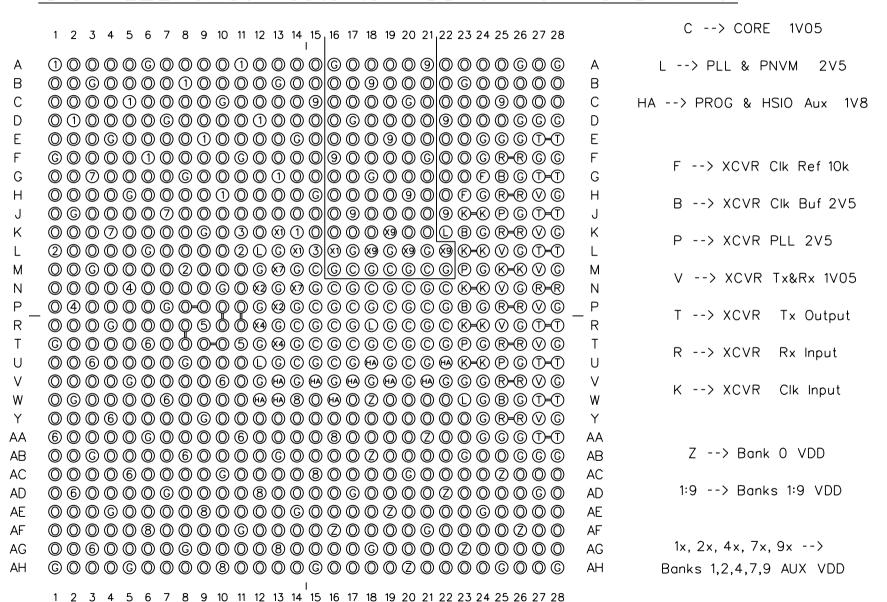

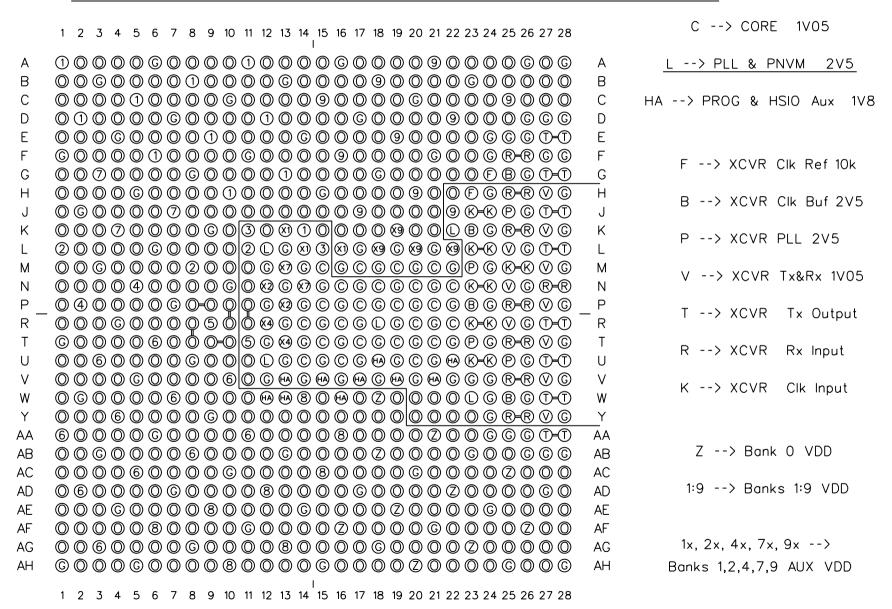

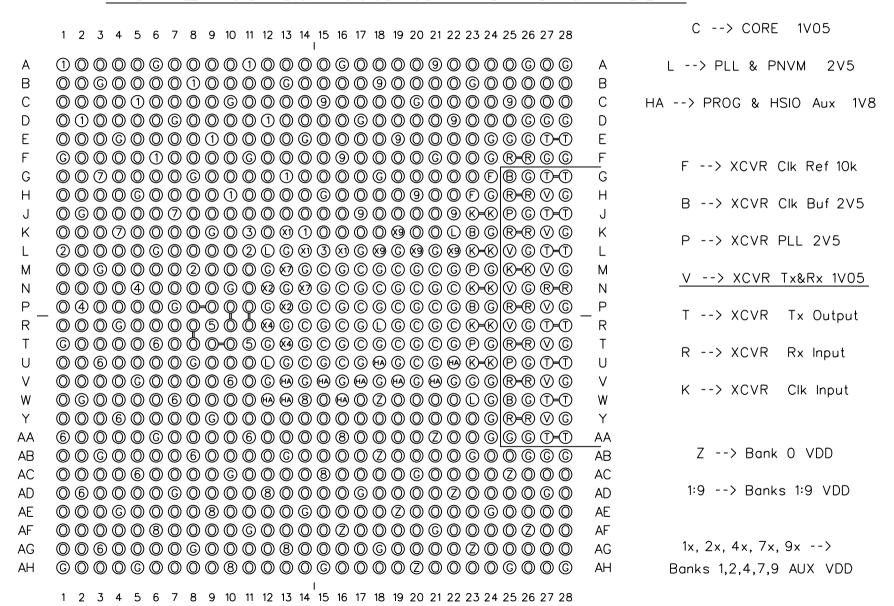

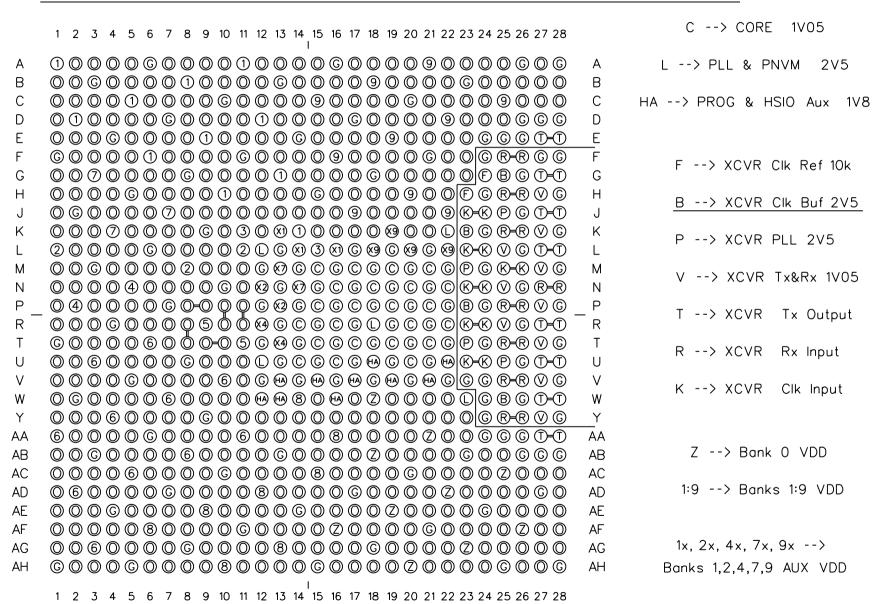

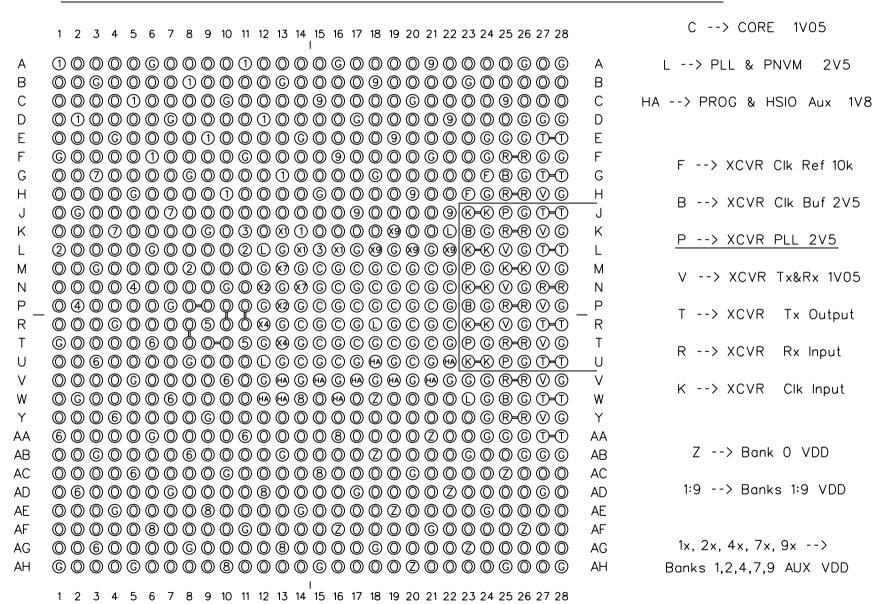

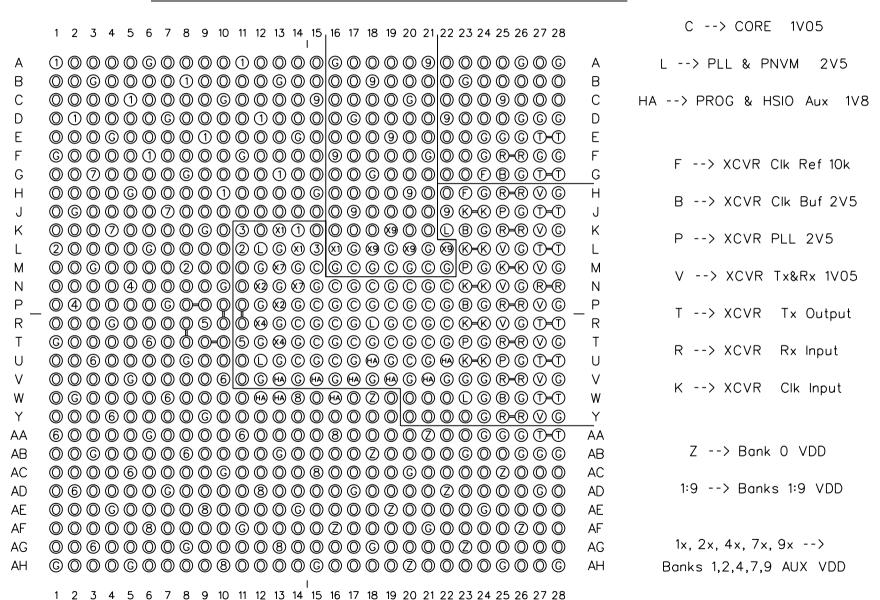

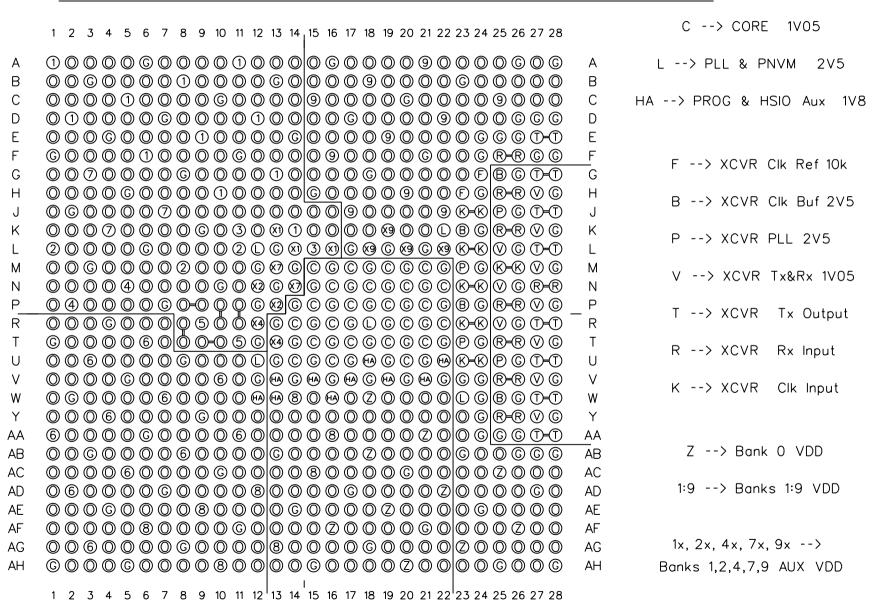

### MPFS25ØT-1FCVG784I

### MPFS25ØT-1FCVG784I I/O Banks

TOP VIEW

DK Drw. 61 Rev. 8-Sept-2023

### FPGA/CPU - Power Bus Connections

| <u>DK SUPPLY</u>  | Microchip<br>NAME | FUNCTION                                                            | DK SUPPLY                  | Microchip<br><u>NAME</u> | FUNCTION                                       |

|-------------------|-------------------|---------------------------------------------------------------------|----------------------------|--------------------------|------------------------------------------------|

| CORE_1VØ5         | VDD               | Core Supply                                                         | BULK_1V2                   | VDDIØ                    | I/O Bank Ø FPGA HSIO<br>FPGA DDR4 Memory       |

| DIGITAL_1V8       | VDD18             | Prgm & HSIO Aux                                                     | BULK_3V3<br>BULK_3V3       | * VDDI1<br>VDDAUX1       | I/O Bank 1 FPGA GPIO<br>DK's 3V3 I/O           |

| FPGA_PLL_2V5      | VDD25             | PLLs and PNVM                                                       | BULK_3V3<br>BULK_3V3       | * VDDI2<br>VDDAUX2       | I/O Bank 2 CPU I/O<br>USB UPLI & QSPI          |

| XCVR_1VØ5         | VDDA              | XCVR Power                                                          | BULK_3V3                   | VDDI3                    | I/O Bank 3 Controller<br>JTAG & Controller SPI |

| XCVR_PLL_2V5      | VDDA25            | XCVR PLLs                                                           | 10k Ohm Gnd<br>10k Ohm Gnd | * VDDI4<br>VDDAUX4       | I/O Bank 4 CPU I/O<br>Not Used No Power        |

| XCVR_CLK_2V5      | XCVR_CLK          | XCVR Clk Buffers                                                    | BULK_3V3                   | VDDI5                    | I/O Bank 5 CPU SGMII<br>Used only for CPU Clk  |

| 10k Ohm<br>to Gnd | XCVR_REF          | XCVR Clk Ref.                                                       | BULK_1V2                   | VDDI6                    | I/O Bank 6 CPU DDR<br>CPU DDR4 Memory          |

|                   |                   | a CPU IO Bank operates<br>hen that Bank's Auxiliary                 | BULK_3V3<br>BULK_3V3       | * VDDI7<br>VDDAUX7       | I/O Bank 7 FPGA GPIO<br>If Used It's 3V3       |

| supply must       | come from the     | same 2V5 or 3V3 bus.                                                | 10k Ohm Gnd                | VDDI8                    | I/O Bank 8 FPGA HSIO<br>Not Used No Power      |

| from 1V8 c        | or lower voltage  | a CPU IO Bank operates power then that Bank's see from the 2V5 bus. | DIGITAL_1V8<br>DIGITAL_2V5 | * VDDI9<br>VDDAUX9       | I/O Bank 9 FPGA GPIO<br>DK's 1V8 I/O           |

# DK Board - FPGA/CPU - Minimum BULK\_1V2 Plane BULK\_1V2 Connects to: I/O Banks 0 & 6 and DDR4 Memories

TOP VIEW

Rev. 11-Sept-2023

DK Planes Drw. 6

# DK Board - FPGA/CPU - Minimum BULK\_3V3 Plane BULK\_3V3 Connects to I/O Banks: 1, 1x, 2, 2x, 3, 5, 7, 7x

Rev. 11-Sept-2023

DK Planes Drw. 1

# DK Board - FPGA/CPU - Minimum CORE\_1V05 Plane CORE\_1V05 Connects to FPGA/CPU: CORE

TOP VIEW

Rev. 11-Sept-2023

DK Planes Drw. 5

# DK Board - FPGA/CPU - Minimum DIGITAL\_1V8 Plane DIGITAL\_1V8 Connects to: VDD18 and I/O Bank\_9

### DK Board - FPGA/CPU - Minimum DIGITAL\_2V5 Plane DIGITAL\_2V5 Connects to: VDDAUX for I/O BANK 9

#### DK Board - FPGA/CPU - Minimum FPGA\_PLL\_2V5 Plane <u>FPGA\_PLL\_2V5 Connects to FPGA/CPU: VDD25</u>

TOP VIEW

Rev. 11-Sept-2023

DK Planes Drw. 4

### DK Board - FPGA/CPU - Minimum XCVR\_1V05 Plane XCVR\_1V05 Connects to FPGA/CPU: VDDA

## DK Board - FPGA/CPU - Minimum XCVR\_CLK\_2V5 Plane XCVR\_CLK\_2V5 Connects to FPGA/CPU: XCVR\_CLK

# DK Board - FPGA/CPU - Minimum XCVR\_PLL\_2V5 Plane XCVR\_PLL\_2V5 Connects to FPGA/CPU: VDDA25

#### 10 Layer Stackup Study for the DK PCB

Current Rev. 4-Oct-2023

Study to see if DK can be routed on a balanced 10 Layer design.

| Layer | Function             | Copper<br>Weight |

|-------|----------------------|------------------|

| 1     | Traces and Pads      | 1/2 oz           |

| 2     | Gnd Plane            | 1/2 oz           |

| 3     | Traces & Power Fills | 1/2 oz           |

| 4     | Gnd Plane            | 1/2 oz           |

| 5     | Power Fills          | 1 oz             |

| 6     | Power Fills          | 1 oz             |

| 7     | Gnd Plane            | 1/2 oz           |

| 8     | Traces               | 1/2 oz           |

| 9     | Gnd Plane            | 1/2 oz           |

| 10    | Traces and Pads      | 1/2 oz           |

All trace layers (1, 3, 8, 10) must be able to support 76 & 100 Ohm differential trace pairs  $\,$  and  $\,$  40 & 50 Ohm single ended routes.

- The Zo of the differential pairs should come from a 50/50 balance of Ground Reference and opposite side reference.

- An approximate velocity match of the single ended microstrip and stripline is a big advantage.

All power routing will be done with fills on layers 3, 5, and 6. No power layer can be dedicated to a single rail.

# Physical Layer: 3 DIGITAL\_2V5 and FPGA\_PLL\_2V5

DK Planes Drw. 12

Rev. 11-Sept-2023

#### Physical Layer: 5

BULK\_3V3 and CORE\_1V05 and XCVR\_1V05

#### Physical Layer: 6

DIGITAL\_1V8 and BULK\_1V2 and XCVR\_CLK - XCVR\_PLL C --> CORE 1V05 1 2 3 4 5 6 7 8 9 10 11 12 13 14, 15 16 17 18 19 20 21 22 23 24 25, 26 27 28 L --> PLL & PNVM 2V5 С HA --> PROG & HSIO Aux 1V8 D F --> XCVR Clk Ref 10k Н Н B --> XCVR Clk Buf 2V5 Κ Κ P --> XCVR PLL 2V5 М V --> XCVR Tx&Rx 1V05 Ν Ν T --> XCVR Tx Output R R --> XCVR Rx Input U U ٧ K --> XCVR Clk Input W W Υ Υ AA AA  $Z \longrightarrow Bank O VDD$ AB AB AC AC 1:9 --> Banks 1:9 VDD AD ΑD ΑE ΑE ΑF ΑF 00600006000080|000600000000000 1x, 2x, 4x, 7x, 9x -->AG AG ΑН ΑН Banks 1,2,4,7,9 AUX VDD

Rev. 11-Sept-2023

DK Planes Drw. 11

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28

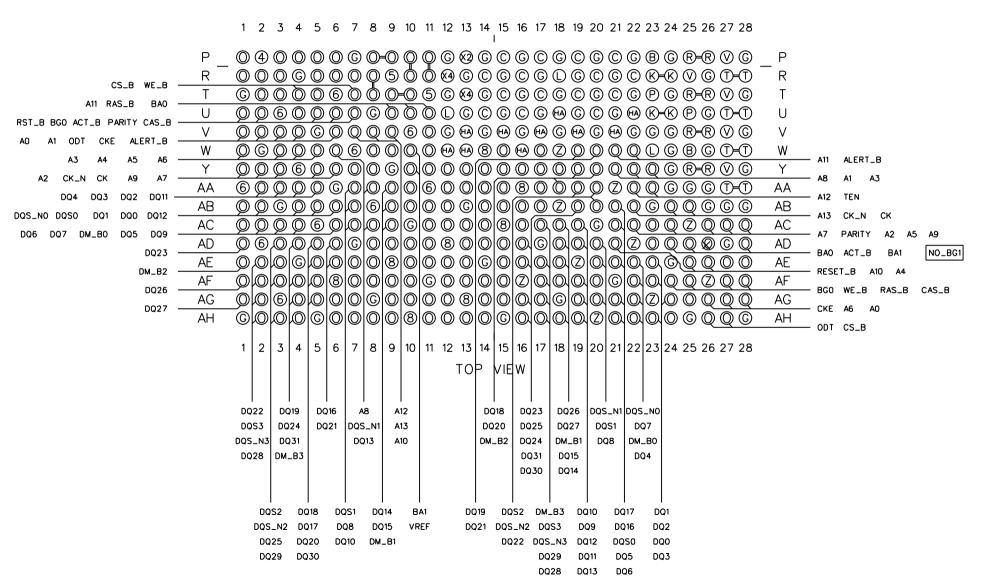

#### DDR4 Escapes from Banks: 0, 6

Viasystems Technologies Corp. LLC 8150 Sheppard Ave E Toronto, ON, M1B 5K2 Job Name: 181875

**Customer: DEBRON INDUSTRIAL ELECTRONICS**

Part Num: 40-00643-00LF

Part Rev : -

Engineer: Yogi Perin

| Layer      | Cust<br>Thickness | Calc<br>Thickness | Primary Stack            | Description                              | Dk / Df       |

|------------|-------------------|-------------------|--------------------------|------------------------------------------|---------------|

| Layer - 1  | Tilleniess        | 0.0005<br>0.0020  | Timaly Stack             | Taiyo 4000-HFX DI<br>1/2oz Mix (Std Plt) | 3.50 / 0.0190 |

| Layer - 2  |                   | 0.0038<br>0.0006  | 1080 - 71%               | FR408HR<br>1/2oz P/G                     | 3.42 / 0.0098 |

| Layer - 2  |                   | 0.0100            | 0.0100<br>(2-2116)       | FR408HR                                  | 3.69 / 0.0089 |

| Layer - 3  |                   | 0.0006<br>0.0040  | 3313 - 63%               | <b>1/2oz Sig</b><br>FR408HR              | 3.48 / 0.0096 |

| Layer - 4  |                   | 0.0006<br>0.0180  | 0.018                    | 1/2oz P/G<br>FR408HR                     | 3.90 / 0.0083 |

| Layer - 5  |                   | 0.0012            | (3-1652)                 | 1oz Mix                                  | 3.30 / 0.0003 |

|            |                   | 0.0078            | 2116 - 55%<br>2113 - 57% | FR408HR                                  | 3.64 / 0.0091 |

| Layer - 6  |                   | 0.0012<br>0.0180  | 0.018                    | <b>1oz Mix</b><br>FR408HR                | 3.90 / 0.0083 |

| Layer - 7  |                   | 0.0006            | (3-1652)                 | 1/2oz P/G                                |               |

| Layer - 8  |                   | 0.0040<br>0.0006  | 3313 - 63%               | FR408HR<br><b>1/2oz Sig</b>              | 3.48 / 0.0096 |

| Layer - 9  |                   | 0.0100<br>0.0006  | 0.0100<br>(2-2116)       | FR408HR<br><b>1/2oz P/G</b>              | 3.69 / 0.0089 |

| Layer - 10 |                   | 0.0038            | 1080 - 71%               | FR408HR<br>1/2oz Mix (Std Plt)           | 3.42 / 0.0098 |

| Layer - 10 |                   | 0.0005            |                          | Taiyo 4000-HFX DI                        | 3.50 / 0.0190 |

Materials: Isola FR408HR High Speed High-Tg FR4

| Requirement              | Req. Thickness | Tol +                | Tol -  | Calc Thick |  |

|--------------------------|----------------|----------------------|--------|------------|--|

| Incl. Plating & Mask     | 0.0940         | 0.0940 0.0094 0.0094 |        | 0.0904     |  |

| Incl. Mask over Laminate | 0.0900         | 0.0090               | 0.0090 | 0.0864     |  |

| Incl. Plating            | 0.0930         | 0.0093               | 0.0093 | 0.0894     |  |

| After Lamination         | 0.0902         | 0.0045               | 0.0045 | 0.0866     |  |

| Over Laminate            | 0.0890         | 0.0089               | 0.0089 | 0.0854     |  |

#### Note

IPC-6012 has a minimum dielectric requirement of .003543" and any nominal dielectric .0045" or less may violate this requirement based on vendor tolerances and actual lamination yields. Accepting TTM's stackup will be taken as a waiver against this requirement. With this exception, minimum dielectric thickness shall be .000984". If this is not acceptable please advise immediately so options can be reviewed and discussed. If we do not get a response within 24 hours, we will proceed with this stackup. Please also be advised that accepting this stackup has no impact on TTM meeting IPC-6012 Class 2 or Class 3 requirements. Please also note that nominal targeted dielectric gaps of .0046" or greater shall have a minimum tolerance of +- .001" after lamination.

#### **Job Comment**

6 different back drills required.

| Impedance Type                 | Layer | Design  | Actual | Pitch  | Plane | Target | Tol<br>(ohms) | Predict |

|--------------------------------|-------|---------|--------|--------|-------|--------|---------------|---------|

| 1 EC Microstrip                | L1    | 0.00550 | 0.0055 | 0.0157 | -     |        |               |         |

| © 2014 TTM All rights recorded |       | 0.00550 | 0.0055 | -      | L2    | 100    | 10            | 101.98  |

3.2.10

Viasystems Technologies Corp. LLC 8150 Sheppard Ave E Toronto, ON, M1B 5K2

| Impedance Type  | Layer | Design  | Actual | Pitch  | Plane | Target | Tol<br>(ohms) | Predict |

|-----------------|-------|---------|--------|--------|-------|--------|---------------|---------|

| 2 EC Stripline  | L3    | 0.00550 | 0.0053 | 0.0157 | L2    | 100    | 10            | 100.85  |

|                 | -     | 0.00550 | 0.0053 | -      | L4    |        |               |         |

| 3 EC Stripline  | L8    | 0.00550 | 0.0053 | 0.0157 | L7    | 100    | 10            | 100.85  |

|                 | -     | 0.00550 | 0.0053 | -      | L9    |        |               |         |

| 4 EC Microstrip | L10   | 0.00550 | 0.0055 | 0.0157 | L9    | 400    | 40            | 404.00  |

|                 | -     | 0.00550 | 0.0055 | -      | -     | 100    | 10            | 101.98  |

Software Version 3.2.10

Stackup Report for 181875 6/1/2018 Page 2