# MOTOROLA SEMICONDUCTOR TECHNICAL DATA

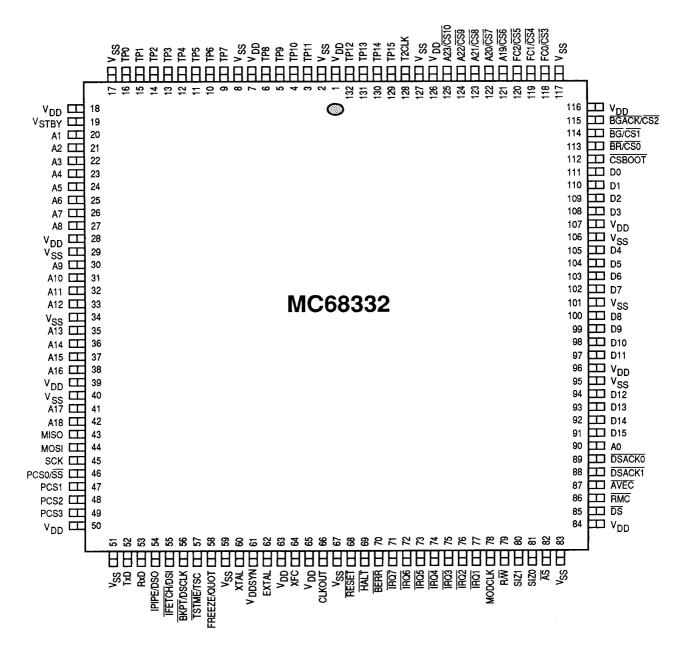

MC68332

# Technical Summary 32-Bit Microcontroller

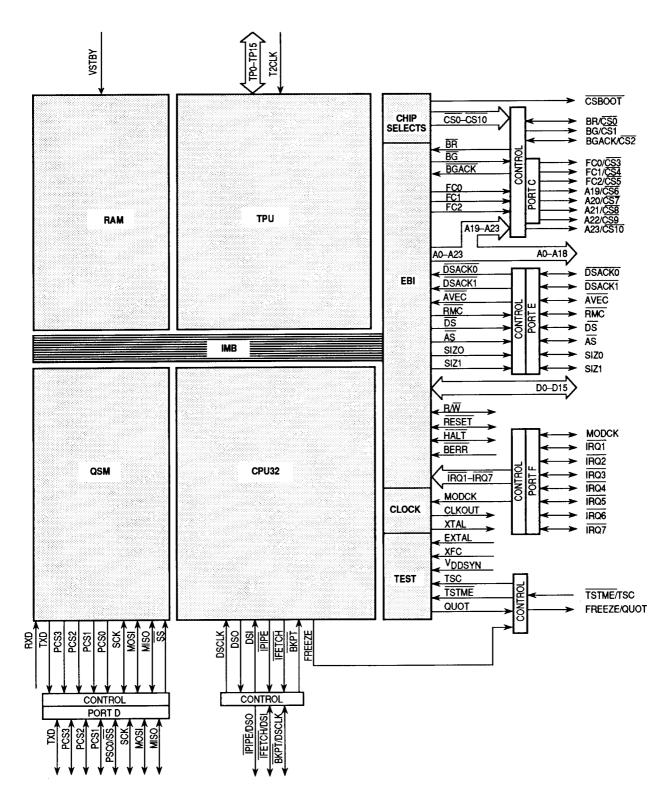

The MC68332, a 32-bit highly integrated microcontroller, combines high-performance data manipulation capabilities with powerful peripheral subsystems: the system integration module (SIM), the queued serial module (QSM), and the time processor unit (TPU). All are connected to the CPU32 through the intermodule bus (IMB). The MC68332 is the first member of the M68300 Family of modular embedded controllers featuring fully static, high-speed complementary metal-oxide semiconductor (CMOS) technology. Based on the powerful MC68020, the CPU32 instruction processing module provides enhanced system performance and also uses the extensive software base for the Motorola M68000 Family.

#### **Features**

- Modular Architecture in a Single Chip

- CPU: 32-Bit M68000 Family (CPU32):

- Upward Object-Code Compatible from the MC68010

- New Instruction for Controller Applications

- Low-Power Operation:

- --- 600 mW Maximum

- 500 μW in Standby Mode

- Frequency, Software Programmable:

- On-Chip Phase-Locked Loop (PLL), 131 kHz to 16.78 MHz (5-V Supply)

- -Uses Inexpensive 32.768-kHz Watch Crystal

- Technology:

- 1-Micron High-Density Complementary Metal-Oxide Semiconductor (HCMOS)

- Static Design

- Transistor Count: 422,000

- Package:

- 132-Pin Plastic Quad Flat Pack (PQFP)

- Intelligent 16-Bit Time Processor Unit (TPU):

- Dedicated Microengine Operating Independently of CPU32

- 16 Independent, Programmable Channels and Pins

- Any Channel Can Perform Any Time Function (Input Capture (IC), Output Compare (OC), Pulse-Width Modulation (PWM), Stepper Motor (SM), etc.)

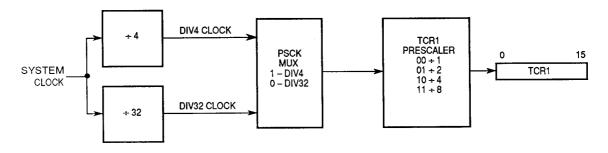

- Two Timer Count Registers with Programmable Prescalers

- Selectable Channel Priority Levels

- Two Serial Input/Output (I/O) Subsystems:

- Enhanced Serial Communications Interface (SCI) Universal Asynchronous Receiver Transmitter (UART) with Parity and Programmable Baud Rate Modulus Counter

- Enhanced Serial Peripheral Interface with I/O Queue (QSPI)

- On-Chip Memory: 2K Bytes Standby RAM

- On-Chip, Programmable, Chip-Select Logic:

- Up to 12 Signals for Memory and Peripheral I/O

- System Failure Protection:

- Software Watchdog Timer

- Periodic Interrupt Timer

- M68000 Family Spurious Interrupt, HALT, and Bus Timeout Monitors

- Up to 32 Discrete I/O Pins

This document contains information on a new product. Specifications and information herein are subject to change without notice.

© MOTOROLA INC., 1991

This Page Intentionally Left Blank\_

MOTOROLA 2

# **Table of Contents**

| MC68332 Overview                              |    |

|-----------------------------------------------|----|

| Standard MC68332 Ordering Information         |    |

| MC68332 Block Diagram                         | 5  |

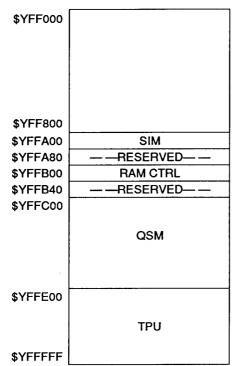

| MC68332 Module Memory Map                     | 6  |

| Central Processor Unit (CPU32)                | 7  |

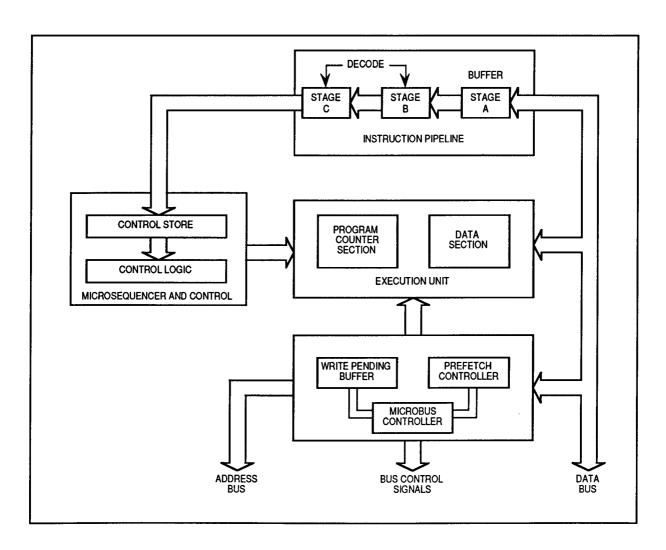

| CPU32 Block Diagram                           | 8  |

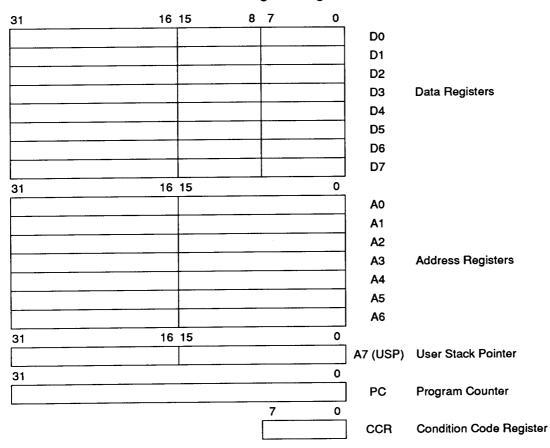

| User Programming Model                        | 9  |

| Instruction Set Summary                       | 11 |

| Background Mode Command Summary               | 12 |

| System Integration Module (SIM)               | 13 |

| System Configuration and Protection Submodule | 14 |

| Clock Synthesizer (System Clock)              |    |

| Chip Selects                                  |    |

| External Bus Interface                        |    |

| SIM Register Map                              |    |

| SIM Registers                                 | 21 |

| Queued Serial Module (QSM)                    | 36 |

| QSPI Submodule                                | 36 |

| SCI Submodule                                 |    |

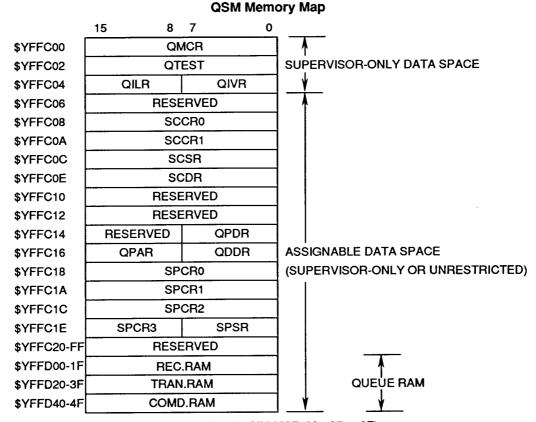

| QSM Memory Map                                |    |

| QSM Registers                                 |    |

| Standby Ram (with TPU Emulation)              |    |

| RAM Module Programmer's Model                 | 52 |

| Standby Ram Registers                         | 53 |

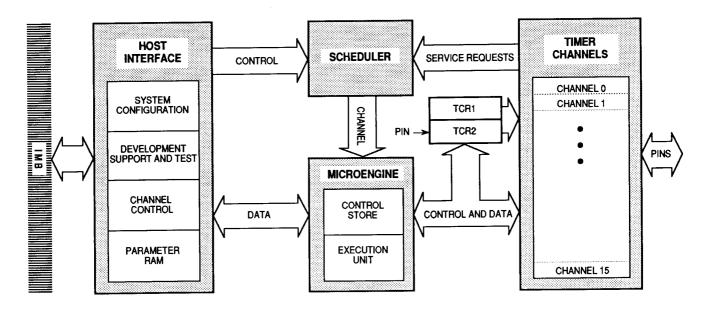

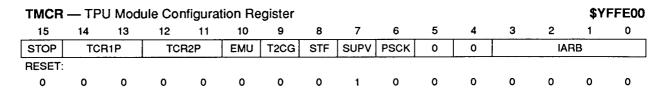

| Time Processor Unit (TPU)                     | 54 |

| Register Map                                  | 57 |

|                                               | 58 |

#### **Pin Assignments**

#### Standard MC68332 Ordering Information

| Package Type                       | Frequency<br>(MHz) | Temperature    | Order Number                                                             |

|------------------------------------|--------------------|----------------|--------------------------------------------------------------------------|

| Ceramic Surface Mount<br>FE Suffix | 16.78              | -40°C to +85°C | XC68332FE (now)<br>MC68332FE (1Q91)<br>SPAKXC68332FE*<br>SPAKMC68332FE*  |

| Plastic Surface Mount<br>FC Suffix | 16.78              | -40°C to +85°C | XC68332FC (1Q91)<br>MC68332FC (2Q91)<br>SPAKXC68332FC*<br>SPAKMC68332FC* |

<sup>\*</sup>These are sample packs and must be ordered in multiples of two parts and are shipped in special cases.

MC68332 Block Diagram

#### MC68332 Module Memory Map

RAM ARRAY (2.0K BYTES)

| Module   | Size    |      |      | Base |      |      |      |          |

|----------|---------|------|------|------|------|------|------|----------|

|          | (Bytes) | A23  | _    | A12  | A11  | _    | A0   | Address  |

| SIM      | 128     | M111 | 1111 | 1111 | 1010 | 0XXX | XXXX | \$YFFA00 |

| RAM CTRL | 64      | M111 | 1111 | 1111 | 1011 | 00XX | XXXX | \$YFFB00 |

| QSM      | 512     | M111 | 1111 | 1111 | 110X | 0XXX | XXXX | \$YFFC00 |

| TPU      | 512     | M111 | 1111 | 1111 | 111X | 0XXX | XXXX | \$YFFE00 |

Y = M111, where M is the modmap signal state on the IMB, which reflects the state of the modmap bit in the module configuration register of the system integration module (Y = \$7 or \$F).

#### Central Processor Unit (CPU32)

The CPU32 is fully object code compatible with the M68000 Family, which excels at processing calculation-intensive algorithms and supporting high-level languages. The CPU32 supports all of the MC68010 and most of the MC68020 enhancements, such as virtual memory support, loop mode operation, instruction pipeline, and 32-bit mathematical operations. Powerful addressing modes provide compatibility with existing software programs and increase the efficiency of high-level language compilers. New instructions, such as table lookup and interpolate, and low-power stop, support the specific requirements of controller applications. Also included is the background debug mode, an alternate operating mode that suspends normal operation and allows the CPU to accept debugging commands from the development system.

#### **Features**

- Fully Object Code Compatible with M68000 Family

- Virtual Memory Implementation (Instruction Restart Method)

- Loop Mode of Instruction Execution (Faster Execution of Certain Instructions)

- · Fast Multiply, Divide, and Shift Instructions

- · Fast Bus Interface with Dynamic Bus Port Sizing

- Improved Exception Handling for Controller Applications

- Enhanced Addressing Modes

- Scaled Index

- Address Register Indirect with Base Displacement and Index

- Expanded PC Relative Modes

- 32-Bit Branch Displacements

- Instruction Set Enhancements

- High-Precision Multiply and Divide

- Trap on Condition Codes

- Upper and Lower Bounds Checking

- Enhanced Breakpoint Instruction

- Table Lookup and Interpolate Instruction

- Low-Power Stop Instruction

- · Hardware Breakpoint Signal, Background Mode

- 16.78-MHz Operating Frequency at –40 to 85°C

- · Fully Static Implementation

#### **Architecture Summary**

The CPU32 architecture includes several important features that provide both power and versatility to the user. The CPU32 is source and object code compatible with the MC68000 and MC68010. All user state programs can be executed unchanged. The major CPU32 features are as follows:

- 32-Bit Internal Data Path and Arithmetic Hardware 16-Bit External Data Bus

- 32-Bit Internal Address Bus 24-Bit External Address Bus

- Rich Instruction Set

- Eight 32-Bit General-Purpose Data Registers

- Seven 32-Bit General-Purpose Address Registers

- Separate User and Supervisor Stack Pointers and Address Spaces

- Separate Program and Data Address Spaces

- Flexible Addressing Modes

- Full Interrupt Processing

#### **Data Types**

Six basic data types are supported:

- Bits

- Packed Binary Coded Decimal Digits

- Byte Integers (8 bits)

- Word Integers (16 bits)

- Long-Word Integers (32 bits)

- Quad-Word Integers (64 bits)

**CPU32 Block Diagram**

#### **User Programming Model**

# **Supervisor Programming Model Supplement**

SR — Status Register

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|--|

| T1 | ТО | S  | 0  | 0  | 12 | I1 | 10 | 0 | 0 | 0 | X | N | Z | V | С |  |

#### Status Register

System Byte

T1-T0 - Trace Enable

S — Supervisor/User State

Bits 12-11 — Unimplemented

12-10 — Interrupt Priority Mask

User Byte (Condition Code Register)

Bits 7-5 — Unimplemented

X — Extend

N — Negative

Z — Zero

V — Overflow

C — Carry

# **Instruction Set Summary**

| Mnemonic                                                               | Description                                                                                                                                                                                    |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABCD<br>ADD<br>ADDA<br>ADDI<br>ADDQ<br>ADDX<br>AND<br>ANDI<br>ASL, ASR | Add Decimal with Extend Add Add Address Add Immediate Add Quick Add with Extend Logical AND Logical AND Immediate Arithmetic Shift Left and Right                                              |

| Bcc<br>BCHG<br>BCLR<br>BGND<br>BKPT<br>BRA<br>BSET<br>BSR<br>BTST      | Branch Conditionally Test Bit and Change Test Bit and Clear Background Breakpoint Branch Test Bit and Set Branch to Subroutine Test Bit                                                        |

| CHK, CHK2  CLR  CMP  CMPA  CMPI  CMPM  CMP2                            | Check Register Against Upper<br>and Lower Bounds<br>Clear<br>Compare<br>Compare Address<br>Compare Immediate<br>Compare Memory to Memory<br>Compare Register Against<br>Upper and Lower Bounds |

| DBcc<br>DIVS, DIVSL<br>DIVU, DIVUL                                     | Test Condition, Decrement and<br>Branch<br>Signed Divide<br>Unsigned Divide                                                                                                                    |

| EOR<br>EORI<br>EXG<br>EXT, EXTB                                        | Logical Exclusive OR<br>Logical Exclusive OR Immediate<br>Exchange Registers<br>Sign Extend                                                                                                    |

| LEA<br>LINK<br>LPSTOP<br>LSL, LSR                                      | Load Effective Address<br>Link and Allocate<br>Low Power Stop<br>Logical Shift Left and Right                                                                                                  |

| ILLEGAL                                                                | Take Illegal Instruction Trap                                                                                                                                                                  |

| JMP<br>JSR                                                             | Jump<br>Jump to Subroutine                                                                                                                                                                     |

| Mnemonic                                                           | Description                                                                                                                                                                                       |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVE MOVE CCR MOVE SR MOVE USP MOVEA MOVEC MOVEM MOVEP MOVEQ MOVES | Move Move Condition Code Register Move Status Register Move User Stack Pointer Move Address Move Control Register Move Multiple Registers Move Peripheral Move Quick Move Alternate Address Space |

| MULS, MULS.L<br>MULU, MULU.L                                       | Signed Multiply<br>Unsigned Multiply                                                                                                                                                              |

| NBCD<br>NEG<br>NEGX<br>NOP                                         | Negate Decimal with Extend<br>Negate<br>Negate with Extend<br>No Operation                                                                                                                        |

| OR<br>ORI                                                          | Logical Inclusive OR Logical Inclusive OR Immediate                                                                                                                                               |

| PEA                                                                | Push Effective Address                                                                                                                                                                            |

| RESET<br>ROL, ROR<br>ROXL, ROXR<br>RTD<br>RTE<br>RTR<br>RTS        | Reset External Devices Rotate Left and Right Rotate with Extend Left and Right Return and Deallocate Return from Exception Return and Restore Codes Return from Subroutine                        |

| SBCD<br>Scc<br>STOP<br>SUB<br>SUBA<br>SUBI<br>SUBQ<br>SUBX<br>SWAP | Subtract Decimal with Extend Set Conditionally Stop Subtract Subtract Address Subtract Immediate Subtract Quick Subtract with Extend Swap Register Words                                          |

| TBLS,TBLSN<br>TBLU, TBLUN                                          | Table Lookup and Interpolate<br>(Signed)<br>Table Lookup and Interpolate<br>(Unsigned)                                                                                                            |

| TAS<br>TRAP<br>TRAPcc<br>TRAPV<br>TST                              | Test Operand and Set<br>Trap<br>Trap Conditionally<br>Trap on Overflow<br>Test Operand                                                                                                            |

| UNLK                                                               | Unlink                                                                                                                                                                                            |

# **Background Mode Command Summary**

| Command               | Mnemonic    | Description                                                                                                                                                                                                                               |

|-----------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read D/A Register     | RDREG/RAREG | Read the selected address or data register and return the results through the serial interface.                                                                                                                                           |

| Write D/A Register    | WDREG/WAREG | The data operand is written to the specified address or data register.                                                                                                                                                                    |

| Read System Register  | RSREG       | The specified system control register is read. All registers that can be read in supervisor mode can be read in background mode.                                                                                                          |

| Write System Register | WSREG       | The operand data is written into the specified system control register.                                                                                                                                                                   |

| Read Memory Location  | READ        | Read the sized data at the memory location specified by the long-word address. The source function code register (SFC) determines the address space accessed.                                                                             |

| Write Memory Location | WRITE       | Write the operand data to the memory location specified by the long-word address. The destination function code (DFC) register determines the address space accessed.                                                                     |

| Dump Memory Block     | DUMP        | Used in conjunction with the READ command to dump large blocks of memory. An initial READ is executed to set up the starting address of the block and retrieve the first result. Subsequent operands are retrieved with the DUMP command. |

| Fill Memory Block     | FILL        | Used in conjunction with the WRITE command to fill large blocks of memory. Initially,a WRITE is executed to set up the starting address of the block and supply the first operand. The FILL command writes subsequent operands.           |

| Resume Execution      | GO          | The pipe is flushed and refilled before resuming instruction execution at the current PC.                                                                                                                                                 |

| Patch User Code       | CALL        | Current program counter is stacked at the location of the current stack pointer. Instruction execution begins at user patch code.                                                                                                         |

| Reset Peripherals     | RST         | Asserts RESET for 512 clock cycles. The CPU is NOT reset by this command. Synonymous with the CPU RESET instruction.                                                                                                                      |

| No Operation          | NOP         | NOP performs no operation and can be used as a null command.                                                                                                                                                                              |

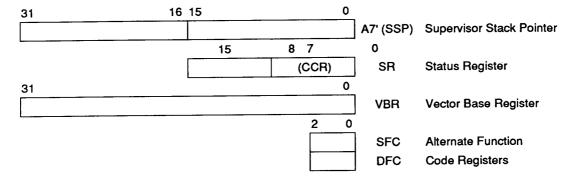

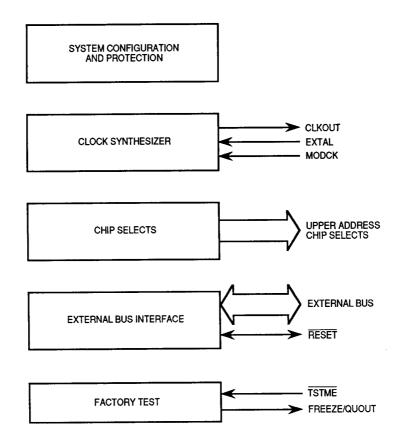

# System Integration Module (SIM)

The MC68332 system integration module (SIM) consists of five submodules that control the microcontroller unit (MCU) system startup, initialization, configuration, and external bus. This high level of integration requires very little or no external glue logic, as was necessary with MPU architectures of the past.

#### **Features**

- System Configuration and Protection

- Clock Synthesizer

- · Chip Selects

- External Bus Interface

System Integration Module (SIM) Block Diagram

#### **System Configuration and Protection Submodule**

This MCU is designed to provide maximum system safeguards and incorporates many of the functions that normally must be provided in external circuits.

#### **Features**

System Configuration

The module configuration register allows the user to configure the system according to the particular system requirements, such as enable slave mode, bus monitor, changing the module map, etc.

• Internal Bus Monitor

The MCU provides an internal bus monitor to check the DSACKx response time for all internal bus accesses and internally initiated external bus accesses.

Halt Monitor

A halt monitor causes a reset to occur if the CPU asserts an internal halt (HALT).

Spurious Interrupt Monitor

If no interrupt arbitration occurs during an interrupt acknowledge (IACK) cycle, the BERR signal is asserted internally.

Software Watchdog

The watchdog asserts reset if the software fails to service the software watchdog for a designated period of time (presumably because it is trapped in a loop or lost). There are four selectable timeout periods. A prescaler can be used for long timeout periods. The software watchdog is automatically enabled after reset.

Periodic Interrupt Timer

The MCU provides a timer to generate periodic interrupts, which can vary from 122  $\mu$ s to 15.94 s when using a 32.768-kHz crystal to generate the system clock.

· Reset Status Register

The reset status register shows the source of the last reset.

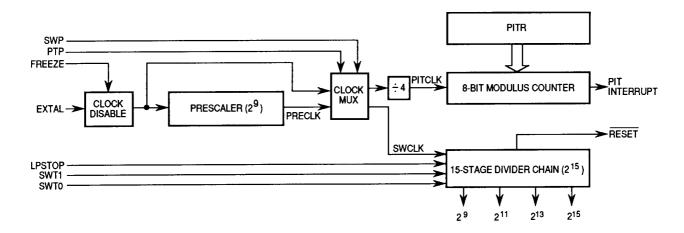

**System Configuration and Protection Submodule**

**Watchdog Timer**

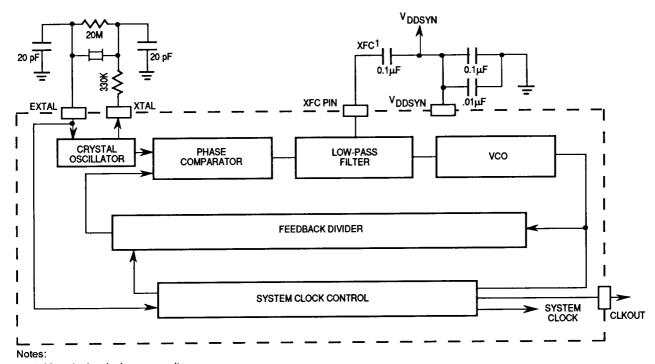

# **Clock Synthesizer (System Clock)**

The system clock, generated by an on-chip phase-locked-loop circuit, runs the device up to 16.78 MHz (current maximum operating frequency) from a 32.768-kHz watch crystal. The system speed can be changed dynamically under software control. With its fully static CMOS design, it is possible to stop the system clock completely, by using a low-power stop instruction, and still retain the contents of the registers and on-board RAM.

Must be low-leakage capacitor.

EXTAL can be driven with an external oscillator.

#### Clock Submodule Block Diagram

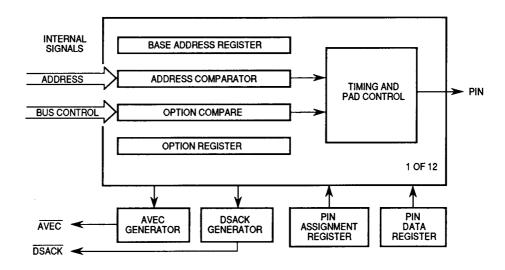

#### **Chip Selects**

Typical microcomputer systems require additional hardware to provide peripheral-select signals to external devices. The MC68332 integrates these functions on-chip, providing 12 independent programmable chip selects that can be set up as output enables, read or write strobes, or IACK signals. Block size is programmable from a minimum of 2K bytes to 1M byte in length. Accesses can be preselected for either 8- or 16-bit transfers. Up to 13 wait states can be programmed for insertion during the access. All bus interface signals are handled automatically by the chip-select logic.

#### **Features**

Twelve Programmable Chip-Select Circuits

Twelve chip-select signals are available (CSBOOT and CS10-CS0). The CSBOOT pin performs a single function because it functions after a reset with no initialization. The other chip-select circuits share functions on their output pins. All 12 chip select circuits are independently programmable from the same list of selectable features.

Variable Block Sizes

The block size, starting from the specified base address, can be programmed as 2K, 8K, 16K, 64K, 128K, 256K, 512K bytes or 1M byte.

• Both 8-Bit and 16-Bit Ports Supported

Eight-bit ports are accessible on both odd and even addresses when connected to data bus bits 15–8. Sixteen-bit ports can be accessed as odd bytes, even bytes, or as words.

MC68332 BR756/D Rev. 1 MOTOROLA

Read Only, Write Only, or Read/Write Capability

Chip selects, asserted in synchronization with read, write, or both read and write, are possible.

Address Strobe and Data Strobe Timing Option

Chip-select signals can be synchronized with either address strobe or data strobe, so that control signals such as output enable or write enable can be generated easily.

• Internal DSACK Generation with Wait States

The port size programmed in the pin assignment register can be referenced for generating DSACK and the proper number of wait states for a particular device programmed by the user.

Address Space Checking

Supervisor, User, and CPU space accesses can be checked optionally.

• Interrupt Priority Level Checking

In the IACK cycle, the acknowledged interrupt level can be compared with the user-specified level programmed in the option field. If autovector option is selected,  $\overline{\text{AVEC}}$  is asserted internally.

Discrete Output

Port C pins A22-A19 and FC2-FC0 can be programmed for discrete output.

• M6800-Type Peripheral Support

M6800-type peripherals that require an E clock for synchronization can be supported. Chip select is asserted, synchronized with the E clock on pin A23, providing correct data bus timing for the MCU.

**Chip-Select Circuit Block Diagram**

This Material Copyrighted By Its Respective Manufacturer

#### External Bus Interface

The external bus, based on the MC68020, provides 24 address lines and a 16-bit data bus. This data bus allows dynamic sizing between 8- and 16-bit data accesses. Read-modify-write cycles are provided through the RMC signal. A three-line handshaking interface accomplishes external bus arbitration.

The external bus interface provides the normal interface between the external system and the internal modules of the MCU and provides alternate functions and discrete I/O capability for many of the pins. The alternate functions of the chip-select circuitry can be determined by the state of the data bus pins at reset, or configured by pin assignment registers.

Refer to the system block diagram and the register descriptions for more information on alternate pin functions.

MC68332 BR756/D Rev. 1 MOTOROLA

# SIM Register Map (Sheet 1 of 2)

| FC         | ADDRESS          | 15 8                                  | 7 0                                                    | SUBMODULE          |  |  |  |  |  |

|------------|------------------|---------------------------------------|--------------------------------------------------------|--------------------|--|--|--|--|--|

| 101        | YFFA00           | MODULE CONFI                          |                                                        |                    |  |  |  |  |  |

| 101        | YFFA02           | MODULE T                              | EST (SIMTR)                                            | TEST               |  |  |  |  |  |

| 101        | YFFA04           | CLOCK SYNTHESIZE                      | CLOCK                                                  |                    |  |  |  |  |  |

| 101        | YFFA06           | UNUSED                                | EBI                                                    |                    |  |  |  |  |  |

| 101        | YFFA08           | MODULE TES                            | TEST                                                   |                    |  |  |  |  |  |

| 101        | YFFA0A           | UNUSED                                |                                                        |                    |  |  |  |  |  |

| 101        | YFFA0C           | UNUSED                                | UNUSED                                                 |                    |  |  |  |  |  |

| 101        | YFFA0E           | UNUSED                                | UNUSED                                                 |                    |  |  |  |  |  |

| X01        | YFFA10           | UNUSED                                | PORTE DATA (PORTE)                                     | EBI                |  |  |  |  |  |

| X01        | YFFA12           | UNUSED                                | PORTE DATA (PORTE)                                     |                    |  |  |  |  |  |

| X01        | YFFA14           | UNUSED                                | PORTE DATA DIRECTION (DDRE)                            |                    |  |  |  |  |  |

| 101        | YFFA16           | UNUSED                                | PORTE PIN ASSIGNMENT (PEPAR)                           |                    |  |  |  |  |  |

| X01        | YFFA18           | UNUSED                                | PORTE DATA (PORTE)                                     | ļ                  |  |  |  |  |  |

| X01        | YFFA1A           | UNUSED                                | PORTE DATA PURE CTION (PDRE)                           |                    |  |  |  |  |  |

| X01        | YFFA1C           | UNUSED                                | PORTE DIA ASSIGNMENT (PERAD)                           | l<br>FDI           |  |  |  |  |  |

| 101        | YFFA1E           | UNUSED                                | PORTF PIN ASSIGNMENT (PFPAR) SYSTEM PROTECTION CONTROL | EBI<br>EVE DROTECT |  |  |  |  |  |

| 101        | YFFA20           | UNUSED                                | SYS PROTECT                                            |                    |  |  |  |  |  |

| 101        | YYFA22           | PERIODIC INTERRU                      | MOD CONF                                               |                    |  |  |  |  |  |

| 101        | YFFA24           | PERIODIC INTERF                       | MOD CONF                                               |                    |  |  |  |  |  |

| 101        | YFFA26           | UNUSED                                | SOFTWARE SERVICE (SWSR)                                | SYS PROTECT        |  |  |  |  |  |

| 101        | YFFA28           | UNUSED                                |                                                        |                    |  |  |  |  |  |

| 101        | YFFA30           | TEST MODULE MASTI                     | TEST                                                   |                    |  |  |  |  |  |

| 101        | YFFA32           | TEST MODULE MASTI                     | ļ                                                      |                    |  |  |  |  |  |

| 101        | YFFA34           | TEST MODULE SHIFT COUNT.A<br>(TSTSCA) | TEST MODULE SHIFT COUNT.B<br>(TSTSCB)                  |                    |  |  |  |  |  |

| 101        | YFFA36           | TEST MODULE REPETI                    | TION COUNTER (TSTRC)                                   | ļ                  |  |  |  |  |  |

| 101        | YFFA38           | TEST MODULE O                         | CONTROL (CREG)                                         | 1                  |  |  |  |  |  |

| X01        | YFFA3A           |                                       | UTED REGISTER (DREG)                                   | TEST               |  |  |  |  |  |

|            | YFFA3C           | UNUSED                                | UNUSED                                                 |                    |  |  |  |  |  |

|            | YFFA3E           | UNUSED                                | UNUSED                                                 |                    |  |  |  |  |  |

| X01        | YFFA40           | UNUSED                                | PORT C DATA (CSPDR)                                    | CHIP SELECT        |  |  |  |  |  |

| X01        | YFFA42           | UNUSED                                | UNUSED                                                 | ļ                  |  |  |  |  |  |

| 101        | YFFA44           |                                       | SSIGNMENT (CSPAR0)                                     | ļ                  |  |  |  |  |  |

| 101        | YFFA46           |                                       | SSIGNMENT (CSPAR1)                                     |                    |  |  |  |  |  |

| 101        | YFFA48           |                                       | E BOOT (CSBARBT)                                       |                    |  |  |  |  |  |

| 101        | YFFA4A           |                                       | ON BOOT (CSORBT)                                       | ļ                  |  |  |  |  |  |

| 101        | YFFA4C           |                                       | ASE 0 (CSBAR0)                                         | ļ                  |  |  |  |  |  |

| 101        | YFFA4E           |                                       | PTION 0 (CSOR0)                                        | ļ                  |  |  |  |  |  |

| 101        | YFFA50           | CHIP-SELECT B                         | ļ                                                      |                    |  |  |  |  |  |

| 101        | YFFA52           |                                       | PTION 1 (CSOR1)                                        |                    |  |  |  |  |  |

| 101        | YFFA54           | CHIP-SELECT B                         |                                                        |                    |  |  |  |  |  |

| 101        | YFFA56           | CHIP-SELECT O                         |                                                        |                    |  |  |  |  |  |

| 101        | YFFA58           | CHIP-SELECT B<br>CHIP-SELECT O        | 1                                                      |                    |  |  |  |  |  |

| 101        | YFFA5A           |                                       | 1                                                      |                    |  |  |  |  |  |

| 101<br>101 | YFFA5C<br>YFFA5E | CHIP-SELECT B                         | I<br>CHIP SELECT                                       |                    |  |  |  |  |  |

| 101        | III MOE          | OHIF-SELECT O                         | 1 11014 4 (000114)                                     | Offil SELECT       |  |  |  |  |  |

MOTOROLA 20

|     |             | _                            | p (Sheet 2 of 2)             | SUBMODULE          |  |  |  |  |  |  |  |  |  |

|-----|-------------|------------------------------|------------------------------|--------------------|--|--|--|--|--|--|--|--|--|

| FC  | ADDRES<br>S | 15                           | 8 7                          | SOBMODULE          |  |  |  |  |  |  |  |  |  |

|     | _           |                              | ACE E (CCDADE)               | CHIP SELECT        |  |  |  |  |  |  |  |  |  |

| 101 | YFFA60      |                              | ASE 5 (CSBAR5)               | - Offile Selection |  |  |  |  |  |  |  |  |  |

| 101 | YFFA62      | CHIP-SELECT OF               | PTION 5 (CSOR5)              | <u> </u>           |  |  |  |  |  |  |  |  |  |

| 101 | YFFA64      | CHIP-SELECT B                | ASE 6 (CSBAR6)               | _  !               |  |  |  |  |  |  |  |  |  |

| 101 | YFFA66      | CHIP-SELECT O                | PTION 6 (CSOR6)              |                    |  |  |  |  |  |  |  |  |  |

| 101 | YFFA68      | CHIP-SELECT BASE 7 (CSBAR7)  |                              |                    |  |  |  |  |  |  |  |  |  |

| 101 | YFFA6A      | CHIP-SELECT OPTION 7 (CSOR7) |                              |                    |  |  |  |  |  |  |  |  |  |

| 101 | YFFA6C      | CHIP-SELECT BASE 8 (CSBAR8)  |                              |                    |  |  |  |  |  |  |  |  |  |

| 101 | YFFA6E      | CHIP-SELECT O                | CHIP-SELECT OPTION 8 (CSOR8) |                    |  |  |  |  |  |  |  |  |  |

| 101 | YFFA70      | CHIP-SELECT B                | ASE 9 (CSBAR9)               | _                  |  |  |  |  |  |  |  |  |  |

| 101 | YFFA72      | CHIP-SELECT O                | PTION 9 (CSOR9)              | _                  |  |  |  |  |  |  |  |  |  |

| 101 | YFFA72      | CHIP-SELECT O                | PTION 9 (CSOR9)              | _                  |  |  |  |  |  |  |  |  |  |

| 101 | YYFA74      | CHIP-SELECT BA               | ASE 10 (CSBAR10)             | _                  |  |  |  |  |  |  |  |  |  |

| 101 | YFFA76      | CHIP SELECT OP               | TION 10 (CSOR10)             | CHIP SELECT        |  |  |  |  |  |  |  |  |  |

|     | YFFA78      | UNUSED                       | UNUSED                       |                    |  |  |  |  |  |  |  |  |  |

|     | YFFA7A      | UNUSED                       | UNUSED                       |                    |  |  |  |  |  |  |  |  |  |

|     | YFFA7C      | UNUSED                       | UNUSED                       |                    |  |  |  |  |  |  |  |  |  |

|     | YFFA7E      | UNUSED                       | UNUSED                       |                    |  |  |  |  |  |  |  |  |  |

X = Depends on state of SUPV bit in SIM MCR

Y = m111, where m is the modmap bit in the SIM MCR (Y = \$7 or \$F)

#### SIM Registers

| MCR — Module Control Register \$YFFA |       |       |    |       |    |       |       |      |    |   |   |       |       | FA00  |       |

|--------------------------------------|-------|-------|----|-------|----|-------|-------|------|----|---|---|-------|-------|-------|-------|

| 15                                   | 14    | 13    | 12 | 11    | 10 | 9     | 8     | 7    | 6  | 5 | 4 | 3     | 2     | 1     | 0     |

| EXOFF                                | FRZSW | FRZBM | 0  | SLVEN | 0  | SHEN1 | SHENO | SUPV | MM | 0 | 0 | IARB3 | IARB2 | IARB1 | IARB0 |

| RESET:                               |       |       |    |       |    |       |       |      |    |   |   |       |       |       |       |

| 0                                    | 1     | 1     | 0  | DB11  | 0  | 0     | 0     | 1    | 1  | 0 | 0 | 1     | 1     | 1     | 1     |

#### EXOFF - External Clock Off

- 1 = The CLKOUT pin is placed in a high-impedance state.

- 0 = The CLKOUT pin is driven from an internal clock source.

#### FRZSW — Freeze Software Enable

- 1 = When FREEZE is asserted, the software watchdog and periodic interrupt timer counters are disabled, preventing interrupts from occurring when software is debugged.

- 0 = When FREEZE is asserted, the software watchdog and periodic interrupt timer counters continue to run.

#### FRZBM - Freeze Bus Monitor Enable

- 1 = When FREEZE is asserted, the bus monitor is disabled.

- 0 = When FREEZE is asserted, the bus monitor continues to operate as programmed.

#### SLVEN — Slave Mode Enabled

- 1 = Any external master winning control of the external bus also gains direct access to the internal peripherals.

- 0 = The internal peripherals are not available to an external master. This bit is a read-only status bit that reflects the state of DB11 during reset.

MC68332 BR756/D Rev. 1 MOTOROLA

#### SHEN1-0- Show Cycle Enable

These two control bits determine what the EBI does with the external bus during internal transfer operations.

| SHEN1 | SHEN0 | Action                                                                                      |

|-------|-------|---------------------------------------------------------------------------------------------|

| 0     | 0     | Show cycles disabled, external arbitration enabled                                          |

| 0     | 1     | Show cycles enabled, external arbitration disabled                                          |

| 1     | 0     | Show cycles enabled, external arbitration enabled                                           |

| 1     | 1     | Show cycles enabled, external arbitration enabled — internal activity halted by a bus grant |

#### SUPV — Supervisor/Unrestricted Data Space

- 1 = Registers with access controlled by the SUPV bit are restricted to supervisor access only when FC2 = 1.

- 0 = Registers with access controlled by the SUPV bit are unrestricted (FC2 is a don't care).

#### MM — Module Mapping

- 1 = Internal modules are addressed from \$FFF000-\$FFFFFF, which is in the absolute short addressing range.

- 0 = Internal modules are addressed from \$7FF000-\$7FFFFF.

#### IARB3-IARB0 - Interrupt Arbitration Bits

The system software must initialize the IARB field to a value from \$F (highest priority) to \$1 (lowest priority). The reset value of zero keeps the SIM from arbitrating during an IACK cycle and causes any SIM interrupts to be discarded as spurious interrupts.

| SIM  | SIMTR — System Integration Module Test Register \$YYFA02 |    |    |    |    |   |   |        |        |        |        |       |       |      | 'FA02 |

|------|----------------------------------------------------------|----|----|----|----|---|---|--------|--------|--------|--------|-------|-------|------|-------|

| 15   | 14                                                       | 13 | 12 | 11 | 10 | 9 | 8 | 7      | 6      | 5      | 4      | 3     | 2     | 1    | 0     |

| MASK |                                                          |    |    |    |    | 0 | 0 | SOSEL1 | SOSELO | SHIRQ1 | SHIRQ0 | FBIT1 | FBIT0 | BWC1 | BWC0  |

| RESE | ET:                                                      |    |    |    |    |   |   |        |        |        |        |       |       |      | -     |

MASK — Revision Number for this Part

SOSEL1-SOSEL0 --- Scan Out Select

SHIRQ1-SHIRQ0 — Show Interrupt Request

FBIT1-FBIT0-Force Bits

BWC1-BWC0 — Bandwidth Control Bits

**\$YFFA04** SYNCR — Clock Synthesizer Control Register 7 3 12 10 14 SLOCK RSTEN STSIM SLIMP **STEXT EDIV** W Х **Y5 Y4 Y3 Y1** Y0 RESET: U 0 0 0 0 U 1 1 0 0 0

U = Unaffected by reset

FSYSTEM = FCRYSTAL  $[4(Y + 1)2^{2W + X}]$

W --- Frequency Control Bit

X — Frequency Control Bit

Y5-Y0 — Frequency Control Bits

#### EDIV - E-Clock Divide Rate

- 1 = E clock = system clock divided by 16

- 0 = E clock = system clock divided by 8

#### SLIMP - Limp Mode

- 1 = A loss of crystal reference has been detected and the VCO is running at approximately half of maximum speed.

- 0 = External crystal frequency is VCO reference.

#### SLOCK — Synthesizer Lock

- 1 = VCO has locked on to the desired frequency (or system clock is driven externally).

- 0 = VCO is enabled, but has not yet locked.

#### RSTEN - Reset Enable

- 1 = Loss of crystal causes a system reset.

- 0 = Loss of crystal causes the VCO to operate at a nominal speed without external reference (limp mode), and the MCU continues to operate at that speed.

#### STSIM — Stop Mode System Integration Clock

- 1 = When the LPSTOP instruction is executed, the SIM clock is driven from the VCO.

- 0 = When the LPSTOP instruction is executed, the SIM clock is driven from the crystal oscillator and the VCO is turned off to conserve power.

#### STEXT — Stop Mode External Clock

- 1 = When the LPSTOP instruction is executed, the external clock pin (CLKOUT) is driven from the SIM clock, as determined by the STSIM bit.

- 0 = When the LPSTOP instruction is executed, the external clock is held low to conserve power.

#### Some System Frequencies from 32.768-kHz Reference

| Υ           | W = 0 X = 0 | W = 0 X = 1 | W = 1 X = 0 | W = 1 X = 1 |

|-------------|-------------|-------------|-------------|-------------|

| 0 = 000000  | 131         | 262         | 524         | 1049        |

| 1 = 000001  | 262         | 524         | 1049        | 2097        |

| 2 = 000010  | 393         | 786         | 1573        | 3146        |

| 3 = 000011  | 524         | 1049        | 2097        | 4194        |

| 4 = 000100  | 655         | 1311        | 2621        | 5243        |

| 5 = 000101  | 786         | 1573        | 3146        | 6291        |

| 6 = 000110  | 918         | 1835        | 3670        | 7340        |

| 7 = 000111  | 1049        | 2097        | 4194        | 8389        |

| 8 = 001000  | 1180        | 2359        | 4719        | 9437        |

| 9 = 001001  | 1311        | 2621        | 5243        | 10486       |

| 10 = 001010 | 1442        | 2884        | 5767        | 11534       |

| 11 = 001011 | 1573        | 3146        | 6291        | 12583       |

| 12 = 001100 | 1704        | 3408        | 6816        | 13631       |

| 13 = 001101 | 1835        | 3670        | 7340        | 14680       |

| 14 = 001110 | 1966        | 3932        | 7864        | 15729       |

| 15 = 001111 | 2097        | 4194        | 8389        | 16777       |

| 16 = 010000 | 2228        | 4456        | 8913        |             |

# RSR — Reset Status Register \$YFFA07 7 6 5 4 3 2 1 0 EXT POW SW HLT 0 LOC SYS TST

#### EXT — External Reset

1 = The last reset was caused by an external signal.

#### POW --- Power-Up Reset

1 = The last reset was caused by the power-up reset circuit.

#### SW — Software Watchdog Reset

1 = The last reset was caused by the software watchdog circuit.

#### **HLT** — Halt Monitor Reset

1 = The last reset was caused by the system protection submodule halt monitor.

#### LOC - Loss of Clock Reset

1 = The last reset was caused by a loss of frequency reference to the clock submodule.

#### SYS — System Reset

1 = The last reset was caused by the CPU executing a reset instruction.

# TST — Test Submodule Reset

1 = The last reset was caused by the test submodule.

| SIMTRE — System Integration Module Test Register (E Clock) |    |    |    |    |    |   |   |   |   |   |   | Y | FFA08 |   |   |

|------------------------------------------------------------|----|----|----|----|----|---|---|---|---|---|---|---|-------|---|---|

| 15                                                         | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2     | 1 | 0 |

|                                                            |    |    |    |    |    |   |   |   |   |   |   |   |       |   |   |

RESET:

This write-only register is reserved for factory testing. A write to this register in test mode forces the E-clock phase to synchronize with the sytem clock.

PORTE - Port E Data Register

| \$YFFA1 | 1, YFFA13 |

|---------|-----------|

| 4       | Λ         |

| 7      | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|

| PE7    | PE6 | PE5 | PE4 | PE3 | PE2 | PE1 | PE0 |

| RESET: |     |     |     |     |     |     |     |

| U      | U   | U   | U   | U   | U   | U   | U   |

PE7-0 - Port E Data

DDRE — Port E Data Direction Register

| •   | YF | _ | A 4 |   |

|-----|----|---|-----|---|

| 39. | T  |   | н 1 | - |

|     |    |   |     |   |

| DDUE — | OIL L Data |      | 9.0.0. |      |      |      | •    |

|--------|------------|------|--------|------|------|------|------|

| 7      | 6          | 5    | 4      | 3    | 2    | 11   | 0    |

| DDE7   | DDE6       | DDE5 | DDE4   | DDE3 | DDE2 | DDE1 | DDE0 |

| RESET: |            |      |        |      |      |      |      |

| 0      | 0          | 0    | 0      | 0    | 0    | 0    | 0    |

DDE7-0 - Data Direction E (Input/Output)

1 = Input

0 = Output

PEPAR — Port E Pin Assignment Register

| \$ | YF | F | 41 | 7 |

|----|----|---|----|---|

|----|----|---|----|---|

| 7               | 6               | 5             | 4             | 3              | 2               | 1               | 0               |

|-----------------|-----------------|---------------|---------------|----------------|-----------------|-----------------|-----------------|

| PEPA7<br>(SIZ1) | PEPA6<br>(SIZ0) | PEPA5<br>(AS) | PEPA4<br>(DS) | PEPA3<br>(RMC) | PEPA2<br>(AVEC) | PEPA1<br>DSACK1 | PEPA0<br>DSACK0 |

| RESET:<br>DB8   | DB8             | DB8           | DB8           | DB8            | DB8             | DB8             | DB8             |

PEPA7-0 — Port E Pin Assignment (I/O Function)

SIZ1-DSACK0 — Control Bus Function

A one on DB8 at reset sets the pins to the bus control function; otherwise, they are general-purpose I/O.

#### PORTF — Port F Data Register

#### **\$YFFA19, YFFA1B**

| 7      | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|

| PF7    | PF6 | PF5 | PF4 | PF3 | PF2 | PF1 | PF0 |

| RESET: |     |     |     |     |     |     |     |

| U      | U   | U   | U   | U   | U   | U   | U   |

PF7-0 — Port F Data

DDRF - Port F Data Direction Register

\$YFFA1D

| 7      | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|--------|------|------|------|------|------|------|------|

| DDF7   | DDF6 | DDF5 | DDF4 | DDF3 | DDF2 | DDF1 | DDF0 |

| RESET: |      |      |      |      |      |      |      |

| 0      | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

DDF7-0 — Data Direction F (Input/Output)

1 = Input

0 = Output

PFPAR — Port F Pin Assignment Register

SYFFA1F

|        |        | g      |        |        |        |        | <b>*</b> · · · · · · · · · · · · · · · · · · · |

|--------|--------|--------|--------|--------|--------|--------|------------------------------------------------|

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0                                              |

| PFPA7  | PFPA6  | PFPA5  | PFPA4  | PFPA3  | PFPA2  | PFPA1  | PFPA0                                          |

| (ĪRQ7) | (ĪRQ6) | (ĪRQ5) | (ĪRQ4) | (IRQ3) | (ĪRQ2) | (ĪRQ1) | (MODCK)                                        |

| RESET: |        |        |        |        |        |        |                                                |

| DB9                                            |

PFPA7-0 — Port E Pin Assignment (I/O Function)

IRQ7-1 — Control Bus Function

MODCLK

A one on DB9 at reset sets pins to the bus control function; otherwise, they are general-purpose I/O.

#### **SYPCR** — System Protection Control Register

\$YFFA21

|        | -     |      |      |     |     |      |      |

|--------|-------|------|------|-----|-----|------|------|

| 7      | 6     | 5    | 4    | 3   | 2   | 1    | 0    |

| SWE    | SWP   | SWTI | swto | HME | вме | BMT1 | вмто |

| RESET: |       |      |      |     |     |      |      |

| 1      | MODCK | 0    | 0    | 0   | 0   | 0    | 0    |

SWE — Software Watchdog Enable

1 = Software watchdog enabled

0 = Software watchdog disabled

SWP — Software Watchdog Prescale

1 = Software watchdog clock prescaled by 512

0 = Software watchdog clock not prescaled

At reset SWP takes on the inverted value of the MODCLK pin.

MOTOROLA 26

#### SWT1-SWT0 — Software Watchdog Timing

These bits control the divide ratio used to establish the timeout period for the software watchdog timer. The software timeout period is given by the following equation.

Timeout Period = 1/(EXTAL Frequency/Divide Count)

or

= Divide Count/EXTAL Frequency

#### **Software Timeout Periods for Watchdog Timer**

| Bits 6-4 | Software Timeout Period                | 32.768-kHz<br>Crystal Period | 16.718-MHz<br>External Clock Period |

|----------|----------------------------------------|------------------------------|-------------------------------------|

| 000      | 2 <sup>9</sup> /EXTAL Input Frequency  | 15.6 Milliseconds            | 30.6 Microseconds                   |

| 001      | 2 <sup>11</sup> /EXTAL Input Frequency | 62.5 Milliseconds            | 122.5 Microseconds                  |

| 010      | 2 <sup>13</sup> /EXTAL Input Frequency | 250 Milliseconds             | 490 Microseconds                    |

| 011      | 2 <sup>15</sup> /EXTAL Input Frequency | 1 Second                     | 1.96 Microseconds                   |

| 100      | 2 <sup>18</sup> /EXTAL Input Frequency | 8 Seconds                    | 15.6 Milliseconds                   |

| 101      | 2 <sup>20</sup> /EXTAL Input Frequency | 32 Seconds                   | 62.7 Milliseconds                   |

| 110      | 2 <sup>22</sup> /EXTAL Input Frequency | 128 Seconds                  | 250 Milliseconds                    |

| 111      | 2 <sup>24</sup> /EXTAL Input Frequency | 512 Seconds                  | 1 Second                            |

#### HME - Halt Monitor Enable

- 1 = Enable halt monitor function

- 0 = Disable halt monitor function

#### BME -- Bus Monitor External Enable

- 1 = Enable bus monitor function for an internal to external bus cycle.

- 0 = Disable bus monitor function for an internal to external bus cycle.

#### **BMT** — Bus Monitor Timing

| Bits 1-0 | Bus Monitor Timeout Period |

|----------|----------------------------|

| 00       | 64 System Clocks (CLK)     |

| 01       | 32 System Clocks (CLK)     |

| 10       | 16 System Clocks (CLK)     |

| 11       | 8 System Clocks (CLK)      |

| <b>PICR</b> | — Pe | riodic | Interru | ıpt Co | ntrol Reg | gister |        |      |      |      |      |      |      | \$YF | FFA22 |

|-------------|------|--------|---------|--------|-----------|--------|--------|------|------|------|------|------|------|------|-------|

| 15          | 14   | 13     | 12      | 11     | 10        | 9      | 8      | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0     |

| 0           | 0    | 0      | 0       | 0      | PIRQL2    | PIRQL1 | PIRQL0 | PIV7 | PIV6 | PIV5 | PIV4 | PIV3 | PIV2 | PIV1 | PIVO  |

| RESE        | T:   |        |         |        |           |        |        |      |      |      |      |      |      |      |       |

| 0           | 0    | 0      | 0       | 0      | 0         | 0      | 0      | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1     |

#### PIRQL2-0 -- Periodic Interrupt Request Level

| Bits 10-8 | Interrupt Request Level     |

|-----------|-----------------------------|

| 000       | Periodic Interrupt Disabled |

| 001       | Interrupt Request Level 1   |

| 010       | Interrupt Request Level 2   |

| 011       | Interrupt Request Level 3   |

| 100       | Interrupt Request Level 4   |

| 101       | Interrupt Request Level 5   |

| 110       | Interrupt Request Level 6   |

| 111       | Interrupt Request Level 7   |

#### PIV7-PIV0 — Periodic Interrupt Vector

These bits contain the value of the vector generated during an IACK cycle in response to an interrupt from the periodic timer.

|   | PITR | — Pe | riodic | Interru | pt Tim | ing Re | egiste | r     |       |       |       |       |       |       | \$YF  | FA24  |

|---|------|------|--------|---------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|   | 15   | 14   | 13     | 12      | 11     | 10     | 9      | 8     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| ſ | 0    | 0    | 0      | 0       | 0      | 0      | 0      | PTP   | PITR7 | PITR6 | PITR5 | PITR4 | PITR3 | PITR2 | PITR1 | PITR0 |

| • | RESE | T:   |        |         |        |        |        |       |       |       |       |       |       |       |       |       |

|   | 0    | 0    | 0      | 0       | 0      | 0      | 0      | MODCK | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

#### PTP — Periodic Timer Prescaler

- 1 = Periodic timer clock prescaled by a value of 512

- 0 = Periodic timer clock not prescaled

| MODCK | PTP |

|-------|-----|

| 0     | 1   |

| 1     | 0   |

#### PITR7-PITR0 --- PITM Field (Periodic Interrupt Timing Modulus)

The periodic interrupt timing register (PITR) contains the count value for the periodic timer. A zero value turns off the periodic timer.

The period of the periodic timer can be calculated using the following equation:

PIT Period = PITM/(EXTAL/Prescaler)/4

where

PIT period = Periodic interrupt timer period

PITM = Periodic interrupt timer register modulus (PITR7-PITR0)

EXTAL= Crystal frequency

Prescaler = 512 or 1 depending on the state of the PTP bit in the PITR

MOTOROLA 28

#### **SYFFA27 SWSR** — Software Service Register 4 3 2 1 n 7 6 5 SWSR0 SWSR5 SWSR4 SWSR3 SWSR2 SWSR1 SWSR6 SWSR7 RESET: 0 0 0 0 0 0 0 0

The software watchdog service sequence consists of the following two steps:

- 1. Write \$55 to the software service register (SWSR)

- 2. Write \$AA to the SWSR

Both writes must occur in the order shown before the watchdog timeout, but any number of instructions can be executed between the two writes.

#### TSTMSRA — Master Shift Register A

\$YFFA30

Master shift register A contains the stimulus to be transferred from the test submodule to the module under test.

#### TSTMSRB - Master Shift Register B

**SYFFA32**

Master shift register B collects the response data shifted from the module under test to the test submodule.

# TSTSCA — Shift Count Register A and Shift Counter A

**SYFFA34**

Shift count register A is an 8-bit shift register that can be accessed by the bus master. Shift counter A is an 8-bit counter that is loaded by shift count register A and is not accessible to the bus master.

# TSTSCB — Shift Count Register B and Shift Counter B

\$YFFA35

Shift count register B is an 8-bit shift register that can be accessed by the bus master. Shift counter B is an 8-bit counter that is loaded by shift count register B and is not accessible to the bus master.

#### TSTRC — Test Module Repetition Counter

**\$YFFA36**

The reps counter determines the number of psuedorandom vectors generated in the automatic mode of operation.

#### **CREG** — Test Submodule Control Register

\$YFFA38

| 15    | 14    | 13   | 12     | 11    | 10   | 9     | 8 | 7 | 6 | 5 | 4    | 3     | 2     | 1    | 0   |

|-------|-------|------|--------|-------|------|-------|---|---|---|---|------|-------|-------|------|-----|

| BUSY  | TMARM | СОМР | IMBTST | CPUTR | QBIT | MUXEL | _ |   |   |   | ACUT | SCONT | SSHOP | SATO | ETM |

| RESET | :     |      |        |       |      |       |   |   |   |   |      |       |       |      |     |

| 4     | TOTME | - 11 | 0      | n     | 0    | 0     | 0 | 0 | 0 | 0 | 0    | 0     | 0     | 0    | 0   |

#### ETM — Enter Test Mode

- 1 = Enter test mode.

- 0 = Stay in normal mode.

#### SATO — Start Automatic Test Operation

- 1 = Start an automatic test operation.

- 0 = Stay in normal mode.

#### SSHOP — Start Shifting Operation

- 1 = Start a shifting operation.

- 0 = Stay in normal mode.

#### SCONT — Start Continuous Operation

- 1 = Start continuous operation.

- 0 = Stop continuous operation.

#### **ACUT** — Activate Circuit Under Test

- 1 = Assert the ACUTL line.

- 0 = Stay in normal mode.

#### MUXSEL — Multiplexer Select Bit

- 1 = Shift in source for master shift register B (MSRB) is the external interrupt pin.

- 0 = Shift in source for MSRB is the internal test line.

#### QBIT - Quotient Bit

- 1 = The least significant bit of master shift register B is available at the quotient/freeze (FREEZE/QUOT) pin.

- 0 = The internal freeze status is available at the FREEZE/QUOT pin.

#### CPUTR — CPU Test Register

- 1 = Scan lines are connected to the CPU test register.

- 0 = Scan lines are disconnected from the CPU test register.

#### IMBTST -- Intermodule Bus Test

- 1 = Internal interconnect lines are configured as test lines.

- 0 = Internal interconnect lines have normal function.

#### COMP — Compare Status Bit

- 1 = Master shift register B contains the correct answer for the user basic self-test.

- 0 = Master shift register B does not contain the correct answer for the basic user self-test.

#### TMARM — Test Mode Armed Status Bit

- 1 = TSTME pin is asserted; test mode can be entered by setting the ETM control bit.

- 0 = TSTME pin is negated; test mode cannot be entered. This status bit can be read at any time, but cannot be written.

#### BUSY — Test Submodule Busy Status Bit

- 1 = Test submodule is busy.

- 0 = Test submodule is not busy.

**DREG** — Distributed Register

**\$YFFA3A**

| 15  | 14  | 13 | 12 |   |       | -     | -     | 7      | •      | 5      | 4     | 3      | 2      | 1      | 0     |

|-----|-----|----|----|---|-------|-------|-------|--------|--------|--------|-------|--------|--------|--------|-------|

|     | _   | _  | _  |   | WAIT3 | WAIT2 | WAIT1 | MSRA18 | MSRA17 | MSRA16 | MSRAC | MSRB18 | MSRB17 | MSRB16 | MSRBC |

| RES | ET: |    |    |   |       |       |       |        |        |        |       |        |        |        |       |

| ^   | ^   | ^  | 0  | ^ | Λ     | 0     | Λ     | n      | 0      | ٥      | 0     | 0      | 0      | 0      | 0     |

WAIT3-WAIT1 — Wait Counter Preset 3-1

These bits program the delay time between automatic test sequences.

MSRA18-MSRA16 - Master Shift Register A Bits 18-16

MSRAC — Master Shift Register A Configuration

- 1 = Master shift register A is configured as a 19-bit serial pattern generator.

- 0 = Master shift register A is configured as a 16-bit shift register.

MSRB18-MSRB16 - Master Shift Register B Bits 18-16

MSRBC — Master Shift Register B Configuration

- 1 = Master shift register B is configured as a 19-bit serial signature analyzer.

- 0 = Master shift register B is configured as a 16-bit shift register.

**CSPDR** — Chip-Select Pin Data Register

**SYFFA41**

| 7      | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|

| 0      | DO6 | DO5 | DO4 | DO3 | DO2 | DO1 | DO0 |

| RESET: |     |     |     |     |     |     |     |

| 0      | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

D6-0 - Pin Data

CSPAR0 — Chip-Select Pin Assignment Register 0

**\$YFFA44**

| 15    | 14 | 13  | 12    | 11  | 10    | 9   | 8     | / 6        | •          | 5   | 4    | 3   | 2    | 1    |    |

|-------|----|-----|-------|-----|-------|-----|-------|------------|------------|-----|------|-----|------|------|----|

| 0     | 0  | CS5 | (FC2) | CS4 | (FC1) | CS3 | (FC0) | CS2 (BGACK | <b>(</b> ) | CS1 | (BG) | CS0 | (BR) | CSBO | от |

| RESET | :  |     |       |     |       |     |       | -          |            |     |      |     |      |      |    |

0 0 DB2 1 DB2 1 DB2 1 DB1 1 DB1 1 DB1 1 1 DB0

Bits 15-14 - Not Used

These bits always read zero; write has no effect.

CSPAR1 — Chip-Select Pin Assignment Register 1

\$YFFA46

| 15   | 14 | 13 | 12 | 11 | 10 | 9    | 8     | 7     | 6    | 5      | 4    | 3     | 2    | 1     | 0    |

|------|----|----|----|----|----|------|-------|-------|------|--------|------|-------|------|-------|------|

| 0    | 0  | 0  | 0  | 0  | 0  | CS10 | (A23) | CS9 ( | A22) | CS8 (/ | 421) | CS7 ( | A20) | CS6 ( | A19) |

| RESE | T: |    |    |    |    |      |       |       |      |        |      |       |      |       |      |

| ^    | ^  | ^  | 0  | ٥  | ^  | DR7  | 4     | DB6   | 1    | DBS    | 1    | DR4   | 1    | DB3   | 1    |

These bits always read zero; write has no effect.

#### **Hierarchical Selection Structure of CSPAR1**

|     | Data Bu | ıs Pins : | at Rese | t   | Default/Alternate Function |         |         |         |         |  |  |  |  |  |

|-----|---------|-----------|---------|-----|----------------------------|---------|---------|---------|---------|--|--|--|--|--|

| DB7 | DB6     | DB5       | DB4     | DB3 | CS10/A23                   | CS9/A22 | CS8/A21 | CS7/A20 | CS6/A19 |  |  |  |  |  |

| 1   | 1       | 1         | 1       | 1   | CS10                       | CS9     | CS8     | CS7     | CS6     |  |  |  |  |  |

| 1   | 1       | 1         | 1       | 0   | CS10                       | CS9     | CS8     | CS7     | A19     |  |  |  |  |  |

| 1   | 1       | 1         | 0       | Х   | CS10                       | CS9     | CS8     | A20     | A19     |  |  |  |  |  |

| 1   | 1       | 0         | Х       | Х   | CS10                       | CS9     | A21     | A20     | A19     |  |  |  |  |  |

| 1   | 0       | Х         | Х       | Х   | CS10                       | A22     | A21     | A20     | A19     |  |  |  |  |  |

| 0   | Х       | Х         | X       | Х   | A23                        | A22     | A21     | A20     | A19     |  |  |  |  |  |

# Pin Assignment Register Bit Encoding

| Bits | Description                       |

|------|-----------------------------------|

| 00   | Discrete Output (E Clock on A23)* |

| 01   | Alternate Function                |

| 10   | Chip Select (8-Bit Port)          |

| 11   | Chip Select (16-Bit Port)         |

<sup>\*</sup>Except for BR, BG, and BGACK

| CSB  | ARBT  | — Chi | p-Sele | ct Bas | e Addı   | ress R | egiste | Boot   |       |     |     |     |     | \$Y     | FFA48 |

|------|-------|-------|--------|--------|----------|--------|--------|--------|-------|-----|-----|-----|-----|---------|-------|

| 15   | 14    | 13    | 12     | 11     | 10       | 9      | 8      | 7      | 6     | 5   | 4   | 3   | 2   | 1       | 0     |

| A23  | A22   | A21   | A20    | A19    | A18      | A17    | A16    | A15    | A14   | A13 | A12 | A11 |     | BLKSZ   |       |

| RESE | T:    | _     | _      | -      |          | _      | -      | •      | _     |     |     | ,   |     |         |       |

| 0    | 0     | 0     | 0      | 0      | 0        | 0      | 0      | 0      | 0     | 0   | 0   | 0   | 1   | 1       | 1     |

|      |       |       |        |        |          |        |        |        |       |     |     |     |     |         |       |

|      |       |       |        |        |          |        |        |        |       |     |     |     |     |         |       |

| CSBA | ARO-C | SBAR  | 10 —   | Chip-S | Select E | Base A | ddres  | s Regi | sters |     |     |     | \$Y | FFA4C-Y | FFA74 |

| 15   | 14    | 13    | 12     | 11     | 10       | 9      | 8      | 7      | 6     | 5   | 4   | 3   | 2   | 1       | 0     |

| A23  | A22   | A21   | A20    | A19    | A18      | A17    | A16    | A15    | A14   | A13 | A12 | A11 |     | BLKSZ   |       |

| RESE | T:    | •     |        |        |          |        |        |        |       |     | •   |     |     |         |       |

| ^    | ^     | ^     | ^      | ^      | ^        | ^      | ^      | •      | ^     | ^   | ^   | •   | •   | ^       | ^     |

| Block Size Field | Block Size | Address Lines Compared |  |  |

|------------------|------------|------------------------|--|--|

| 000              | 2K         | A23-A11                |  |  |

| 001              | 8K         | A23-A13                |  |  |

| 010              | 16K        | A23-A14                |  |  |

| 011              | 64K        | A23-A16                |  |  |

| 100              | 128K       | A23-A17                |  |  |

| 101              | 256K       | A23-A18                |  |  |

| 110              | 512K       | A23-A19                |  |  |

| 111              | 1M         | A23-A20                |  |  |

Bits 15-3 - Base Address Field

In supervisor/user space, this field sets the starting address of a particular address space.

| CSORE  | ST — ( | Chip-S | elect C | ption | Registe | r |    |     |   |    |     |   |     | \$1 | /FFA4A |

|--------|--------|--------|---------|-------|---------|---|----|-----|---|----|-----|---|-----|-----|--------|

| 15     | 14     | 13     | 12      | 11    | 10      | 9 | 8  | 7   | 6 | 5  | 4   | 3 | 2   | 1   | 0      |

| MODE   | BY     | TE     | R       | W     | STRB    |   | DS | ACK |   | SP | ACE |   | IPL |     | AVEC   |

| RESET: |        |        |         | -     |         |   |    |     |   |    |     |   |     |     |        |

| 0      | 1      | 1      | 1       | 1     | 0       | 1 | 1  | 0   | 1 | 1  | 1   | 0 | 0   | 0   | 0      |

# **Option Register Functions Summary**

| Mode      | Byte       | R/W        | STRB   | DSACK           | Space        | IPL           | AVEC    |

|-----------|------------|------------|--------|-----------------|--------------|---------------|---------|

| 0 = ASYNC | 00 = Off   | 00 = Rsvd  | 0 = AS | 0000 = 0 WAIT   | 00 = CPU SP  | 000 = All     | 0 = Off |

| 1 = SYNC  | 01 = Lower | 01 = Read  | 1 = DS | 0001 = 1 WAIT   | 01 = User SP | 001 = Level 1 | 1 = On  |

|           | 10 = Upper | 10 = Write |        | 0010 = 2 WAIT   | 10 = Supv SP | 010 = Level 2 |         |

|           | 11 = Both  | 11 = Both  |        | 0011 = 3 WAIT   | 11 = S/U SP  | 011 = Level 3 |         |

|           |            |            |        | 0100 = 4 WAIT   |              | 100 = Level 4 |         |

|           |            |            |        | 0101 = 5 WAIT   |              | 101 = Level 5 |         |

|           |            |            |        | 0110 = 6 WAIT   |              | 110 = Level 6 |         |

|           |            |            |        | 0111 = 7 WAIT   |              | 111 = Level 7 |         |

|           |            |            |        | 1000 = 8 WAIT   |              |               |         |

|           |            |            |        | 1001 = 9 WAIT   |              |               |         |

|           |            |            |        | 1010 = 10 WAIT  |              |               |         |

|           |            |            |        | 1011 = 11 WAIT  |              |               |         |

|           |            |            |        | 1100 = 12 WAIT  |              |               |         |

|           |            |            |        | 1101 = 13 WAIT  |              |               |         |

|           |            |            |        | 1110 = F term   |              |               |         |

|           |            |            |        | 1111 = External |              |               |         |

#### CSOR0-CSOR10 — Chip-Select Option Registers

**\$YFFA4E-YFFA76**

|   | 15     | 14 | 13 | 12 | 11 | 10   | 9 | 8   | 7   | 6 | 5   | 4   | 3 | 2   | 1 | 0    |

|---|--------|----|----|----|----|------|---|-----|-----|---|-----|-----|---|-----|---|------|

|   | MODE   | BY | TE |    | w  | STRB |   | DSA | ACK |   | SPA | ACE |   | IPL |   | AVEC |

| , | RESET: |    |    |    |    |      |   |     |     |   |     |     |   |     |   |      |

|   | _      | _  | _  | ^  | _  | •    | ^ | _   | _   | _ | ^   | ^   | ^ | ^   | ^ | •    |

MODE — Asynchronous/Synchronous Mode

1 = Synchronous mode selected

0 = Asynchronous mode selected

#### BYTE — Upper/Lower Byte Option

This field is used when the chip-select 16-bit port option in the pin assignment register is selected.

| Bits | Description |

|------|-------------|

| 00   | Disable     |

| 01   | Lower Byte  |

| 10   | Upper Byte  |

| 11   | Both Bytes  |

#### R/W — Read/Write

This option causes the chip select to be asserted only for a read, only for a write, or for both read and write.

| Bits | Description |

|------|-------------|

| 00   | Reserved    |

| 01   | Read Only   |

| 10   | Write Only  |

| 11   | Read/Write  |

#### STRB — Address Strobe/Data Strobe

1 = Data strobe

0 = Address strobe

This option controls the timing for assertion of a chip select in asynchronous mode.

#### DSACK — Data Strobe Acknowledge

In asynchronous mode, this option field specifies the source of the DSACK (externally or internally generated).

| Bits | Description      |

|------|------------------|

| 0000 | No Wait States   |

| 0001 | 1 Wait State     |

| 0010 | 2 Wait States    |

| 0011 | 3 Wait States    |

| 0100 | 4 Wait States    |

| 0101 | 5 Wait States    |

| 0110 | 6 Wait States    |

| 0111 | 7 Wait States    |

| 1000 | 8 Wait States    |

| 1001 | 9 Wait States    |

| 1010 | 10 Wait States   |

| 1011 | 11 Wait States   |

| 1100 | 12 Wait States   |

| 1101 | 13 Wait States   |

| 1110 | Fast Termination |

| 1111 | External DSACK   |

#### SPACE — Address Space

This option field checks the address spaces indicated by the function codes generated by the CPU.

| Bits | Description           |

|------|-----------------------|

| 00   | CPU Space             |

| 01   | User Space            |

| 10   | Supervisor Space      |

| 11   | Supervisor/User Space |

#### IPL — Interrupt Priority Level

In an IACK cycle, the chip-select logic checks the acknowledged interrupt level on address lines A3—A1. If that level matches the level set in the IPL field, then the chip select can be asserted if the match conditions in the other fields are met.

| Bits | Description |

|------|-------------|

| 000  | Any Level   |

| 001  | IPL1        |

| 010  | IPL2        |

| 011  | IPL3        |

| 100  | IPL4        |

| 101  | IPL5        |

| 110  | IPL6        |

| 111  | IPL7        |

#### **AVEC** — Autovector Enable

- 1 = Autovector enabled

- 0 = External interrupt vector enabled

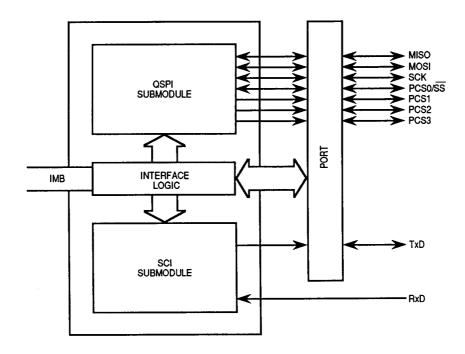

#### Queued Serial Module (QSM)

The queued serial module (QSM) provides the MCU with two serial communication interfaces divided into two submodules: the queued serial peripheral interface (QSPI) and the serial communications interface (SCI). These submodules operate independently.

**QSM Block Diagram**

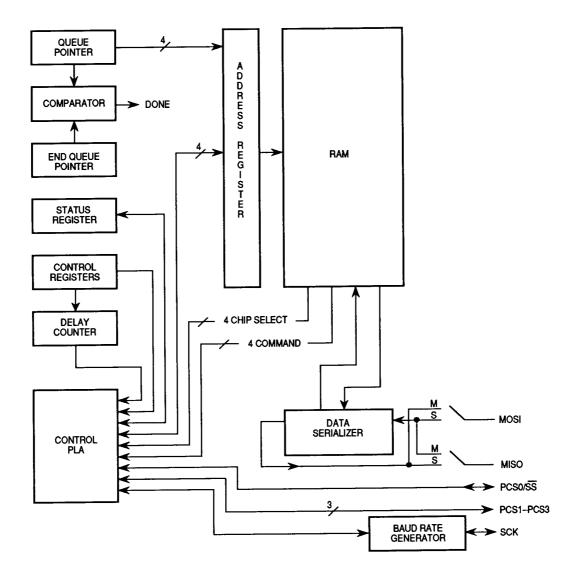

#### **QSPI Submodule**

The QSPI submodule communicates with external peripherals and other MCUs through a synchronous serial bus. The QSPI is fully compatible with the serial peripheral interface (SPI) found on other Motorola devices, such as the M68HC11 and M68HC05 Families. It has all of the capabilities of the SPI system, as well as several new features.

#### **Features**

Standard SPI features:

- Full Duplex, Three-Wire Synchronous Transfers

- Half-Duplex, Two-Wire Synchronous Transfers

- Master or Slave Operation

- Programmable Master Bit Rates

- Programmable Clock Polarity and Phase

- End-of-Transmission Interrupt Flag

- Multimaster Mode Fault Flag

- Easy Interface to Simple Expansion Parts (A/D converters, EEPROMS, display drivers, etc.)

#### **QSPI-Enhanced Features:**

- Programmable Queue Up to 16 Preprogrammed Transfers

- Programmable Peripheral Chip Selects Four Pins Select up to 16 SPI Chips

- Wraparound Transfer Mode For Autoscanning of Serial A/D (or other) Peripherals

- Programmable Transfer Length From 8–16 Bits Inclusive

- Programmable Transfer Delay From 1 μs to 0.5 ms (at 16.78 MHz)

- Programmable Queue Pointer

- Continuous Transfer Mode Up to 256 Bits

**QSPI Submodule Diagram**

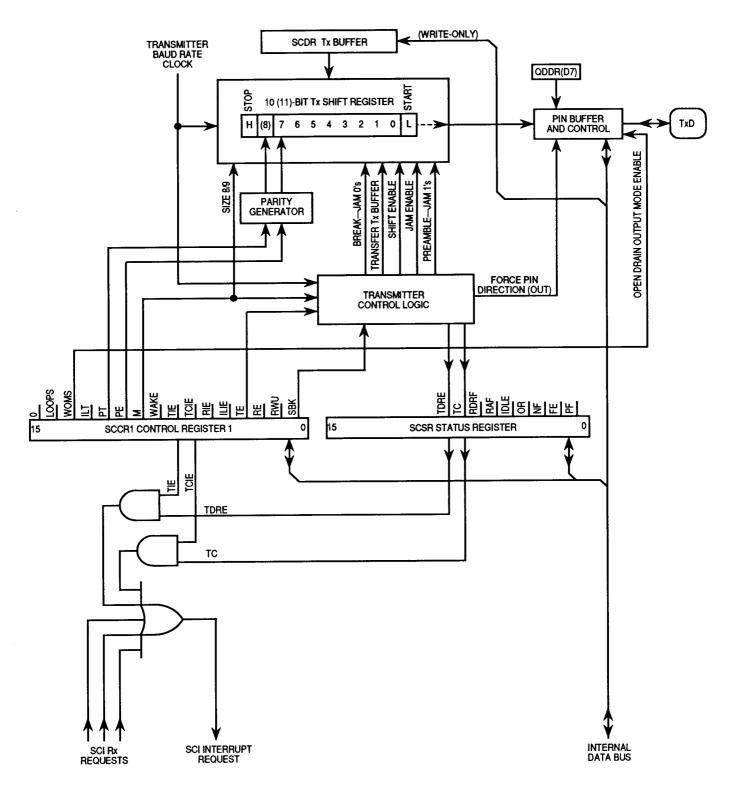

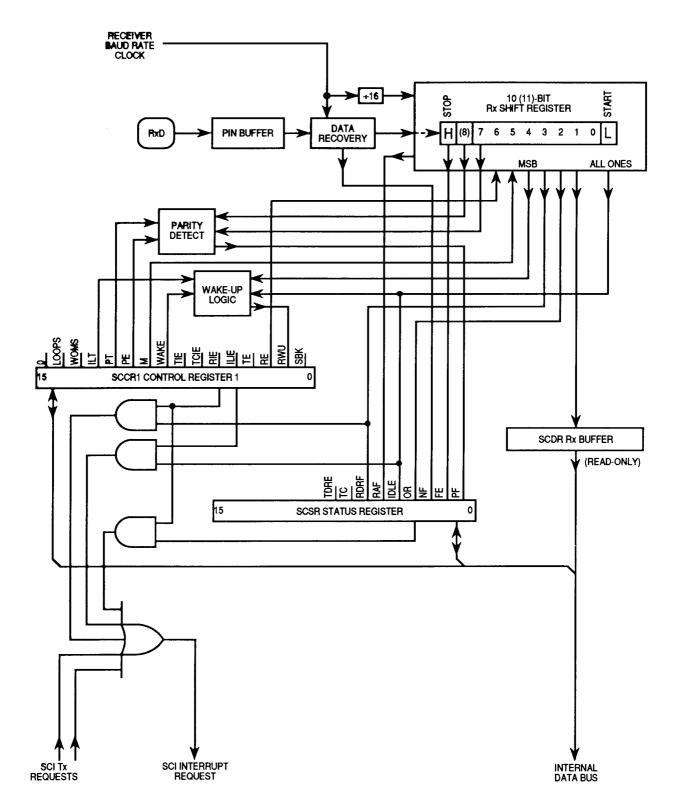

#### **SCI Submodule**

The SCI submodule communicates with external devices and other MCUs through an asynchronous serial bus. The SCI is fully compatible with the SCI systems found on other Motorola MCUs such as the M68HC11 and the M68HC05 Families. It has all of the capabilities of previous SCI systems as well as several significant new features.

#### **Features**

Standard SCI Two-Wire System Features:

- Standard Nonreturn-to-Zero (NRZ) Mark/Space Format

- Advanced Error Detection Mechanism (detects noise duration up to 1/16 of a bit time)

- Full-Duplex Operation

- Software Selectable Word Length (8- or 9-bit words)

- Separate Transmitter and Receiver Enable Bits

- May be Interrupt Driven

- Four Separate Interrupt Enable Bits

#### Standard SCI Receiver Features:

- Receiver Wakeup Function (idle or address mark bit)

- Idle-Line Detect

- Framing Error Detect

- Noise Detect

- Overrun Detect

- Receive Data Register Full Flag

#### Standard SCI Transmitter Features:

- Transmit Data Register Empty Flag

- Transmit Complete Flag

- Send Break

#### QSM-Enhanced SCI Two-Wire System Features:

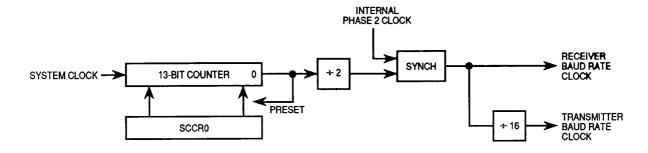

- 13-Bit Programmable Baud Rate Modulus Counter

- Even/Odd Parity Generation and Detection

#### QSM-Enhanced SCI Receiver Features:

- Two Idle-Line Detect Modes

- Receiver Active Flag

- •13-Bit Programmable Baud Rate Modulus Counter

**SCI Transmitter Block Diagram**

**SCI Receiver Block Diagram**

#### **SCI Baud Generator Block Diagram**

Y = m111 where m is the modmap bit in the SIM MCR (Y = \$7 or \$F).

#### **QSM Registers**

# **QMCR** — QSM Configuration Register

\$YFFC00

| 15    | 14   | 13   | 12 | 11 | 10 | 9 | 8 | 7    | 6 | 5 | 4 | 3 | 2   | 1  | 0 |

|-------|------|------|----|----|----|---|---|------|---|---|---|---|-----|----|---|

| STOP  | FRZ1 | FRZ0 | 0  | 0  | 0  | 0 | 0 | SUPV | 0 | 0 | 0 |   | IAI | ЗВ |   |

| RESET | •    |      |    |    |    |   |   |      |   |   |   |   |     |    |   |

| 0     | 0    | 0    | 0  | 0  | 0  | 0 | 0 | 1    | 0 | 0 | 0 | 0 | 0   | 0  | 0 |

STOP - Stop Enable

1 = QSM clock operation stopped

0 = Normal QSM clock operation

FRZ1 — Freeze 1

1 = Halt the QSM (on a transfer boundary)

0 = ignore the FREEZE signal on the IMB

FRZ0 - Freeze 0

Reserved for future enhancement.

Bits 12-8 - Not Implemented

SUPV — Supervisor/Unrestricted

1 = Supervisor access

0 = User access

Bits 6-4 - Not Implemented

IARB — Interrupt Arbitration Identification Number