# Hub - I2Cbus & multi-master

Daniel Edmunds, Wade Fisher, Yuri Ermoline, Philippe Laurens, Gabriel Louis Moreau (Michigan State University)

> TDAQ Phase-I upgrade DCS contacts meeting CERN, 11 October 2018

- Started with legacy I2C state machine (RAL) for the CMM module

- CoolRunner XPLA3 XCR3384XL 384 macrocell CPLD

- Point-to-point access to TTCrx chip

- Single master, no arbitration, simple (2 registers) interface

- Adapted for the CMX module

- Spartan-3AN FPGA XC3S200AN-4FTG256C

- Individual masters, no arbitration, point-to-point (TTCrx, MiniPOD, SFP)

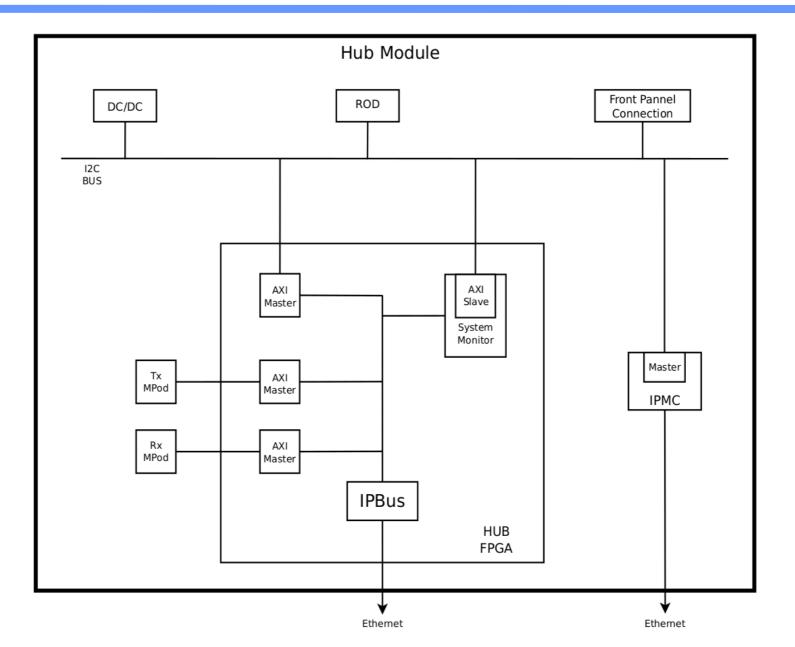

- For the HUB, HW design started with the same idea

- Initially Virtex7 FPGA, then move to Ultra Scale XCVU125

- Single master, no arbitration, point-to-point:

MiniPODs (Rx & Tx), DC/DC convertors (3 master I2C interfaces on FPGA)

- Dedicated slave I2C interface to FPGA System Monitor

- For the HUB FPGA FW development use XILINX I2C IP

- Full Master/Slave I2C, AXI4 interface, 22 control/status registers

- IPbus to I2C via AXI4 bridge (Ed Flaherty, Cambridge)

- Then IPMC came into the game...

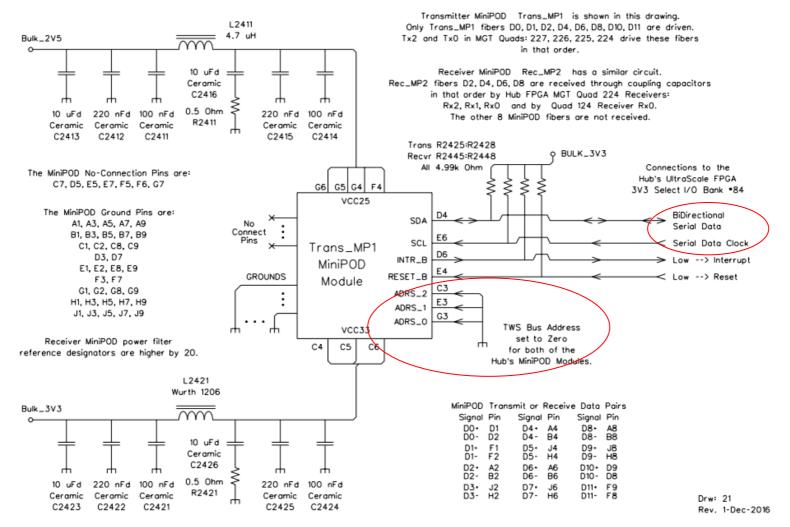

#### Transmitter and Receiver MiniPOD Modules

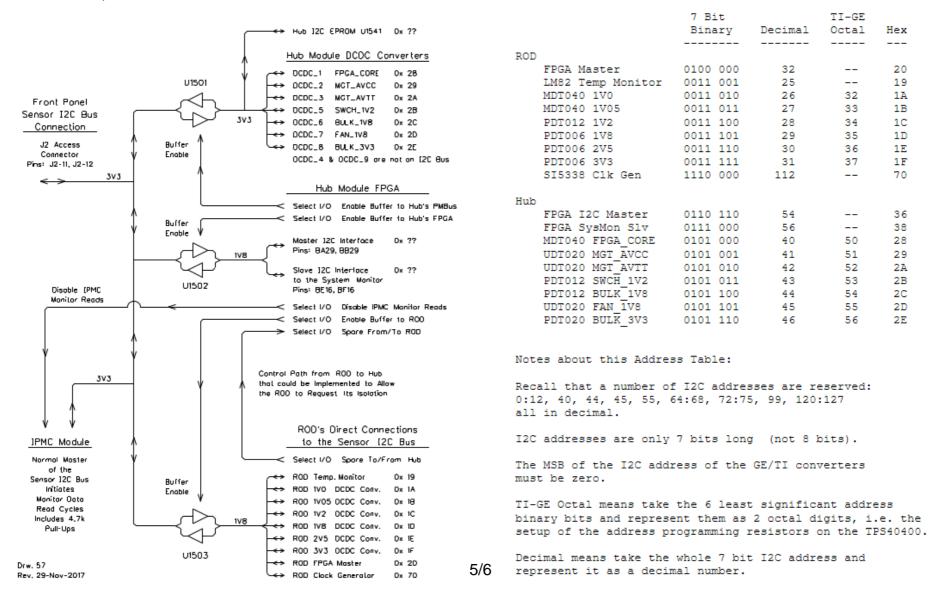

## DC/DC, SysMon, ROD – IPMC Sensor I2C bus

- Access from IPbus:

- To 7 DC/DC

- Access from IPMC:

- DC/DC, SysMon, ROD

- Buffers controlled via Ipbus

- Test front panel I2C connector

- Sensor I2C Bus

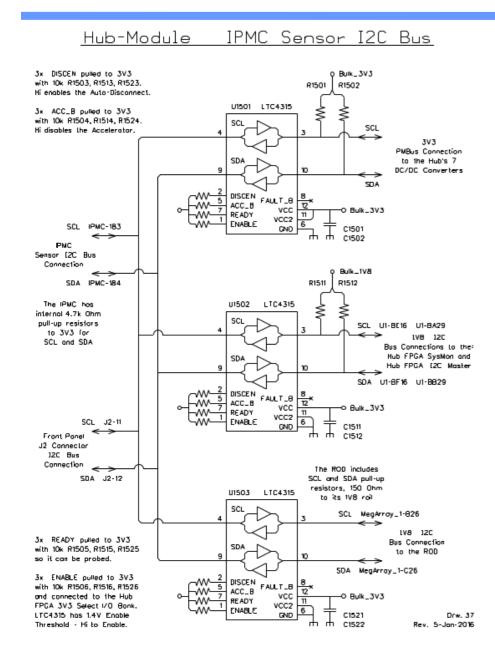

The IPMC Senor I2C Bus is used to collect monitoring data about power supply voltages and currents and device temperatures on the ROD and Hub. The IPMC will forward this hardware monitoring information over Ethernet to the Atlas DCS system. The layout of the Sensor I2C Bus is shown in drawings #37 and #57.

As shown in these drawings, three I2C bus buffer/translators are used both to drive the large number of devices on this bus, a combination of ROD and Hub devices, and also to translate between the sections of the Sensor I2C Bus that are 3V3 and the sections that are 1V8 signal level I2C bus. The buffer/translator part that is used on the Hub is the Linear Technology LTC4315. If necessary these buffer/ translators can also be used to separate the various sections of overall Sensor I2C bus under control of the Hub FPGA.

At times other devices will need to initiate and master cycles on the Sensor I2C Bus, e.g. to setup parameters in the GE DCDC power converters on both the ROD and Hub modules. A User I/O input pin on the IPMC to disable its collection sweeps of monitoring data might be useful during the short and infrequent periods when other devices need to initiate and master cycles on this bus.

### DC/DC, SysMon, ROD, IPMC - addresses

#### ROD plus Hub Overall Sensor I2C Bus

#### I2C Addresses on the Hub-ROD Sensor I2C Bus:

### HUB DCS I<sup>2</sup>C buses