# High Frequency Inversion Capacitance Measurements for 6H-SiC n-MOS Capacitors from 450 to 600 °C

Ruby N. Ghosh<sup>1,a</sup>, Reza Loloee<sup>1</sup>, Tamara Isaacs-Smith<sup>2</sup> and John R. Williams<sup>2,b</sup>

<sup>1</sup>Dept. of Physics, Michigan State University, East Lansing, MI 48824, USA

<sup>2</sup>Dept. of Physics, Auburn University, Auburn, AL 36849, USA

<sup>a</sup>ghosh@pa.msu.edu, <sup>b</sup>williams@physics.auburn.edu

**Keywords**: bulk carrier generation, inversion capacitance, high temperature, MOS capacitor

#### Abstract

The operation of metal-oxide-semiconductor (MOS) devices based on the semiconductor SiC in high temperature environments above 300 °C requires an understanding of the physical processes in these capacitor structures under operating conditions. In this study we have focused on the regime of inversion biasing, where the electrical characteristics of the device are dominated by minority carriers. We report on the direct observation of the high frequency inversion capacitance due to thermal generation of holes in 6H-SiC n-MOS capacitors between 450 and 600 °C by monitoring the 1MHz C-V characteristics of large area, 1000  $\mu$ m diameter, capacitors in the dark. Our experimental results are consistent with a first order calculation based on the delta depletion approximation.

#### Introduction

SiC based field-effect structures show great promise for electronic and sensing applications at elevated temperatures. Device design requires an understanding of the physical processes in these capacitor structures at the operating temperature. In this study we have focused on the regime of inversion biasing, where the electrical characteristics of the capacitor are dominated by minority carriers. Due to the large bandgap of SiC (3.00 eV for 6H-SiC), minority carrier generation/recombination rates are rather sluggish, which in turn means that the time constant for the semiconductor to reach equilibrium can be quite long. The physics of inversion layers in 6H-SiC has been studied up to ~400 °C using high frequency capacitance-voltage (C-V) techniques, transient capacitance measurements and the Hall effect [1,2,3,4,5]. In 4H-SiC inversion capacitance in both n-MOS and p-MOS devices have been observed via capacitance-transient techniques [6].

We report on the direct observation of the high frequency inversion capacitance due to thermal generation of holes in 6H-SiC n-MOS capacitors between 450 and 600 °C. In order to ensure that the minority carriers were thermally generated we measured the 1MHz C-V characteristics of large area, 1000  $\mu$ m diameter, capacitors in the complete absence of light.

#### Experimental

The n-MOS capacitors were fabricated on  $1 \text{ cm}^2$  6H-SiC (0001) Si face substrates with a 5.1 µm, 9.44 x  $10^{15}$  N/cm<sup>3</sup> epitaxial layer grown on an n+ wafer. The gate oxide was grown by dry oxidation at 1150 °C for 6 hours at 1 atm in a 500 sccm dry O<sub>2</sub> gas stream. This was immediately followed by a 30 min 1150 °C Ar anneal and a 2 hour 1175°C post oxidation NO passivation anneal in pure NO (577 sccm) at 1 atm. The oxide thickness as determined by spectroscopic ellipsometry is 46.1 nm. The gate metal is 100 nm of Pt sputtered at 350 °C in a 2.5 mTorr Ar atmosphere.

The SiC chip has an array of 52 gates with nominal diameters ranging from 200 to 1000  $\mu$ m, all the data in this report are from a single 1065 ± 5  $\mu$ m device. A large area back contact provides a common ground plane.

The SiC sample was mounted on a thermally conducting alumina header with three backside platinum microheaters (Heraeus) to locally heat the  $1 \text{cm}^2$  SiC sample to 630 °C. The temperature of the Pt gate was determined by monitoring the resistance of the backside heater. We estimate that our uncertainty is +5/-10 °C after accounting for the measured thermal impedance between heater and Pt gate. The alumina header provided the necessary electrical insulation from the heater current for precision 1MHz C-V measurements (Keithley Model 590). At 630 °C our noise is  $\pm 2\text{pF}$ . All measurements were made in the dark, inside a light tight enclosure.

#### **Results and Discussion**

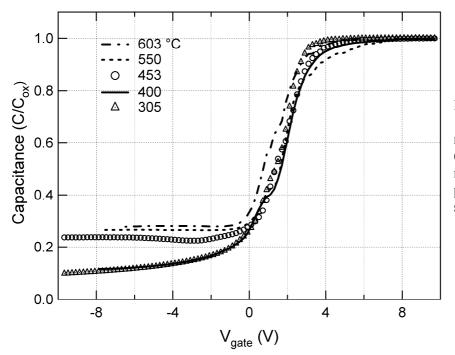

Shown in Fig. 1 are the high frequency (1MHz) C-V characteristics of a 1065  $\mu$ m diameter n-type capacitor in the *dark*, at various temperatures between 300 – 600 °C, normalized with respect to the oxide capacitance C<sub>ox</sub>. Following a 10 s hold in accumulation, the curves were swept from positive to negative bias at 0.40 V/s. At all temperatures we obtain a well defined C-V characteristic in accumulation. Note that the measurements were made without using optical illumination to generate minority carriers.

From standard MOS capacitor analysis there are two limiting cases we expect to encounter as the device is ramped from depletion to inversion bias, where a large number of minority carriers (holes) are needed to establish an equilibrium charge distribution within the MOS capacitor. As the measurements are performed in the dark, any minority carriers must be created by generation processes within the SiC epi-layer near the SiC/oxide interface. Case 1: if the temperature is high enough and the ramp rate is slow enough, the semiconductor will reach equilibrium due to thermally generated minority carriers and an inversion capacitance that is the sum of the oxide and semiconductor capacitances will be measured. Case 2: if the temperature is too low for thermal generation of minority carriers the semiconductor will be driven into non-equilibrium or deep depletion conditions. At 603, 550 and 453 °C the capacitance under inversion bias is a constant independent of voltage for  $V_{gate} < -1.1$  V as shown in Table 1. At 305 °C the semiconductor is driven into deep depletion. For the 400 °C curve the MOS capacitor is in some intermediate state under inversion bias, based on  $1/C^2$  analysis to be presented in the next section.

Fig. 1, 1MHz C-V curves of a 1065  $\mu$ m diameter 6H-SiC n-MOS capacitor from 305 to 603 °C. Measurements were made in the dark from positive to negative bias at a sweep rate of 0.40 V/s.

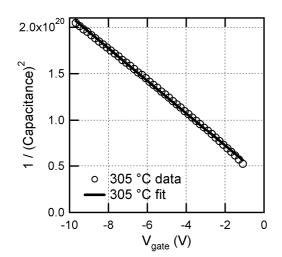

Fig. 2,  $1/C^2$  analysis at 305 °C, a least squares fit gives a slope that agrees with the nominal doping density reported by the crystal grower.

The effective majority carrier density in the SiC epi-layer was determined to be  $(10.2 \pm 0.5) \times 10^{15}$ /cm<sup>3</sup> at 305 °C via 1/C<sup>2</sup> analysis [7], from Fig. 2. This is consistent with the donor doping density of 9.44 x 10<sup>15</sup> N/cm<sup>3</sup> reported by the crystal grower. Note that at 400 °C, 1/C<sup>2</sup> analysis does not yield a good linear fit in inversion, leading us to speculate that at this temperature the device is in some intermediate state between Case 1 and Case 2.

The inversion capacitance at high temperature was calculated using the delta depletion approximation, which assumes that the free carrier distribution in the transition region between the depletion region and the neutral bulk can be approximated by a step function [7]. In addition we assumed that the minority carrier (hole) density at high temperature (>453 °C) is independent of temperature and can be approximated by the measured effective majority (electron) carrier concentration at 305 °C. The resultant inversion capacitances, normalized with respect to C<sub>ox</sub>, are given in Table 1. Also in Table 1 are the experimental values obtained from the inversion region of the measured C-V curves,  $V_g < -1.1V$  in Fig. 1; again normalized with respect to C<sub>ox</sub>. As expected from theory the measured inversion capacitance decreases with temperature from 603 to 453 °C. The experimental numbers agree with the calculated values within the level of approximation of our model. We speculate that at the higher temperatures of 603 and 550 °C, the measured capacitance is larger than that predicted by our model because the number of minority carriers in the semiconductor is actually larger than the number of majority carriers measured at 305 °C, due to the negative temperature dependence of the bandgap.

| Temperature<br>(°C) | C <sub>inversion</sub> /C <sub>ox</sub><br>(experiment) | C <sub>inversion</sub> /C <sub>ox</sub><br>(model) |

|---------------------|---------------------------------------------------------|----------------------------------------------------|

| 603                 | $0.279 \pm 0.002$ [-6.5 < V <sub>g</sub> (V)< -1.1]     | 0.241                                              |

| 550                 | $0.266 \pm 0.002$ [-7.5 < V <sub>g</sub> (V)< -1.1]     | 0.232                                              |

| 453                 | $0.235 \pm 0.010$ [-9.7 <v<sub>g(V)&lt; -1.1]</v<sub>   | 0.219                                              |

Table 1: High temperature inversion capacitance

High temperature inversion capacitance: (i) experimental data from Fig. 1 with the range of gate bias and (ii) results from model.

## Conclusions

We have experimentally observed the high frequency inversion capacitance, due to thermal generation of minority carriers, in an n-MOS 6H-SiC capacitor between 600 and 453 °C. The data was obtained from C-V measurements performed in the dark. At high temperature, > 453 °C, the measured inversion capacitance increases with increasing temperature. This is consistent with a first order calculation using the delta depletion approximation.

## Acknowledgements

The authors acknowledge the contributions of Nate Verhanovitz, Michigan State University. The devices were fabricated in the W. M. Keck Microfabrication Facility at Michigan State University. This article was prepared with the support of the U.S. Department of Energy (DOE), under Award No. DE-FC26-03NT41847. However, any opinions, findings, conclusions, or recommendations expressed herein are those of the authors and do not necessarily reflect the view of the DOE.

## References

- [1] J. Cooper, Phys. Stat. Sol (a), 162 (1997), p 305.

- [2] P. Neudeck, S. Kang, J. Petit and M. Tabib-Azar, J. Appl. Phys. 75 (1994), p 7949.

- [3] J. Sanders, J. Pan, W. Xie, S. Sheppard, M. Mathur, J. Cooper and M. Melloch, IEEE Tran. Elec. Dev., 40 (1993), p 2130.

- [4] Cheong, S. Dimitrijev and J. Han, Mat. Sci. Forum, 457-460 (2004), p 1365.

- [5] N. Saks, S. Mani, A. Agarwal and V. Hedge, Mat. Sci. Forum, 338-342 (2000),p 737.

- [6] K. Y. Cheong, S. Dimitrijev and J. Han, IEEE Trans. Elec. Dev., 51 (2004), p 1361.

- [7] Nicollian and Brews, *MOS Physics & Technology*, Wiley, New York, 383-385 and 58-67 (1982).

## Silicon Carbide and Related Materials 2007

10.4028/www.scientific.net/MSF.600-603

# High Frequency Inversion Capacitance Measurements for 6H-SiC n-MOS Capacitors from 450 to 600 °C

10.4028/www.scientific.net/MSF.600-603.739

## **DOI References**

[2] P. Neudeck, S. Kang, J. Petit and M. Tabib-Azar, J. Appl. Phys. 75 (1994), p 7949. doi:10.1063/1.356583

[3] J. Sanders, J. Pan, W. Xie, S. Sheppard, M. Mathur, J. Cooper and M. Melloch, IEEE Tran. lec. Dev., 40 (1993), p 2130.doi:10.1109/16.239812

[4] Cheong, S. Dimitrijev and J. Han, Mat. Sci. Forum, 457-460 (2004), p 1365. doi:10.4028/www.scientific.net/MSF.457-460.1365

[5] N. Saks, S. Mani, A. Agarwal and V. Hedge, Mat. Sci. Forum, 338-342 (2000),p 737. doi:10.4028/www.scientific.net/MSF.338-342.737

[6] K. Y. Cheong, S. Dimitrijev and J. Han, IEEE Trans. Elec. Dev., 51 (2004), p 1361. doi:10.1109/TED.2004.833966