|

CMX

CMX firmware code in-line documentation

|

|

CMX

CMX firmware code in-line documentation

|

Entities | |

| Behavioral | architecture |

Libraries | |

| IEEE | |

| UNISIM | |

Use Clauses | |

| IEEE.STD_LOGIC_1164.all | |

| IEEE.NUMERIC_STD.all | |

| UNISIM.VComponents.all | |

| work.CMX_VME_defs.all | |

| WORK.CMXpackage.all | |

Ports | |

| DATA24 | in arr_word ( numactchan - 1 downto 0 ) |

| CLKPAR | in std_logic_vector ( numactchan - 1 downto 0 ) |

| REF_CLK_200 | in std_logic |

| REF_CLK_READY | in std_logic |

| CLK_40 | in std_logic |

| del_register | in del_register_type |

| upload_delays | in std_logic |

| IDELAYCTRL_RDY | out std_logic_vector ( num_IDELAYCTRL - 1 downto 0 ) |

| DELAYED_DATA24 | out arr_word ( numactchan - 1 downto 0 ) |

| DELAYED_CLKPAR | out std_logic_vector ( numactchan - 1 downto 0 ) |

| ncs | in std_logic |

| rd_nwr | in std_logic |

| ds | in std_logic |

| addr_vme | in std_logic_vector ( 15 downto 0 ) |

| data_vme_in | in std_logic_vector ( 15 downto 0 ) |

| data_vme_out | out std_logic_vector ( 15 downto 0 ) |

| bus_drive | out std_logic |

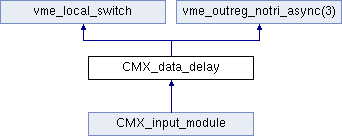

Definition at line 25 of file CMX_data_delay.vhd.

|

Port |

Definition at line 48 of file CMX_data_delay.vhd.

|

Port |

Definition at line 51 of file CMX_data_delay.vhd.

|

Port |

Definition at line 31 of file CMX_data_delay.vhd.

|

Port |

Definition at line 28 of file CMX_data_delay.vhd.

|

Port |

Definition at line 27 of file CMX_data_delay.vhd.

|

Port |

Definition at line 49 of file CMX_data_delay.vhd.

|

Port |

Definition at line 50 of file CMX_data_delay.vhd.

|

Port |

Definition at line 32 of file CMX_data_delay.vhd.

|

Port |

Definition at line 42 of file CMX_data_delay.vhd.

|

Port |

Definition at line 41 of file CMX_data_delay.vhd.

|

Port |

Definition at line 47 of file CMX_data_delay.vhd.

|

Port |

Definition at line 40 of file CMX_data_delay.vhd.

|

Library |

Definition at line 11 of file CMX_data_delay.vhd.

|

Package |

Definition at line 13 of file CMX_data_delay.vhd.

|

Package |

Definition at line 12 of file CMX_data_delay.vhd.

|

Port |

Definition at line 45 of file CMX_data_delay.vhd.

|

Port |

Definition at line 46 of file CMX_data_delay.vhd.

|

Port |

Definition at line 29 of file CMX_data_delay.vhd.

|

Port |

Definition at line 30 of file CMX_data_delay.vhd.

|

Library |

Definition at line 18 of file CMX_data_delay.vhd.

|

Package |

Definition at line 19 of file CMX_data_delay.vhd.

|

Port |

Definition at line 35 of file CMX_data_delay.vhd.

|

Package |

Definition at line 21 of file CMX_data_delay.vhd.

|

Package |

Definition at line 23 of file CMX_data_delay.vhd.